Многоразрядные сумматоры

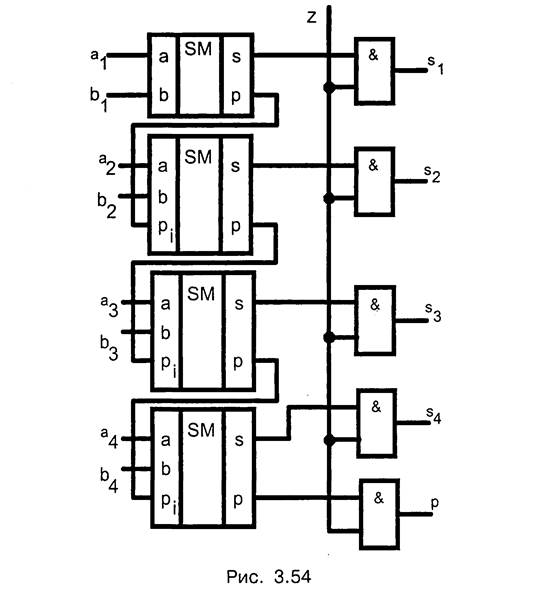

Сумматор параллельного действия содержит одноразрядные сумматоры, число которых равно разрядности суммируемых двоичных слов (рис. 3.54).

Разряды двоичных слов поступают на соответствующие одноразрядные сумматоры. Каждый одноразрядный сумматор формирует выходы суммы S1-S4 и выходы переноса Р. Перенос передается на вход следующего одноразрядного сумматора более старшего разряда. По цепям переноса сумматоры соединены последовательно. Импульс переноса в каждом сумматоре формируется после того, как будет сформирован и поступит на сумматор перенос из предыдущего разряда. Поэтому быстродействие такого параллельного сумматора с последовательным переносом невысокое. В наихудшем случае перенос может последовательно пройти все сумматоры.

Общая задержка сигнала

где  — задержка распространения в одном сумматоре.

— задержка распространения в одном сумматоре.

Повышение быстродействия достигается несколькими направлениями.

1. Повышение быстродействия элементов, используемых в цепях переноса.

2. Уменьшение числа нагрузок на выходы переноса Р. В этом случае снижается суммарная емкость нагрузки, что ведет к повышению быстродействия.

3. Уменьшение числа элементов в цепях переноса. Этот принцип реализуется путем использования элементов типа И-ИЛИ, И-ИЛ И-НЕ.

4. Формирование переносов в параллельной форме одновременно для всех сумматоров.

5. Использование отдельных комбинационных схем для формирования импульсов переноса независимо от одноразрядных сумматоров, например, с использованием формул типа (3.41) — (3.42). Также разрабатывают сумматоры, в комбинационных схемах ускоренного переноса которых формируются дополнительные величины, используемые для формирования сигнала переноса.

В результате задержки сигналов в логических элементах и неодновременного прихода сигналов на входы а, b, р сумматоров (задержка переноса) выходной код суммы может принимать в течение коротких интервалов времени ложные значения, не соответствующие входным суммируемым кодам.

Для того, чтобы избежать неопределенных состояний, применяют синхронизирование или стробирование выходных сигналов. В схеме рис. 3.54, а для этой цели используются логические элементы И. На один вход ЛЭ И поступают сигналы с выходов одноразрядных сумматоров, а на другой вход подается сигнал Z, который определяет момент выдачи результата суммы. При Z = 0 на выходах всех элементов И устанавливается логический 0. При Z = 1 выход схем И определяется выходами одноразрядных полусумматоров и равен им.

В параллельных сумматорах с параллельным переносом повышение быстродействия сумматоров достигается путем существенного усложнения схемы. Компромиссным является построение сумматоров с групповой структурой. В таких сумматорах одноразрядные сумматоры разбиваются на группы с условием

п = ml,

где п — число разрядов сумматора;

т — число одноразрядных сумматоров в группе;

l— число групп.

Внутри группы и между группами осуществляются различные виды переноса.

В качестве примера на рис. 3.50 показана микросхема К555ИМ6 — четырехразрядный двоичный полный сумматор с ускоренным переносом на основе схем И-ИЛИ-НЕ. Выполняет операцию сложения двух четырехразрядных чисел в двоичном коде с учетом переноса из младшего разряда и выдает сумму этих чисел и перенос в старший разряд.

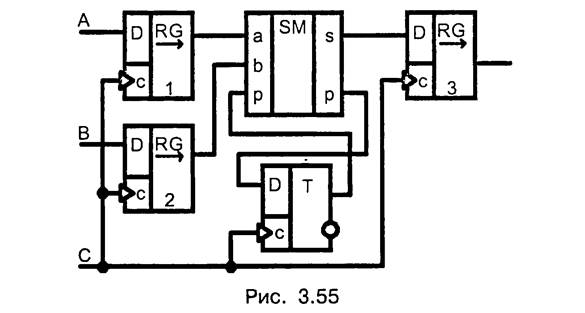

Сумматор последовательного действия содержит один одноразрядный сумматор, D-триггер и три сдвиговых регистра (рис. 3.55). Два сдвиговых регистра используются для хранения слагаемых, а в третий записывается результат суммирования. Регистры обычно выполняются отдельно от сумматора и являются отдельными микросхемами.

Под действием каждого синхроимпульса на входы а, b одноразрядного сумматора поступают разряды кодовых слов, начиная с младшего. На вход р подается сигнал переноса с выхода D-триггера. Результаты суммирования в последовательной форме записываются в третий регистр, новый сигнал переноса записывается в D-триггер по приходу следующего синхроимпульса.

Для выполнения суммирования на тактовый вход необходимо подать п синхронизирующих импульсов по числу разрядов суммируемых двоичных чисел. После каждого синхроимпульса выполняется счет одного разряда и формирование переноса в следующий разряд.

Достоинство последовательных сумматоров — малые аппаратурные затраты, с другой стороны приводит к снижению быстродействия сумматора.

Дата добавления: 2015-11-06; просмотров: 4922;