Одноразрядный полусумматор

Сумматоры

Сумматоры выполняют арифметическую операцию сложения двух чисел.

Они имеют как самостоятельное значение, так и являются составной частью арифметическо-логического устройства (АЛУ). При организации различных вычислительных процессов суммированию отводится главная роль, оно является основной операцией. Например, вычитание — это суммирование с использованием дополнительного либо обратного кода, умножение сводится к сдвигу и сложению (суммированию) двоичных чисел. Следует отметить, что сумматоры являются логическими устройствами, функционируют по законам алгебры логики, но выполняют операцию арифметического, а не логического сложения.

В соответствии с определением, сумматор суммирует два числа. Выходной сигнал зависит только от двух входных сигналов, действующих на входе в текущий момент. Следовательно, сумматор является комбинационным устройством. Однако, некоторые сумматоры, например, накапливающий сумматор и другие, содержат в своем составе элементы памяти.

По числу выводов различают: полусумматоры, одноразрядные сумматоры, многоразрядные сумматоры.

Полусумматор имеет два входа и два выхода, предназначен для сложения двух одноразрядных слов и формирует на своих выходах сигнал суммы и сигнал переноса в старший разряд.

Одноразрядный сумматор имеет три входа и два выхода, предназначен для сложения двух одноразрядных слов и формирует сигнал выхода и сигнал переноса в старший разряд из входных слов и сигнала переноса из младшего разряда.

Многоразрядный сумматор предназначен для сложения многоразрядных слов.

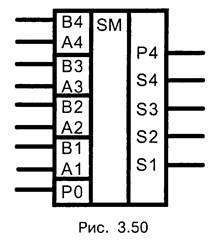

В настоящее время выпускают микросхемы одно-, двух- и четырехразрядные сумматоры. Маркировку микросхем — сумматоров можно определить по буквам ИМ — функциональное назначение, например, К555ИМ6 — четырехразрядный полный двоичный сумматор. На принципиальных схемах сумматоры обозначают буквами SM (рис. 3.50).

В зависимости от способа обработки чисел сумматоры разделяются на сумматоры последовательного и параллельного типов. Сложение чисел в последовательных сумматорах осуществляется поразрядно, последовательно во времени.

В сумматорах параллельного действия сложение всех разрядов многоразрядных чисел происходит одновременно.

По способу тактирования различают синхронные и асинхронные сумматоры. В синхронных сумматорах операция сложения осуществляется по тактовым импульсам, и время ее проведения не зависит от длины разрядов кодов, остается постоянным. В асинхронных сумматорах время выполнения операции зависит от длины входных кодов и поэтому необходимо формировать признак окончания операции.

В зависимости от используемой системы счисления различают двоичные, двоично-десятичные и другие типы сумматоров.

В виду особой важности сумматоров разработано большое количество разнообразных схем на основе различных алгоритмов синтеза. Рассмотрим наиболее характерные схемы построения сумматоров.

Одноразрядный полусумматор

В сумматорах операция суммирования чисел, представленных в двоичном коде, осуществляется поразрядно.

Простейший случай — это суммирование двух одноразрядных слов. В десятичной системе

0 + 0 = 0; 0 + 1 = 1; 1 + 0 = 1; 1 + 1 = 2; (3.35) что соответствует в двоичной системе счисления

0 + 0 = 0; 0 + 1 = 1; 1+ 0 = 1; 1 + 1 = 10. (3.36)

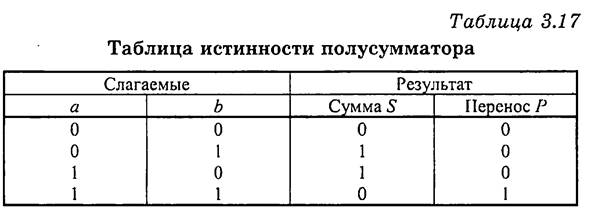

В последнем случае результат суммы оказался двухразрядным 102= 210. Обычное явление, когда при суммировании двух чисел в любой системе счисления результат имеет на один разряд больше. В двоичной системе единица в старшем разряде суммы называется единицей переноса. Сведем формулы (3.36) в таблицу.

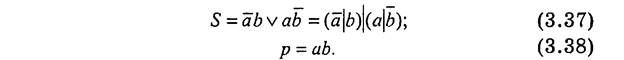

Из таблицы 3.17 получим аналитические выражения для суммы S и переноса Р

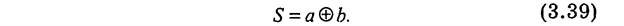

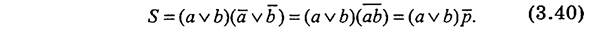

Выражение для S можно записать с помощью известной операции ИСКЛЮЧАЮЩЕЕ-ИЛИ

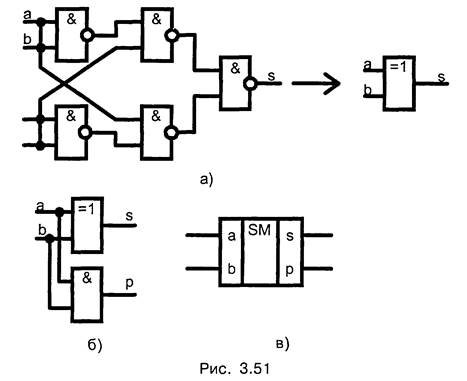

Техническая реализация полусумматора на основе (3.37) — (3.39) представлена на рис. 3.51.

Используя представление в базисе ИЛИ-НЕ, из таблицы 3.17 получим

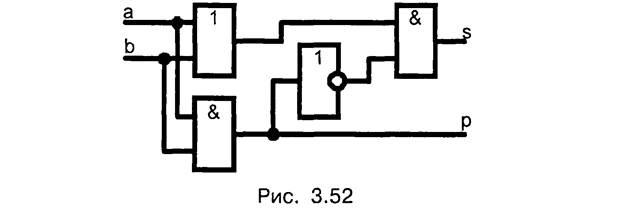

На основе формулы (3.40) построим схему полусумматора, содержащего меньшее число логических элементов (рис. 3.52)

В то же время схема (рис. 3.52) содержит различные элементы: И, НЕ, ИЛИ.

Полусумматор (рис. 3.51; 3.52) не имеет входа переноса с предыдущего разряда, поэтому его можно использовать только в младших разрядах устройства обработки многоразрядных двоичных слов.

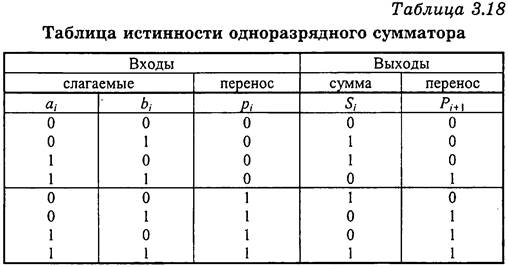

Составим таблицу истинности сложения одного разряда многоразрядного двоичного слова с учетом переноса из младшего разряда (таблица 3.18).

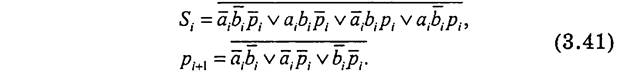

Пользуясь таблицей истинности 3.18 в базисе И-ИЛИ-НЕ получаем выражения для

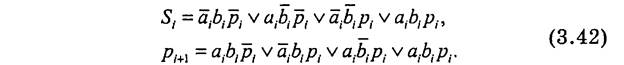

С другой стороны, составляем совершенную дизъюнктивную нормальную форму

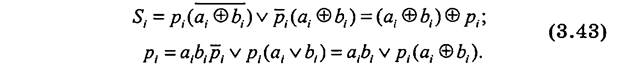

После преобразований (3.42), используя функции «равнозначность» (ИСКЛЮЧАЮЩЕЕ ИЛИ-HE), «неравнозначность» (ИСКЛЮЧАЮЩЕЕ ИЛИ), получим

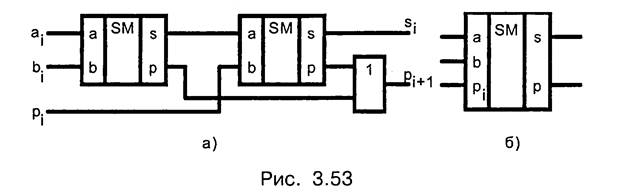

Полный одноразрядный сумматор в соответствии с (3.43) построим из двух полусумматоров (рис. 3.53)

Полные одноразрядные сумматоры являются основой, из которых получают различные схемы многоразрядных сумматоров.

Дата добавления: 2015-11-06; просмотров: 8819;