Структура адресации.

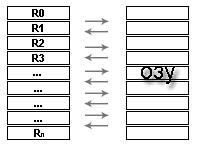

90% работы процессора связано с оперативной памятью. Он берет оттуда данные, обрабатывает их и отсылает обратно в память. Кроме этого, сам процессор имеет собственную память, называемую регистрами. Графически это можно изобразить так:

где слева регистры процессора R1, R2 … Rn, а справа ячейки памяти. Зачем нужны регистры? В процессор поступает некоторое количество данных (несколько операндов), и с ними необходимо провести некоторые действия. Поступили эти операнды из оперативной памяти, и процессор по команде начал с ними работать. Поскольку действий над ними несколько, то работа разбивается на несколько этапов и результат каждого необходимо запомнить. Самый простой способ - сохранить в ячейках оперативной памяти, но на передачу и запись этих данных в память уйдет время, так как память работает значительно медленнее процессора. К тому же речь идет о промежуточных результатах, которые необходимо будет еще много раз использовать, поэтому будут большие временные потери. Поэтому используются регистры внутри процессора, которые работают значительно быстрее, по сути дела на тактовой частоте процессора. К тому же адресация к ним происходит быстрее.

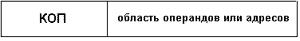

Но для начала определимся с форматом команды. Под форматом команды понимают совокупность размера всех полей и их расположения в команде. Представим себе упрощенный вид команды:

Команда делится на две области: область кода операции и область адресов. Вначале идет код операции (КОП) который говорит, что вообще необходимо делать, а затем идет адрес операнда/операндов с которым/которыми это надо делать. Адресная область может состоять из нескольких частей – это, так называемые многоадресные команды. С точки зрения программиста, наиболее удобны трехадресные (ранее были распространены четырехадресные, которые уже практически не применяются).

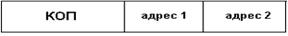

Адресная область состоит из трех полей: в первых двух лежат адреса операндов, а в третье будет записан адрес результата действия над операндами.

В двухадресных командах адресная область состоит из двух полей: поле адреса первого операнда и поле адреса второго операнда. Адрес результата действия над операндами будет записан в первое поле.

В одноадресных командах адресная область состоит из одного единственного поля, в котором лежит адрес операнда, а адрес второго операнда и результата совпадает с сумматором. Существуют так же и безадресные команды, которые применяются при работе со стеками. Чаще всего используются двух-, одно- и безадресные команды.

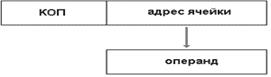

Проблема заключается в том, что операнды эти могут находиться в любом месте памяти. Об этом знает только та программа, которая, собственно, их и запрашивает. Для того, чтобы процессор нашел нужные операнды, в поле адреса операнда вкладывают … адрес операнда (то есть тот адрес, по которому, обратившись, процессор найдет операнд или, проще говоря, необходимые данные).

Адресный код - это информация об адресе операнда, содержащаяся в команде.

Исполнительный адрес - это номер ячейки памяти, к которой производится фактическое обращение.

В современных ЭВМ адресный код, как правило, не совпадает с исполнительным адресом.

Выбор способов адресации, формирования исполнительного адреса и преобразования адресов является одним из важнейших вопросов разработки ЭВМ. Рассмотрим способы адресации, используемые в современных ЭВМ :

· неявная адресация (источник и (или) приемник информации неявно заданы в команде);

· непосредственная;

· прямая (адрес операнда указывается в командном слове);

· косвенная;

· относительная, или базовая, адресации (используется регистр базового адреса);

· адресация слов переменной длины;

· стековая адресация;

· автоинкрементная и автодекрементная адресация;

· индексация;

· двойная индексация.

Неявная адресация. В команде может не содержаться явных указаний об адресе участвующего в операции операнда или адресе, по которому должен быть размещен результат операции, но этот адрес подразумевается

Непосредственная адресация (подразумеваемый операнд) – случай, когда вместо адреса операнда в команде указывается сам операнд (правда, если он представляет целое число). Выбрав из памяти код операции, процессору уже нет необходимости лезть опять в память за самим операндом, ведь он передается вместе с КОП.

Но такое не всегда бывает. Если в команде указан полный адрес ячейки, где лежат необходимые данные, то это уже полный или абсолютный тип адресации. Иногда этот тип называют прямой адресацией.

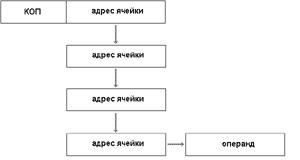

Кроме этого, в поле адреса операнда может быть указан адрес или регистра или ячейки памяти, в которой лежит то же адрес, по которому можно найти ячейку с нужным операндом.

Такой способ адресации называться косвенным. При косвенной адресации количество ячеек с адресами других ячеек может быть несколько (цепочка).

Количество звеньев (или ступеней перехода) называется глубиной косвенной адресации.

Все выше приведенные типы адресации касались одного операнда. А как же быть в случае с несколькими операндами или говоря другим языком – массивами? Тогда обычно указывается адрес массива и номер (индекс) элемента. Базовый (начальный) адрес указывается в команде. Кроме этого, там же, в команде, есть поле, где указан номер регистра, в котором лежит значение индекса или номер ячейки в массиве относительно начального адреса. Тогда адрес каждой ячейки массива будет получаться из суммы начального адреса и того, что содержит указанный регистр. Такой способ называется модификацией адресов.

Кроме того, существует тип адресации, когда в регистре лежит начальный адрес. В команде указан адрес этого регистра, а так же записано смещение относительно начального адреса. Все остальные адреса операндов будут получены из суммы адреса и смещения. Такой вот тип адресации называется относительным.

При относительной адресации можно еще и модифицировать адреса. В этом случае адрес будет равен сумме начального адреса плюс смещение плюс содержимое индексного регистра.

Укороченная адресация. Для уменьшения длины кода команды часто применяется так называемая укороченная адресация. Суть ее сводится к тому, что в команде задаются только младшие разряды адресов, а старшие разряды при этом подразумеваются нулевыми. Такая адресация позволяет использовать только небольшую часть фиксированных ячеек в начале всей адресуемой области памяти, и поэтому применяется лишь совместно с другими способами адресации.

Регистровая адресация является частным случаем укороченной, когда в качестве фиксированных ячеек с короткими адресами используются регистры (ячейки сверхоперативной или местной памяти) процессора. Например, если таких регистров 16, то для адреса достаточно четырех двоичных разрядов. Регистровая адресация наряду с сокращением длины адресов операндов позволяет увеличить скорость выполнения операций, так как уменьшается число обрашений к оперативной памяти

Если система использует несколько типов адресации, то в команде обязательно записывается, какой способ будет применен в данный момент, в машинной команде указывается признак адресации в поле признака операции.

Адресация слов переменной длины. Эффективность вычислительных систем, предназначенных для обработки данных, повышается, если имеется возможность выполнять операции со словами переменной длины. В этом случае в машине может быть предусмотрена адресация слов переменной длины, которая обычно реализуется путем указания в команде местоположения в памяти начала слова и его длины.

Стековая адресация,реализующая безадресное задание операндов, особенно широко используется в микропроцессорах и мини-ЭВМ.

Стекпредставляет собой группу последовательно пронумерованных регистров или ячеек памяти, снабженных указателем стека, в котором автоматически при записи и считывании устанавливается номер (адрес) последней занятой ячейки стека (вершины стека). При операции записи заносимое в стек слово помещается в следующую по порядку свободную ячейку стека, а при считывании из стека извлекается последнее поступившее в него слово.

Автоинкрементная и автодекрементная адресации. Поскольку регистровая косвенная адресация требует предварительной загрузки регистра косвенным адресом из оперативной памяти, что связано с потерей времени, такой тип адресации особенно эффективен при обработке массива данных, если имеется механизм автоматического приращения или уменьшения содержимого регистра при каждом обращении к нему. Такой механизм называется соответственно автоинкрементной и автодекрементной адресацией. В этом случае достаточно один раз загрузить в регистр адрес первого обрабатываемого элемента массива, а затем при каждом обращении к регистру в нем будет формироваться адрес следующего элемента массива.

При автоинкрементной адресации сначала содержимое регистра используется как адрес операнда, а затем получает приращение, равное числу байт в элементе массива. При автодекрементной адресации сначала содержимое указанного в команде регистра уменьшается на число байт в элементе массива, а затем используется как адрес операнда.

Автоинкрементная и автодекрементная адресации могут рассматриваться как упрощенный вариант индексации — весьма важного механизма преобразования адресных частей команд и организации вычислительных циклов, поэтому их часто называют автоиндексацией.

Индексация. Для реализуемых на ЭВМ методов решения математических задач и обработки данных характерна цикличность вычислительных процессов, когда одни и те же процедуры выполняются над различными операндами, упорядоченно расположенными в памяти. Поскольку операнды, обрабатываемые при повторениях цикла, имеют разные адреса, без использования индексации требовалось бы для каждого повторения составлять свою последовательность команд, отличающихся адресными частями.

Программирование циклов существенно упрощается, если после каждого выполнения цикла обеспечено автоматическое изменение в соответствующих командах их адресных частей согласно расположению в памяти обрабатываемых операндов. Такой процесс называется модификацией команд, и основан на возможности выполнения над кодами команд арифметических и логических операций.

Управление вычислительным циклом должно обеспечивать повторение цикла нужное число раз, а затем выход из него.

Автоматическая модификация команд и управление вычислительными циклами в современных ЭВМ обеспечиваются механизмом индексации. Это понятие включает в себя специальный способ кодирования команд, командные и аппаратурные средства задания и выполнения модификации команд и управления вычислительными циклами. Упомянутые средства часто называют индексной арифметикой.

Для выполнения индексации в машину вводятся так называемые индексные регистры. Исполнительный адрес при индексации формируется путем сложения адресного кода команды (смещения) с содержимым индексного регистра (индексом), а при наличии базирования - и с базовым адресом.

Для управления индексацией используются команды, задающие операции над содержимым индексных регистров - команды индексной арифметики. Можно отметить основные виды индексных операций:

- засылка в соответствующий индексный регистр начального значения индекса;

- изменение индекса;

- проверка окончания циклических вычислений.

Иногда применяется аппаратура, поддерживающая сегментную двумерную адресацию, в условиях которой программы представляют собой систему логических сегментов, связанных друг с другом в процессе выполнения с помощью ссылок. Есть машины, образующие из блоков, содержащих последовательные адресные участки, рамочные структуры. В таких машинах любой блок может динамически связываться с различными физическими адресами, не требуя изменения адресации непосредственно в программах. Каждый из перечисленных механизмов предполагает свою стратегию управления памятью со стороны ОС.

Структура прерываний. Прерывания представляют собой механизм, позволяющий координировать параллельное функционирование отдельных устройств вычислительной системы и реагировать на особые состояния, возникающие при работе процессора.

Прерывания – это принудительная передача управления от выполняющейся программы к операционной системе, а через неё к соответствующей программе обработки прерываний, происходящая при определенном событии. Основная цель введения прерываний – реализация асинхронного режима работы и распараллеливания работы отдельных устройств вычислительного комплекса. Механизм прерываний реализуется аппаратно-программными средствами.

Структуры систем прерываний могут быть самыми различными, но все они имеют общую особенность – прерывание непременно ведет за собой изменение порядка выполнения команд процессором. Механизм обработки прерываний включает в себя следующие элементы:

1. Установление факта прерывания (прием и идентификация сигнала на прерывание).

2. Запоминание состояния прерванного процесса (состояние процесса определяется значением счетчика команд, содержимым регистра процессора, спецификацией режима: пользовательский или привилегированный)

3. Управление аппаратно передается программе обработки прерывания. В этом случае, в счетчик команд заносится начальный адрес подпрограммы обработки прерывания, а в соответствующие регистры из слова состояния.???

4. Сохранение информации прерванной программе, которую не удалось спасти с помощью действий аппаратуры.

5. Обработка прерывания. Работа может быть выполнена той же подпрограммой, которой было передано управление на 3-ем шаге, но в ОС чаще всего эта обработка реализуется путем вызова соотв. подпрограммы.

6. восстановление информации относящейся к прерванному процессу.

7. Возврат в прерванную программу.

Первые 3 шага реализуются аппаратными средствами, а остальные – программно.

Главные функции механизма прерывания:

- распознавание или классификация прерывания;

- передача управления обработчику прерывания;

- корректное возвращение к прерванной программе

Переход от прерванной программе к обработчику и обратно должен производится как можно быстрее. Одним из быстрых методов является использование таблицы, содержащей перечень всех допустимых для компьютера прерываний и адреса соответствующих обработчиков. Для корректного возвращения к прерванной программе, перед передачей управления обработчику, содержимое регистров процессора запоминается либо в памяти с прямым доступом либо в системном стеке.

Обслуживание прерываний. Наличие сигнала прерывания не обязательно должно вызывать прерывание исполняющейся программы, процессор может обладать системой защиты от прерываний: отключение системы прерываний либо запрет или маскирование отдельных сигналов прерываний. Программное управление этими средствами позволяет ОС регулировать обработку сигналов прерывания. Процессор может обрабатывать прерывания сразу по приходу прерывания, откладывать их обработку на некоторое время, полностью игнорировать. Обычно операции прерывания выполняются только после завершения выполнения текущей команды. Поскольку сигналы прерывания возникают в произвольные моменты времени, то на момент прерывания может существовать несколько сигналов прерывания, которые могут быть обработаны только последовательно. Чтобы обработать сигналы прерывания в разумном порядке им присваиваются приоритеты. Программы управляя специальными регистрами маски, позволяют реализовать различные дисциплины обслуживания:

с относительным приоритетом. При этом обслуживание не прерывается даже при наличии запросов с более высокими приоритетами. после окончания обслуживания данного запроса (текущего) обслуживается запрос с наивысшим приоритетом. для организации такой дисциплины необходимо в программе обслуживания данного запроса наложить маски на все остальные прерывания или просто отключить систему прерываний.

с абсолютным приоритетом. Всегда обслуживаются задачи с наивысшим приоритетом. Для реализации этой дисциплины при запросе на обработку прерываний маскируются все прерывания с низшим приоритетом. При этом возможно многоуровневое прерывание, т. е. прерывание программы обработки прерывания. Число уровней прерывания в этом режиме изменяется и зависит от приоритета запроса по принципу стека: LCFS – last come first served, т . е. запрос с более высоким приоритетом может прервать запрос с более низким приоритетом. При появлении запроса на прерывание система прерываний идентифицирует сигнал и если прерывания разрешены, то управление передается на соотв. программу обработки прерываний.

Служебные секции, в которых осуществляется сохранение контекста прерванной задачи и последняя секция, в которой осуществляется восстановление контекста, не могут быть прерваны. Поэтому на время выполнения центральной секции обработки прерываний прерывания разрешены, на время работы заключительной секции подпрограмма обработки прерываний должна быть отключена, а после восстановления контекста прерванной задачи включена вновь. Эти действия нужно выполнять в каждой обработке прерываний.

Во многих ОС 1 секция обработки прерываний выделяется в специальный программный модуль наз. супервизором прерываний.

Вектор состояния (state vector) отражает состояние программы, выполняющейся процессором. Он служит для определения той информации, которая должна быть помещена в регистр процессора и отдельные ячейки памяти в момент прерывания для обеспечения возможности возобновления приостановленной программы.

Типы прерываний :

· от схем контроля процессора;

· из-за ошибки адресации;

· от нарушения питания;

· от устройств ввода-вывода;

· программное прерывание.

Прерывания связаны между собой системой приоритетов (какое прерывание надо обрабатывать в первую очередь при возникновении нескольких прерываний одновременно). Общая схема обработки прерываний представлена на рис.2.1.

Применяется так называемая система масок прерываний, разрешения (запрещения) обработки прерываний.

Система команд - влияет на структуры и функциональные характеристики механизмов ввода-вывода, на способы реализации системных функций.

Вся система команд может делиться на две группы: привилегированные команды и непривилегированные. Привилегированные команды могут выполняться в режиме управления, а непривилегированные - в режиме задачи. Переход в режим управления в некоторых системах выполняется автоматически, при прерывании, в других системах прерывание может вызвать, а может и не вызвать переход в этот режим.

Переход из режима задачи в режим управления обычно осуществляется в результате выполнения специальной команды, инициирующей прерывание, например, SVC (Supervisor Call - вызов супервизора).

Механизмы защиты. Назначение механизма защиты, встроенного в процессор - запретить какой-либо программе обращения к не принадлежащему ей участку памяти. Различают следующие механизмы защиты:

а) с использованием регистров-ограничителей, куда заносится минимальное и максимальное значение адресов.

б) с использованием ключа защиты, области памяти, доступные данной программе, помечаются тем же ключом. Ключ представляет собой несколько битов информации и помещается в регистры или ячейки, не доступные программам, работающим в режиме задачи. По завершению формирования адреса ключ выполняющейся программы сравнивается с ключом адресуемой области.

в) механизм защиты совмещен с механизмом адресации (комплексный механизм с использованием ассоциативных MAP-таблиц).

Кроме выше указанных характеристик ЦП, на общую структуру ОС оказывают влияние: система микрокоманд (если она имеется); иерархия и организация памяти (наличие основной и промежуточной (кэш) памяти), а также других видов - ROM (read only memory); структура оборудования ЭВМ в целом.

Глава 4 (лекция 6)

Дата добавления: 2015-10-21; просмотров: 3241;