Регистры. Простейшие регистры

Простейшие регистры способны выполнять минимальное количество микроопераций типа параллельного приёма информации. Они могут быть построены на любых триггерах. Рассмотрим вариант реализации регистра на D-триггерах.

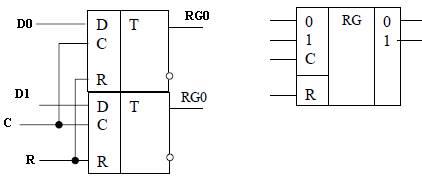

Двухразрядный регистр и его графическое изображение предложены на рисунке 4.1.

Рис. 4.1. – Схема простейшего двухразрядного регистра и его условное обозначение

Предложенный регистр строится с использованием одноступенчатых триггеров с потенциальным управлением.Если регистр или счётчик реализуется на триггерах с динамическим управлением или двухступенчатых триггерах, то вход синхронизации помечается как динамический, фронт срабатывания по которому соответствует моменту появления новой информации на выходах регистра.

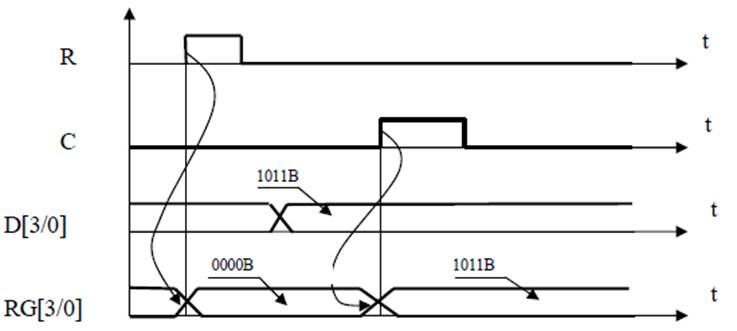

Поведение узла может быть описано временными диаграммами, на которых каждый сигнал представлен своей линией. Если узел многоразрядный, то потребуется изображение большого числа линий, что оказывается неудобным при анализе работы. В этом случае возможно групповое изображение входных и выходных информационных сигналов с указанием в шестнадцатеричной или другой системе состояния узла в текущий момент времени. На рисунке 4.2 предлагается вариант временных диаграмм четырёхразрядного регистра с информационными входами D[3/0] и выходами RG[3/0].

Рис. 4.2. – Временные диаграммы работы четырёхразрядного регистра

По сигналу сброса R регистр сбрасывается в нулевое состояние, которое в двоичной системе представлено на временных диаграммах числом 0000B. В некоторый момент времени входная информация меняет своё состояние, что выражено двоичным числом 1011B. В момент прихода активного сигнала синхронизации происходит занесение входной информации, в результате чего на выходах регистра формируется то же число 1011B.

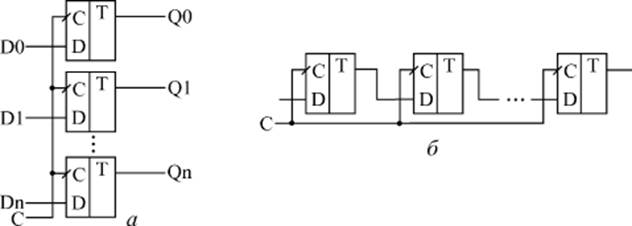

На схемах регистры обозначаются буквами RG. В отечественных сериях микросхем регистрам соответствуют буквы ИР. Все регистры делятся на две большие группы (рис. 8.1):

· Параллельные регистры;

· Регистры сдвига (или сдвиговые регистры).

Существуют регистры и других типов, но они применяются гораздо реже, чем параллельные и сдвиговые, так как имеют узкоспециальное назначение.

В параллельных регистрах рис. 8.1.-а каждый из триггеров имеет свой независимый информационный вход (D) и свой независимый информационный выход. Тактовые входы (С) всех триггеров соединены между собой. В результате параллельный регистр представляет собой многоразрядный, многовходовый триггер.

Рис. 8.1.Структура параллельного регистра (а) и сдвигового регистра (б)

В сдвиговых регистрах (б) все триггеры соединены в последовательную цепочку. Тактовые входы всех триггеров (С) объединены между собой. В результате такой триггер может рассматриваться как линия задержки, входной сигнал которой последовательно перезаписывается из триггера в триггер по фронту тактового сигнала С.Информационные входы и выходы триггеров могут быть выведены наружу, а могут и не выводиться – в зависимости от функции, выполняемой регистром.

Дата добавления: 2015-08-21; просмотров: 2778;