Базовые средства микропроцессорной техники

В настоящее время микропроцессорные средства широко применяются для обработки информации в измерительных системах. Структурный состав в каждом конкретном случае определяется требованиями измерительной системы.

В простых случаях это может быть однокристальный специализированный вычислитель, работающий по короткой неизменяемой программе.

В сложных случаях микропроцессорные средства объединяются в универсальную микро-ЭВМ, имеющую сложные аппаратные устройства и развитое программное обеспечение.

Примером может служить измерительно-вычислительная система (ИВС) на основе “Pentium”, оснащённая платой АЦП. При объёме ОЗУ в 32 мегабайт, жёстком диске до одного гигабайта и тактовой частоте 200 мегагерц, такая ИВС может удовлетворить большинству современных требований. Аналогично применяется портативная вычислительная система на основе “Notebook” с такими же вычислительными возможностями.

Для программирования задач обработки измерительной информации используется ассемблер и языки высокого уровня, например, С/C++ со всеми известными на данный момент программными наработками.

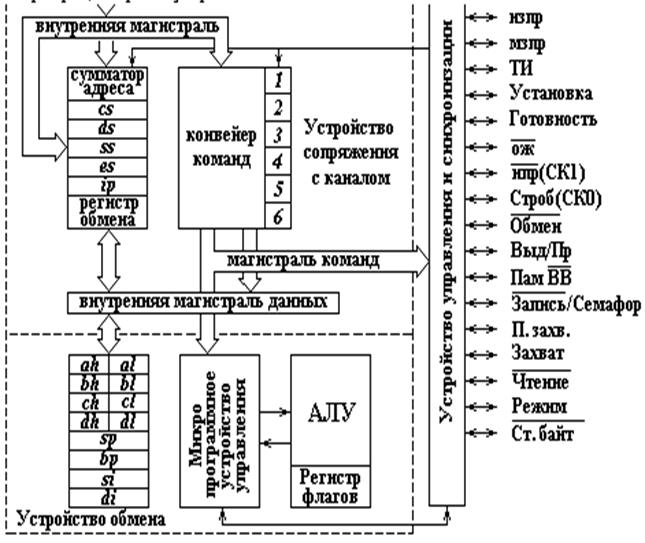

Высокая степень интеграции во всех случаях позволяет выполнять микропроцессорные средства компактными, гибкими в настройке и надёжными в эксплуатации. На рис. 13.1. приведена обобщённая структура аппаратной части микропроцессора семейства 8086…80486. Отличительная особенность архитектуры микропроцессора характеризуется рядом структурных и схемотехнических решений, среди которых, прежде всего нужно выделить следующие:

1 - микропроцессор имеет развитую регистровую структуру, что даёт возможность снизить количество обращений к памяти;

2 - использование конвейерного принципа выполнения команд с предварительной выборкой обеспечивает максимальную пропускную способность канала;

3 - распределённое аппаратно-микропрограммное устройство управления позволяет совмещать операции выборки команд с арифметико-логическими операциями;

4 - мультиплексированный канал адреса и данных с разделением по времени, а также совмещение функций многих выводов управления в зависимости от конфигурации режимов использования позволяет значительно сократить число выводов центрального процессорного элемента ЦПЭ, т.е. решить компромиссную задачу между числом функций ЦПЭ и числом выводов.

Рисунок 13.1 – Аппаратная часть микропроцессора

Рисунок 13.1 – Аппаратная часть микропроцессора

Микропроцессоры, стоящие на разных уровнях этого ряда отличаются друг от друга только разрядностью и методами технологических реализаций. В микропроцессорах этого ряда ЦПЭ разделён на два специализированных процессорных устройства: устройство обмена (УО) и устройство сопряжения с каналом (УСК). Это позволило совместить в командах следующие этапы:

1 - извлечение кодов и операторов команд из памяти;

2 - выполнение команд в операционном блоке;

3 - запись результата в регистры общего назначения или во внешнюю память микроЭВМ или выдача во внешние устройства.

Таблица 13.1 – Обозначение выводов микропроцессора

| Номер вывода | Обозначение вывода | Функциональное назначение вывода |

| 1, 20 | Земля | Общая точка питания |

| 2…16, 39 | АД0…АД15 | Канал адреса данных |

| нзпр | Немаскируемый запрос прерывания | |

| мзпр | Маскируемый запрос прерывания | |

| ТИ | Вход тактовых импульсов | |

| Установка | Установка в начальное состояние | |

| Готовность | Готовность внешних устройств для работы с ЦПЭ | |

| Ожидание | |

| чт | Чтение | |

| Режим | Однопроцессорный - вывод соединён с +Uпит. Многопроцессорный - вывод соединён с землёй. | |

| Разрешение передачи старшего байта по каналу данных (сигнал состояния). | |

| 35…38 | А19/C6, A18/C5, A17/C4, A16/C3 | Линия канала адреса/сигналы состояния |

| Uпит | Напряжение питания +5 В. | |

| Однопроцессорный режим | ||

| Подтверждение прерывания | |

| Строб | Строб адреса | |

| Обмен | Разрешение передачи данных | |

| Выдача/Приём данных | |

| Пам/Пр | Память/внешнее устройство | |

| Запись в память или ВВ | |

| П.захв. | Подтверждение захвата | |

| Захв | Захват | |

| Многопроцессорный режим | ||

| 24, 25 | СК1, СК0 | Сигналы состояния конвейера команд |

| 26, 27, 28 | С0, С1, С2 | Сигналы состояния цикла канала |

| Семафор | Канал занят | |

| 30, 31 | П.захв., Захв | Запрос сопроцессоров/разрешение доступа к магистрали |

Устройство обмена включает в себя 64, 32 (или 16 в зависимости от уровня в ряду) - разрядное арифметико-логическое устройство (АЛУ) с регистром признаков, восемь 64, 32 или 16 - разрядных регистров общего назначения (РОН) и микропрограммное устройство управления. Устройство сопряжения с каналом состоит из конвейера команд, представляющего собой очередь из шести регистров команд, регистра обмена и сумматора для вычисления адреса. Между собой УО и УСК соединены шиной данных и шиной команд. Координация и управление блоками ЦПЭ осуществляется общим блоком управления и синхронизации.

Устройство обработки предназначено для осуществления арифметико-логических операций с данными: сложения и вычитания, умножения и деления, инверсии, конъюнкции, дизъюнкции и тестирования операнда. Арифметические операции производятся с четырьмя различными типами представления чисел: двоичными числами со знаком и без знака, упакованными и неупакованными форматами чисел со знаком и без знака. Произведение и делимое представляются числами двойной длины.

Команды по запросам от УО выбираются из памяти и записываются в регистры конвейера команд УСК. Очередь команд из конвейера поступает по внутренней магистрали команд на вход микропрограммного устройства управления УО, где они декодируются, и вырабатывается последовательность микрокоманд, управляющая выполнением операций в соответствии с кодом команды. УО не имеет непосредственной связи с внешней магистралью вычислительной системы и обменивается данными посредством регистра обмена УСК.

Устройство сопряжения с каналом выполняет функции, связанные с формированием физического адреса памяти, выборку из памяти команд и операндов, формирование очереди в конвейере команд и запоминание в памяти результатов выполнения команд. После освобождения двух регистров конвейера УСК заполняет их следующими командами. Состояние конвейера команд индицируется специальными сигналами, выдаваемыми на внешние выводы СКО и СК1.

Однопроцессорный (минимальный) режим ЦПЭ обеспечивается посредством соединения вывода “Режим” с выводом +Uпит, а многопроцессорная конфигурация (максимальная) - посредством соединения этого вывода с “Землёй”. В минимальном и максимальном режимах управления внешние выводы ЦПЭ несут различные функции, отмеченные в таблице 13.1.

С точки зрения программиста микропроцессор может быть представлен следующей совокупностью адресуемых регистров (рис. 13.2). Все программно-доступные регистры микропроцессора можно разделить на три группы.

Рисунок 13.2 – Регистры микропроцессора.

К первой группе относятся регистры, предназначенные для временного хранения данных: 16-разрядный регистр - аккумулятор AX, 16-разрядный регистр базы BX, 16-разрядный регистр-счётчик CX и 16-разрядный регистр данных DX. Эти регистры допускают раздельную адресацию старших AH, BH, CH, DH и младших AL, BL, CL, DL 8-разрядных регистров. Двойственный характер этих регистров обеспечивает простую обработку 8- и 16-разрядных данных. Все эти регистры могут одинаково использоваться при арифметико-логической обработке данных. Но имеется значительное число команд, которые специализируют регистры данных, что отражено в аббревиатуре их названий. Например, регистр AX выполняет функции аккумулятора, он является источником и получателем в операциях ввода-вывода, с ним связаны операции преобразования, десятичной коррекции, умножения и деления. Регистр BX в некоторых командах участвует как регистр базового адреса.

Регистр CX используется как счётчик в операциях с цепочками байт и слов, в операциях сдвигов и командах зацикливания. Наконец, регистр косвенной адресации для указания адресов портов ввода-вывода.

DX может неявно адресоваться в операциях умножения и деления, а также используется в режиме хранения информации.

Ко второй группе относятся регистры SI и DI и указатели SP и BP, предназначенные для извлечения информации из сегментов памяти. Содержимое этих регистров задаёт смещения в сегментах при определении логических адресов. Это позволяет компактно писать программы каждый раз непосредственно, не приводя используемого адреса. Обычно в индексных регистрах записывается адресное смещение по отношению к сегменту данных, а в указателях - адресное смещение по отношению к стековому сегменту.

Несмотря на то, что регистры специализированы и каждый имеет своё мнемоническое обозначение, они могут участвовать в арифметико-логических операциях как регистры общего назначения, что придаёт гибкость при программировании

К третьей группе относятся сегментные регистры: 16-разрядный регистр начального адреса сегмента кода CS, 16-разрядный регистр начального адреса сегмента данных DS, 16-разрядный регистр начального адреса сегмента стека SS и 16-разрядный регистр начального адреса дополнительного сегмента ES.

Коды команд извлекаются из сегмента текущего кода с использованием смещения, задаваемого 16-разрядным регистром адреса команд IP, а операнды команд обычно извлекаются путём записи специального однобайтного префикса перед командой. Префикс позволяет отличать операнд от кода команды.

Микропроцессор имеет 16-разрядный регистр признаков, девять разрядов которого задействованы для флагов состояний, а остальные семь не используются, т.е. заполнены постоянными нулями или единицами. По функциональным признакам флаги состояний можно разделить на две категории: флаги, характеризующие результат, и флаги, предназначаемые для управления режимами ЦПЭ. Выполнение какой-либо операции в ЦПЭ может ставиться в зависимость от результата выполнения предыдущей операции. При этом флаги признаков результата могут быть установлены в нуль или единицу и содержать сведения об информации, обмениваемой между АЛУ и аккумулятором.

Одним из важнейших признаков является признак переноса, изображаемый флагом CF. При сложении или умножении многоразрядных чисел флаг CF показывает, нужно ли переносить единицу в младший разряд следующего байта или слова, а при вычитании или делении этот флаг показывает, нужно ли занимать единицу в следующем байте или слове.

Вычитание в микропроцессоре выполняется преобразованием отрицательных чисел в дополнительный код и последующим их сложением, поэтому функции переноса и заем одни и те же.

Разновидностью признака переноса является признак вспомогательного переноса, изображаемый флагом AF . Этот флаг участвует при работе с числами, кодированными в двоично-десятичном коде. Независимо от причин, порождающих перенос из третьего разряда в четвёртый в каждой тетради чисел, участвующих в арифметических операциях, возникновение этого переноса говорит о необходимости применения десятичной коррекции.

Признак нуля отмечает случай появления в АЛУ после выполнения какой-либо операции нулевого результата и изображается флагом ZF. Признак нуля используется для программной реализации счётчиков циклов, а также для сравнения двух чисел на равенство.

Признак знака необходим для различения положительных и отрицательных чисел и изображается флагом SF. Старший знак любого числа всегда несёт информацию о знаке: 0 - положительное число, 1 - отрицательное. При наличии единицы во флаге SF числа автоматически преобразуются в дополнительный код. Значение флага SF участвует в арифметических операциях наравне со значащими разрядами чисел.

Признак переполнения изображается флагом SF и предназначается для автоматического контроля длины слова и её адаптации к возможному переполнению разрядной сетки. Наличие единичного значения во флаге SF свидетельствует о том, что результат больше длины разрядной сетки и необходимо последовательное увеличение длины слова. В микропроцессоре предусмотрена возможность неограниченного увеличение длины слов данных при последовательном наращивании по байту или по слову.

Признак чётного паритета изображается флагом PF и применяется для выявления одиночных ошибок при передаче информации между блоками микро-ЭВМ. Флаг устанавливается равным единице, если в результате операции общее число единиц является чётным. При нечётном числе единиц в результате в сопровождающем контрольном бите устанавливается единица, так что при контроле передаваемый результат всегда является чётным. В случае нарушения чётности передаваемой информации вычисление длины автоматически прекращается. Сигналом для этого является нулевое значение во флаге PF.

Флаг DF определяет направление сканирования массива в операциях цепочками, а флаг IF выполняет функцию маскирования внешних прерываний. Прерывания воспринимаются между командами, причём запросы по входу маскируемых прерываний “мзпр” воспринимаются только при условии, что флаг IF имеет единичное значение.

Флаг TF применяется для организации пошагового выполнения команд программ при их отладке. При установке флага TF=1 микропроцессор сразу после выполнения любой текущей команды автоматически формирует прерывания. Следующая команда выполняется подачей сигнала на вход готовности.

Системе команд микропроцессора с классифицирована в традиционные для микропроцессоров группы по функциональным признакам: команды пересылок, арифметические команды, команды поразрядной обработки данных, строковые команды, команды передачи управления и команды управления микропроцесссором. Системе команд разработана с учётом опыта программирования микроп-роцессоров предыдущих серий, она позволяет повысить производительность, сократить трудоёмкость программирования, обеспечить проектирование измерительно-вычислительных систем.

13.2. Системы сбора информации с датчиков на базе

Дата добавления: 2015-07-14; просмотров: 1499;