Классификация Хендлера

В основу классификации В.Хендлер закладывает явное описание

возможностепараллельнои конвейернообработки информации

вычислительно системо. При этом он намеренно не рассматривает различные способы связи между процессорами и блоками памяти и считает, что коммуникационная сеть может быть нужным образом сконфигурирована и будет способна выдержать предполагаемую нагрузку.

Предложенная классификация базируется на различии между тремя уровнями обработки данных в процессе выполнения программ:

• уровень выполнения программы - опираясь на счетчик команд и некоторые другие регистры, устройство управления (УУ) производит выборку и дешифрацию команд программы;

• уровень выполнения команд - арифметико-логическое устройство компьютера (АЛУ) исполняет команду, выданную ему устройством управления;

• уровень битовой обработки - все элементарные логические схемы процессора (ЭЛС) разбиваются на группы, необходимые для выполнения операций над одним двоичным разрядом.

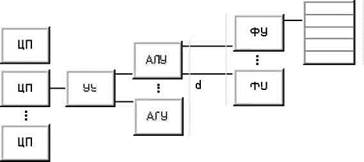

Таким образом, подобная схема выделения уровне предполагает, что вычислительная система включает какое-то число процессоров кажды со своим устроством управления. Каждое устроство управления связано с несколькими арифметико-логическими устроствами, исполняющими одну и ту же операцию в каждый конкретны момент времени. Наконец, каждое АЛУ объединяет несколько элементарных логических схем, ассоциированных с обработко одного двоичного разряда (число ЭЛС есть ничто иное, как длина машинного слова). Если на какое-то время не рассматривать возможность конвееризации, то число устройств управления к , число арифметико-логических устройств d в каждом устройстве управления и число элементарных логических схем w в каждом АЛУ составят тройку для описания данно вычислительно системы С:

t(C) = (k, d, w)

В таких обозначениях описания некоторых хорошо известных вычислительных систем будут выглядеть следующим образом:

t( MINIMA ) = (1,1,1);

t( IBM 701 ) = (1,1,36);

t( SOLOMON ) = (1,1024,1);

t( ILLIAC IV ) = (1,64,64);

t( STARAN ) = (1,8192,1) - в полно конфигурации;

t( C.mmp ) = (16,1,16) - основной режим работы;

t( PRIME ) = (5,1,16);

t( BBN Butterfly GP1000 ) = (256,-1,-32).

Несмотря на то, что перечисленным системам присущ параллелизм разного рода, он без особого труда может быть отнесен к одному из трех выделенных уровне.

на каждой ступени слово из w бит

|

| а" ФУ могут быть сцеплены |

w' ступеней конвейера

к' ЦП из к могут fjaOuiaib ы макршк-жьейери

Рис. 4.3. Уровни обработки данных в процессе выполнения программы

Теперь можно расширить возможности описания, допустив возможность конвейерно обработки на каждом из уровне (рис. 4.3). Конвейерность на самом нижнем уровне (т.е. на уровне ЭЛС) это конвейерность функциональных устройств. Если функциональное устройство обрабатывает w-разрядные слова на каждо из w' ступене конвеера, то для характеристики параллелизма данного уровня естественно рассмотреть произведение wxw'. Знак умножения х используется на каждом уровне чтобы отделить число, представляющее степень параллелизма, от числа ступене в конвейере. Компьютер TI ASC имеет четыре конвейерных устройства по восемь ступене в каждом для обработки 64-х разрядных слов, следовательно, он может быть описан так:

t( TI ASC ) = (1,4,64x8)

Следующий уровень конвейерно обработки - это конвееризация на уровне команд. Предполагается, что в вычислительно системе есть несколько функциональных устройств, которые могут работать одновременно в рамках одного потока команд (в настоящее время используется специальны термин для

обозначения данно возможности - сцепление функциональных устройств). Классическим примером этому могут служить компьютеры фирмы Cray Research. А исторически перво является машина CDC 6600, содержащая десять независимых последовательных функциональных устройств, способных подавать результат свое работы на вход другим функциональным устройствам, образуя едины поток команд:

t(CDC 6600) = (1,1x10,-64)

(описан только центральны процессор без учета управляющих и периферийных подсистем).

Конвееризация на самом верхнем уровне, известна как макро-конвейер. Поток данных, проходя через один процессор, поступает на вход другому, возможно через некоторую буферную память. Если независимо работают п процессоров, то в идеальной ситуации при отсутствии конфликтов и полно сбалансированности получаем ускорение в п раз по сравнению с использованием только одного процессора. Так компьютер РЕРЕ, имея фактически три независимых системы из 288-ми устроств, описывается следующим образом:

t( РЕРЕ ) = (1x3,288,32)

После расширения трехуровнево модели параллелизма средствами описания потенциальных возможносте конвееризации каждая тройка

t( РЕРЕ) = (kxk',dxd',wxw')

интерпретируется так:

• к - число процессоров (каждый со своим УУ), работающих параллельно

• к1 - глубина макроконвейера из отдельных процессоров

• d - число АЛУ в каждом процессоре, работающих параллельно

• сГ - число функциональных устройств АЛУ в цепочке

• w - число разрядов в слове, обрабатываемых в АЛУ параллельно

• w' - число ступеней в конвейере функциональных устройств АЛУ

Очевидна связь между классификацие Фенга и классификацие Хендлера:

для получения максимально степени параллелизма в терминах Фенга надо найти произведение всех шести величин в описании Хендлера. Здесь же заметим, что заложив в основу свое схемы явное указание на присутствующи параллелизм и возможную конвееризацию, В.Хендлер сразу снимает массу вопросов, характерных для предшествующих схем Флинна и Фенга в плане описания векторно-конвейерных машин.

В дополнение к изложенному способу описания архитектур Хендлер предлагает использовать три операции, которые будучи примененными к тройкам, позволят описать:

• сложные структуры с подсистемами ввода-вывода, хост-компьютером или какими-то другими особенностями;

• возможные режимы функционирования вычислительных систем, поддерживаемые для оптимального соответствия структуре программ.

Первая операция (х) отражает конвейерный принцип обработки и предполагает последовательное прохождение данных сначала через первый ее аргумент-подсистему, а затем

через второй. Описание упомянутого выше компьютера CDC 6600 можно уточнить следующим образом:

t( CDC 6600 ) = (10,1,12) х (1,1x10,64),

где первый аргумент отражает существование десяти 12-ти разрядных периферийных процессоров и тот факт, что любая программа должна сначала быть обработана одним из них и лишь после этого передана центральному процессору для исполнения. Аналогично можно получить описание машины РЕРЕ, принимая во внимание, что в качестве хост-компьютера она использует CDC 7600:

t( РЕРЕ ) = t( CDC 7600 ) х (1x3, 288, 32) = = (15, 1, 12) х (1, 1x9, 60) х (1x3, 288,

32)

Поток данных последовательно проходит через три подсистемы, что мы и отразили, соединив их знаком У. Все подсистемы последнего примера достаточно сложны и исходя только из данного описания могут представляться по-разному. Чтобы внести большую ясность, аналогично операции конвейерного исполнения, Хендлер вводит операцию параллельного исполнения (+), фиксирующую возможность независимого использования процессоров разными задачами:

t(n,d,w) = ri(l,d,w) + ... + (l,d,w)l {праз}

В случае CDC 7600 уточненная запись вида:

(15, 1, 12) х (1, 1x9, 60) = [(1, 1, 12) + ... +(1, 1, 12)]} {15раз} х (1, 1x9, 60)

говорит о том, что каждая задача может захватить сво периферийны процессор, а затем одна за одно они будут поступать в центральны процессор.

Третья операция - операция альтернативы (V), показывает возможные альтернативные режимы функционирования вычислительно системы. Чем больше для системы таких режимов, тем более гибко архитектуро, по мнению Хендлера, она обладает. Например, компьютер C.rnmp может быть запрограммирован для использования в трех принципиально разных режимах:

t( C.rnmp ) = (16,1, 16) V (1x16, 1,1 6) V (1, 16, 16).

4. Архитектура параллельных вычислительных систем

Дата добавления: 2015-08-21; просмотров: 1833;