Устройство портов.

Каждый из портов содержит регистр-защелку (SFR P0 — SFR P3), выходную цепь и входной буфер.

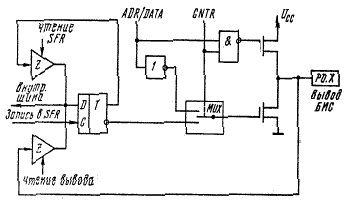

Рис.3.Порт P0

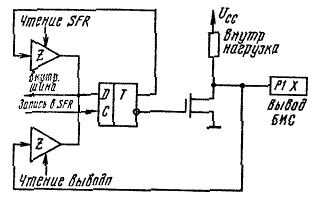

Рис.4.Порт P1

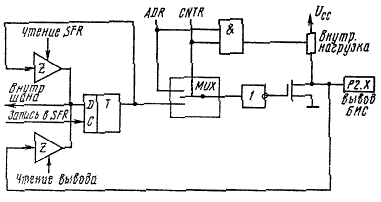

Рис.5.Порт P2

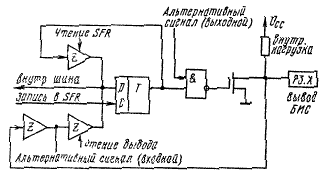

Рис.6.Порт P3

На рисунке изображены функциональные схемы регистров-защелок и буферов ввода-вывода всех портов микро-ЭВМ 8051. Каждый из разрядов регистра-защелки SFR является D-триггером, информация в который заносится с внутренней шины данных микроконтроллера по сигналу «Запись в SFR Pх» (х= 0, 1, 2, 3) от центрального процессорного элемента (CPU). С прямого выхода D-триггера информация мажет быть выведена на внутреннюю шину по сигналу «Чтение SFR Pх» от CPU, а с вывода микросхемы («из внешнего мира») по сигналу «Чтение выводов Pх». Одни команды активизируют сигнал «Чтение SFR PI», другие - «Чтение выводов РI».

Дата добавления: 2015-06-05; просмотров: 889;