Листинг 1. Блок my_register.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY my_register IS

PORT ( clock, resetn : IN STD_LOGIC; --синхросигнал и сигнал сброса

byte_enable : IN STD_LOGIC_VECTOR(3 DOWNTO 0); --побайтное разрешение записи

data : IN STD_LOGIC_VECTOR(31 DOWNTO 0); --вход данных

q : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); --выход регистра

END my_register;

ARCHITECTURE Behavior OF my_register IS

BEGIN

PROCESS ( clock, resetn)

BEGIN

IF resetn = '0' THEN

q <= "00000000000000000000000000000000";

ELSIF clock'EVENT AND clock = '1' THEN

IF byte_enable(0) = '1' THEN

q(7 DOWNTO 0) <= data(7 DOWNTO 0); END IF;

IF byte_enable(1) = '1' THEN

q(15 DOWNTO 8) <= data(15 DOWNTO 8); END IF;

IF byte_enable(2) = '1' THEN

q(23 DOWNTO 16) <= data(23 DOWNTO 16); END IF;

IF byte_enable(3) = '1' THEN

q(31 DOWNTO 24) <= data(31 DOWNTO 24); END IF;

END IF;

END PROCESS;

END Behavior;

Листинг 2. Блок my_register_slave_interface.vhd

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY my_register_slave_interface IS

PORT( clock, resetn, read, write, chip_select : IN STD_LOGIC; --

byte_enable : IN STD_LOGIC_VECTOR(3 DOWNTO 0); -- Основные сигналы

writedata : IN STD_LOGIC_VECTOR(31 DOWNTO 0); -- шины Avalon

readdata : OUT STD_LOGIC_VECTOR(31 DOWNTO 0); --

to_lights : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) ); -- вывод на светодиоды

END my_register_slave_interface;

ARCHITECTURE Structure OF my_register_slave_interface IS

SIGNAL local_byteenable : STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL to_reg, from_reg : STD_LOGIC_VECTOR(31 DOWNTO 0);

COMPONENT my_register

PORT ( clock, resetn : IN STD_LOGIC;

data : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

byte_enable : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

q : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT;

BEGIN

my_instance: my_register PORT MAP( clock, resetn, to_reg, local_byteenable, from_reg );

to_lights <= from_reg; --

to_reg <= writedata; -- Создание Avalon MM Slave интерфейса

readdata <= from_reg; -- для регистра

WITH (chip_select AND write AND not read ) SELECT --

local_byteenable <=byte_enable WHEN '1',

"0000" WHEN OTHERS;

END Structure;

Последовательность действий, выполняемых пользователем для создания нового компонента SOPC Builder, должна быть следующей.

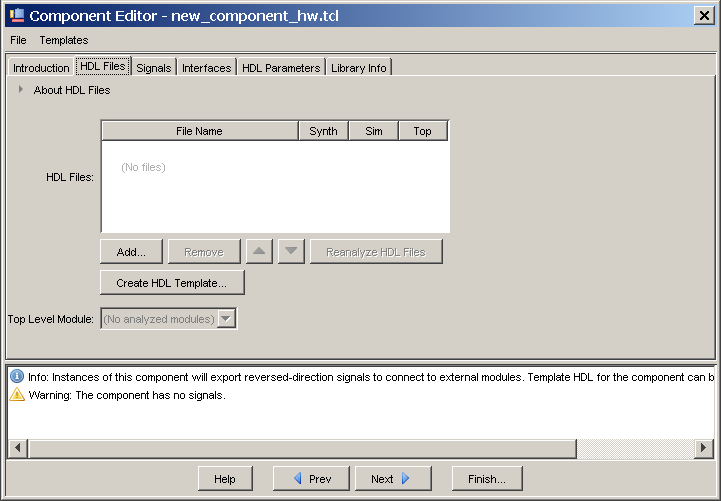

1) Вначале необходимо запустить редактор нового компонента, как это описано в предыдущем разделе 1.6, затем в открывшемся окне редактора открыть вкладку HDL Files, как показано на рис. 1.48.

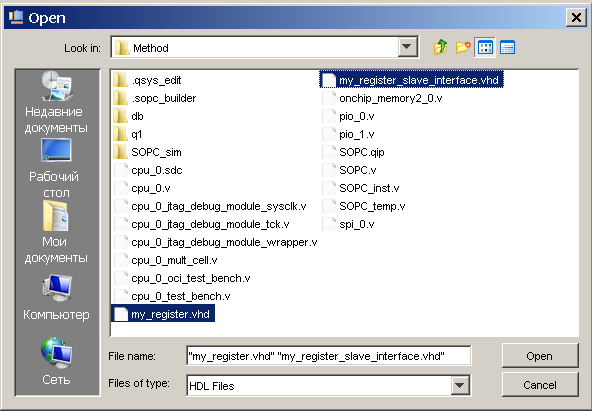

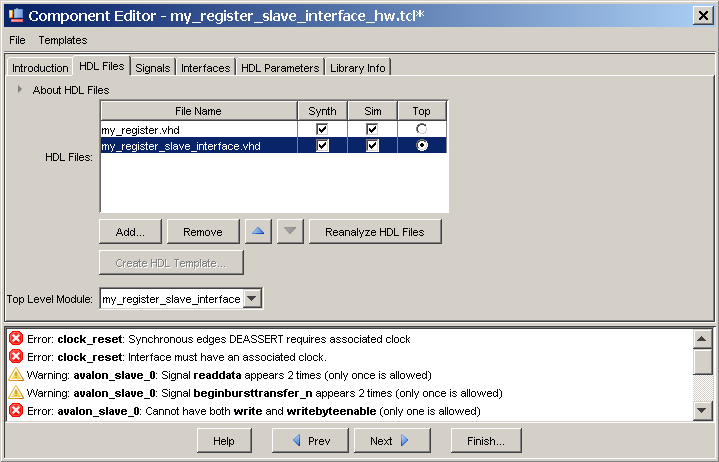

2) Далее необходимо нажать кнопку “Add…” и в появившемся окне найти созданные HDLфайлы в файловой системе инструментального компьютера, как это показано на рис. 1.49. После нажатия кнопки Open в правой нижней части окна, редактор начнет анализ файла верхнего уровня на наличие в нем интерфейсных сигналов. В случае если он выберет неверный файл верхнего уровня, необходимо его указать в явном виде, кликнув левой кнопкой мыши в столбцеTop, напротив соответствующего файла. Заполненная вкладкаHDL Files для рассматриваемого примера, представлена на рис. 1.50. В ходе анализа файлов редактор попытается заполнить вкладкиSignals иInterfacesсамостоятельно.

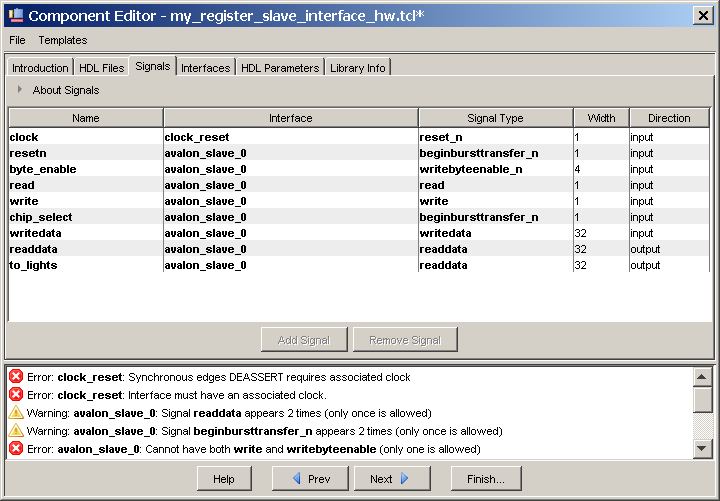

Рис. 1.48 – Вкладка HDL Files

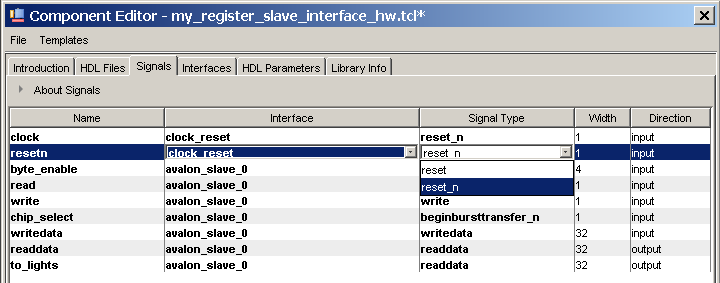

3) Следующим шагом является исправление ошибок и предупреждений, отображенных редактором в нижней части окна, путем коррекции параметров во вкладках Signals и Interfaces.Вкладка Signalsдля рассматриваемого примера представлена на рис. 1.51. Как видно из рисунка, необходимо скорректировать сигналы clock, resetn, byte_enable, chip_select и to_lights. Сигнал resetn это сигнал сброса, относится к типу интерфейса clock_reset, а типом сигнала является reset_n. Ввод таких корректировок осуществляется нажатием левой кнопки мыши, по соответствующему элементу и выбору из выпадающего списка необходимого параметра, как это показано на рис. 1.52. Сигнал byte_enable соответствуют интерфейсу avalon_slave_0 с типом сигнала byte_enable.

Рис. 1.49 – Выбор файлов HDL описания нового компонента

Рис.1.50 – Заполненная вкладка HDL Files

Рис. 1.51 – Вкладка Signals для рассматриваемого примера

Рис. 1.52 – Корректировка параметров

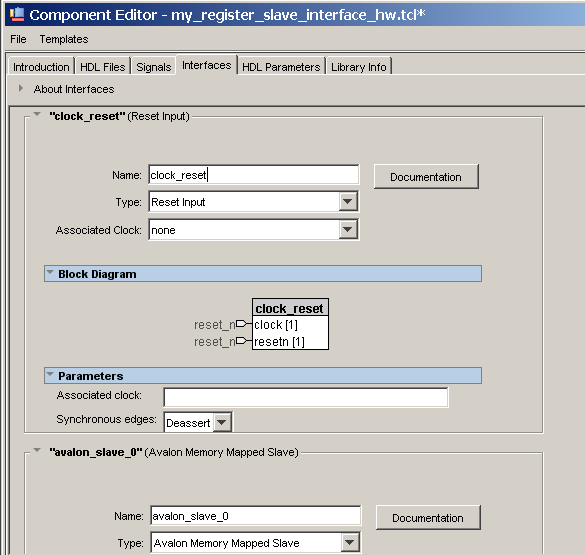

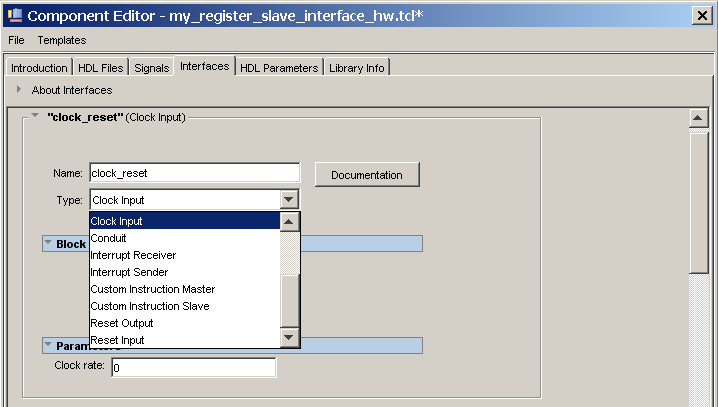

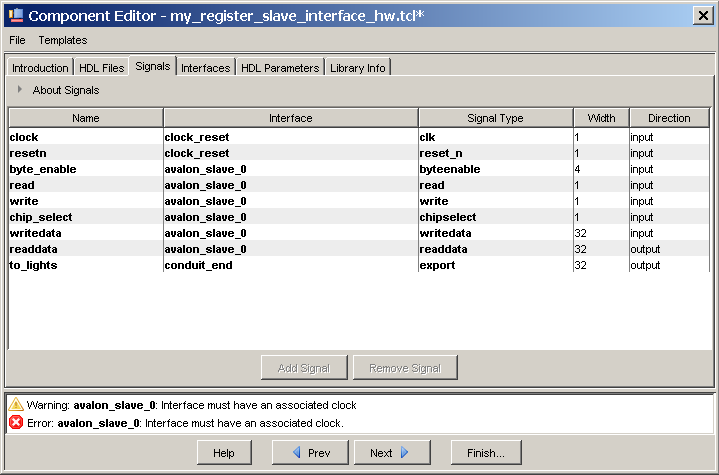

Сигнал chip_select является сигналом типа chip_select интерфейса avalon_slave_0. Шина to_lights предназначена для вывода содержимого регистра на светодиоды, поэтому она должна относиться к интерфейсу Conduit с типом сигналов export. Последним шагом является настройка сигнала clock. Для этого, необходимо перейти во вкладку Interfaces, так как редактор нового компонента неправильно распознал этот сигнал и необходимо изменить его тип. Во вкладке Interfaces представлены все используемые интерфейсы и их параметры, рис. 1.53. Здесь необходимо для интерфейса clock_resetустановить тип “Clock Input”, выбрав его в выпадающем списке, рис. 1.54. После чего, необходимо вернуться во вкладку Signalsи для сигнала clock установить тип сигнала – clk. Полностью заполненная правильными значениями вкладка представлена на рис. 1.55.

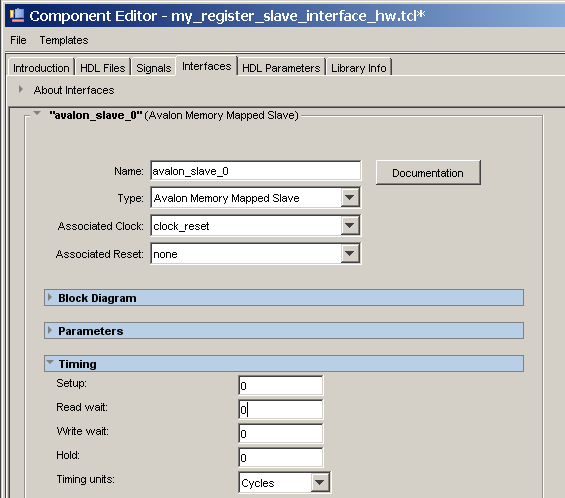

Последним шагом по корректировке параметров является назначение сигнала синхронизации для интерфейса Avalon_slave_0 и временных задержек для него во вкладке Interfaces. Чтобы назначить синхросигнал, необходимо выбрать “clock_reset” в выпадающем списке рядом с надписью Associated Clock. Ввиду того, что при доступе к созданному аппаратному блоку отсутствует задержка, в полях раздела Timing интерфейса Avalon_slave_0 должны быть нулевые значения. Для удобства пользователя, в разделах Read Waveform и Write Waveform отображаются временные диаграммы работы интерфейса с учетом параметров задержек. Фрагмент заполненной вкладки представлен на рис. 1.56.

Рис. 1.53 – Фрагмент вкладки Interfaces

Рис. 1.54 – Выбор типа интерфейса

Рис. 1.55 – Заполненная вкладка Signals

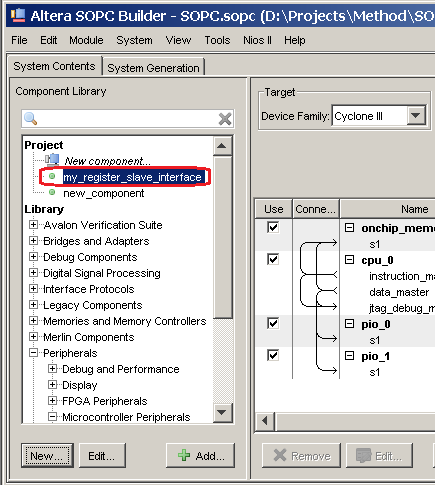

4) Далее во вкладке Library Infoнеобходимо назначить имя для создаваемого компонента и нажать кнопку “Finish”. После чего данный компонент появится в списке компонентов SOPC Builder, готовый для вставки в процессорную систему, как это показано на рис. 1.57.

Рис. 1.56 – Фрагмент заполненной вкладки Interfaces

Рис. 1.57 – Результат работы мастера создания новых компонентов

Дата добавления: 2015-05-30; просмотров: 1805;