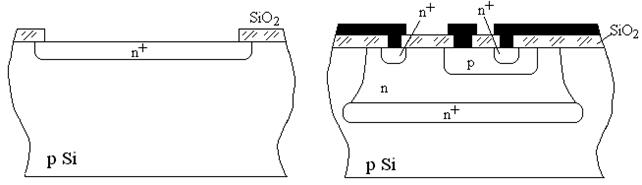

Со скрытым слоем

Первыми операциями при изготовлении таких микросхем являются термическое окисление, фотолитография и диффузия донорной примесью, чтобы создать n+ - слой на месте, где будут формироваться транзисторы (рисунок 4.8а). Толщина этого слоя составляет примерно 2 мкм. Затем слой SiO2 стравливается. В последующем проводится эпитаксия и последовательно все операции, которые использовались при изготовлении планарно–эпитаксиального транзистора. Структура готового транзистора приведена на рисунке 4.8б.

| а) | б) |

Рисунок 4.8

Распределение примесей приведено на рисунке 4.9. Поскольку в коллекторе основного транзистора (этот же слой является базой паразитного транзистора) распределение примеси неравномерное, то в нем создается тормозящее электрическое поле для дырок, которые движутся из эмиттера в коллектор паразитного транзистора. Кроме того, высокая концентрация примеси в коллекторе на порядок снижает распределенное сопротивление rК основного транзистора. Это исключает недостатки планарно-эпитаксиального транзистора.

Рисунок 4.9

Дата добавления: 2015-04-21; просмотров: 1007;