Недвоичные счётчики с предварительной записью

В счётчиках с обратной связью исключаются последние состояния двоичного счётчика. Можно поступить по-другому. Начать с последнего состояния счётчика и, воспользовавшись вычитающим счётчиком, определять нулевое состояние счётчика. Это состояние очень просто можно определить при помощи логического элемента "И". В данной схеме начинать счёт необходимо с числа, которое будет определять коэффициент деления делителя, построенного на таком счётчике.

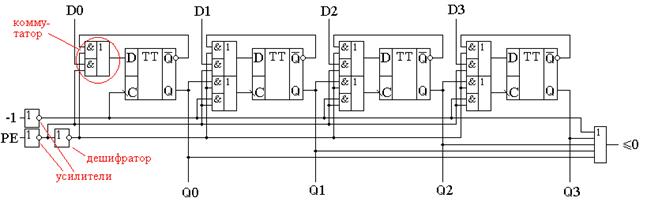

При построении счётчика по таким принципам необходимо иметь возможность предварительной записи в счётчик. То есть счётчик при предварительной записи должен вести себя как параллельный регистр. Опять нам требуется, как и при построении универсального регистра, коммутатор логических сигналов.

Напомню, что в качестве коммутатора вполне успешно используется логический элемент “2И-2ИЛИ”. Главное обеспечить подачу на элементы “И” противофазных сигналов. Это условие нам обеспечит инвертор.

Одна из схем счётчика, с возможностью параллельной записи двоичных кодов во внутренние триггеры счётчика, приведена на рисунке 13.1. В этой схеме вход C предназначен для подачи тактовых импульсов. Его ещё называют "-1", так как при подаче на этот вход импульсов, содержимое счётчика уменьшается на единицу. Входы D0 ... D3 предназначены для записи произвольного двоичного числа в счётчик. Запись производится по сигналу, подаваемому на вход параллельной записи PE.

Рисунок 13.1. Схема счётчика с возможностью параллельной записи

На первый взгляд схема достаточно сложна. Однако если приглядеться, то она состоит из одинаковых узлов. Информационные входы D триггеров могут быть подключены либо к входу параллельной записи, либо к инверсному выходу триггера. Так как в схеме применено четыре триггера, то для коммутации входов требуется четыре мультиплексора.

Точно так же переключаются источники сигналов и на тактовых входах триггеров. Входы триггеров либо подключены к выходу предыдущего триггера, либо к цепи синхронизации. Условно-графическое обозначение двоичного счётчика с возможностью параллельной записи приведено на рисунке 13.2.

Рисунок 13.2. Условно-графическое обозначение счётчика с возможностью параллельной записи

Ну а теперь, точно так же как и в предыдущем примере, попробуем реализовать делитель с коэффициентом деления 1000. Вспомним, что при разработке делителя частоты сначала определяется количество микросхем двоичных счётчиков. Для этого определим степень числа 2, при которой число M=2n будет больше требуемого числа 1000.

Получаем число десять. При возведении основания системы счисления 2 в 10 степень получится число 1024. При использовании четырёхразрядных двоичных счётчиков достаточно будет трёх микросхем, так как в трёх микросхемах будет 3*4=12 триггеров, что заведомо больше минимального числа триггеров.

Следующим этапом построения делителя частоты будет перевод коэффициента деления 1000 в двоичное представление. Перевод чисел между системами счисления мы рассматривали в предыдущих главах. Десятичное число 100010 в двоичном виде будет выглядеть как 0011 1110 10002. Как мы уже говорили, с этого числа должен начинаться счёт вычитающего счётчика.

Схема делителя частоты на 1000 приведена на рисунке 3. В этой схеме первая микросхема является младшей, поэтому в неё загружается младшая тетрада числа предварительной записи 100010, равная 10002. В следующую микросхему загружается число 11102, а в последнюю микросхему — 00112.

Рисунок 13.3 Схема делителя на 1000, построенного на основе трёх двоичных счётчиков с предварительной записью

Для определения нулевого состояния триггеров счётчика служит выход <0. Для этого внутри микросхемы расположен логический элемент "4ИЛИ". Чтобы определить обнулились ли все три микросхемы, в схеме на рисунке 3 счётные входы микросхем –1 соединяются с входом переноса предыдущей микросхемы. Как только такое состояние обнаруживается, сигнал поступает на входы параллельной записи PE, и в счётчик снова записывается число 1000.В результате работы приведённой схемы на выходе делителя импульс возникает один раз после подачи на его вход тысячи импульсов.

Обратите внимание, что на этот раз коэффициент деления заключён не в принципиальной схеме делителя, а просто подаётся на вход параллельной записи счётчиков. В результате процесс изменения коэффициента деления значительно упростился. Для изменения частоты на выходе делителя достаточно просто подать нужное число. Схема делителя, в отличие от схемы недвоичного счётчика с обратной связью, при этом не меняется.

Для построения делителя с переменным коэффициентом деления мы использовали вычитающий счётчик. Можно ли такую же схему построит на суммирующем счётчике? Можно! Однако в этом случае придётся для записи коэффициента деления воспользоваться отрицательным числом в дополнительном коде. Для того, чтобы получить отрицательное число в этом коде необходимо положительное двоичное число проинвертировать и прибавить единицу. Например, для реализации коэффициента деления 1000 возьмём его двоичный эквивалент 0011 1110 10002. После инвертирования получим число 1100 0001 01112. Окончательный результат будет равен 1100 0001 10002.

Для десятиразрядного двоичного кода это будет равно десятичному эквиваленту 2410. Действительно, если в счётчике с коэффициентом 210=1024 начать считать от числа 24, то ровно через 100010 импульсов счётчик переполнится и станет равным нулю.

Дата добавления: 2014-12-24; просмотров: 1134;