Технические параметры или показатели памяти.

· Объем памяти или емкость памяти – количество бит двоичной информации, которую память хранит постоянно или пи наличии питания.

к = 1024 байт * 8 = … бит

· Объем выборки или разрядность – количество бит информации, которая записывается в память или считывается из нее за один машинный цикл.

· Время доступа – время, в течение которого от момента поступления адреса ячейки памяти до вывода информации на ШД (чтение) или от момента поступления адреса ячейки памяти до записи информации с ШД в ячейку.

· Время цикла – интервал времени между двумя соседними разрешенными обращениями к памяти.

· Скорость обмена информацией – количество бит информации, передаваемой, записывающейся или считывающейся в единицу времени.

· Энергозависимость – способность сохранять информацию в зависимости от наличия питания.

· Себестоимость хранения одного бита информации зависит от количества бит информации, помещающихся в единице объема кристалла. Этот параметр определяет стоимость ЗУ.

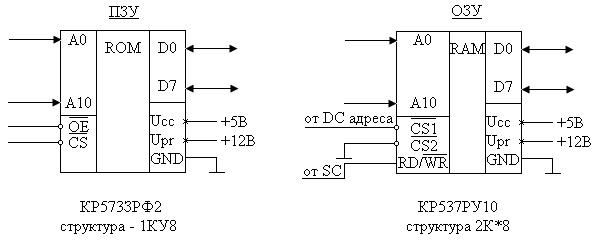

· Схема выводов:

Классификация ЗУ.

1. По функциональному назначению:

1.1. внутренние ЗУ – те, которые находятся внутри МП, и, с которыми МП общается через системные шины или внутреннюю ШД.

К ним относят:

· сверхоперативные регистры;

· оперативные ЗУ, предназначенные для хранения команд и данных оператора;

· постоянные ЗУ, предназначенные для хранения программы «монитор», констант и другого, которые записываются на заводе-изготовителе.

1.2. буферные ЗУ – запоминающие устройства для хранения больших объемов информации, к которой МП обращается через порты ввода/вывода.

1.3. внешние ЗУ, которые предназначены для согласования сигналов по уровню, форме (последовательная или параллельная) и по коду. Эти ЗУ входят в состав портов ввода/вывода в виде интерфейсных блоков.

*Интерфейс – ИС сопряжения различных блоков и устройств.

2. По способу доступа к ЗУ:

2.1. ЗУ с произвольным доступом – полупроводниковые ЗУ. Эти схемы позволяют считывать и записывать информацию по любому адресу, не затрагивая предыдущего адреса. Их достоинство – малое время доступа (  =200 нс).

=200 нс).

2.2. ЗУ с последовательным доступом, в котором нужная информация считывается или записывается по указанному адресу только после прохождения всех предыдущих адресов.

Область применения:

· Внутренние ЗУ МП-системы, кроме стека;

· Внешние ЗУ – диски, бобины, флэш-карты.

Оперативные ЗУ.

В зависимости от используемого элемента памяти различают статические и динамические ОЗУ. В статических ОЗУ в качестве элементарной ячейки на 1 бит используется триггер. В динамических ОЗУ в качестве элементарных ячеек памяти используются конденсаторы.

Статические ОЗУ.

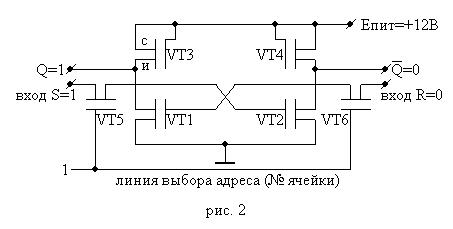

Статические ОЗУ могут выполняться на биполярных транзисторах (рис.1) или на МОП-транзисторах (рис.2).

По линии выбора адреса всегда поступает нулевой сигнал. Если на входе SET тоже 0, то  будет полным, в результате Q=0. Этот потенциал подается на базу VT2, который закрыт, его

будет полным, в результате Q=0. Этот потенциал подается на базу VT2, который закрыт, его  и потенциал на

и потенциал на  . Такое состояние сохраняется до тех пор, пока не поступят новые сигналы на S и R.

. Такое состояние сохраняется до тех пор, пока не поступят новые сигналы на S и R.

Транзисторы VT3 и VT4 выполняют функции нагрузочных регистров  . Транзисторы VT5 и VT6 играют роль входных вентилей – ключей. По линии «выбор адреса ячейки памяти» поступает сигнал логической единицы, тогда VT5 и VT6 открыты. Если S=0 и R=0, то на затвор VT2 подана единица, а на VT1 – 0. VT2 пропускает ток, на его выходе будет 0 (

. Транзисторы VT5 и VT6 играют роль входных вентилей – ключей. По линии «выбор адреса ячейки памяти» поступает сигнал логической единицы, тогда VT5 и VT6 открыты. Если S=0 и R=0, то на затвор VT2 подана единица, а на VT1 – 0. VT2 пропускает ток, на его выходе будет 0 (  ), тогда Q=1.

), тогда Q=1.

Достоинство схемы 1 – высокое быстродействие, поэтому она применяется, когда требуется большая скорость срабатывания. Недостатки – более дорогой технологический способ изготовления или более высокая стоимость такого типа ЗУ.

В схеме 2 вес наоборот, поэтому она более распространена из-за дешевизны. Ее главным достоинством является то, что не требуется никаких блоков регистрации данных для поддержания записанной в памяти информации.

Динамические ОЗУ.

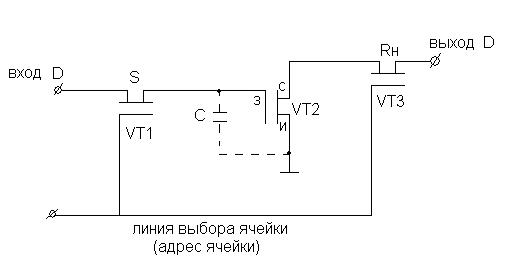

Ячейка динамической ОЗУ на 1 бит (на МОП-транзисторах).

В отличие от статических ОЗУ, у которых запоминающим элементом является триггер на биполярных или полевых транзисторах, у динамических ОЗУ запоминающим элементом является конденсатор, который представляет собой паразитную емкость между затвором и истоком транзистора VT2. Поскольку на затвор подается обратное напряжение порядка 1000 в, то входное сопротивление такого трансформатора представляет величину 10 Мом, что эквивалентно сопротивлению конденсатора. По линии выбора адреса ячейки памяти подается сигнал логической единицы, поэтому затворы VT1, VT3 открывают эти приборы. Транзистор VT1 выполняет функцию включателя, транзистор VT3 – функцию сопротивления нагрузки. При подаче на вход данных в виде логической 1 транзистор VT2 отпирается и паразитная емкость С заряжается до величины этого напряжения, т. е. хранит логическую единицу. Если сигнал на вход не поступает, то С не заряжен и хранит логический нуль. Поскольку VT3 открыт, то логическая единица конденсатора поступает на выход (шина данных).

Достоинства:

- на той же площади кристалла размещается больше бит информации (тут 3 VT, а там 6), следовательно, эти схемы дешевле.

- по сравнению со статическими ОЗУ потребляемая мощность меньше.

Недостатки:

- через сопротивление изоляции между затвором и истоком транзисторов VT1 и VT2 постоянно происходит разряд конденсатора, поэтому с интервалом в 2 мкс необходимо подзаряжать конденсатор, этот процесс называется регенерацией данных.

Динамические ОЗУ для надежного хранения информации требуют дополнительного блока регенерации данных, поэтому если объем динамических ОЗУ маленький, то стоимость блока регенерации «съедает» положительный эффект, который получен размещением большего объема информации. Поэтому динамические ОЗУ применяют: в схемах, хранящих большой объем информации.

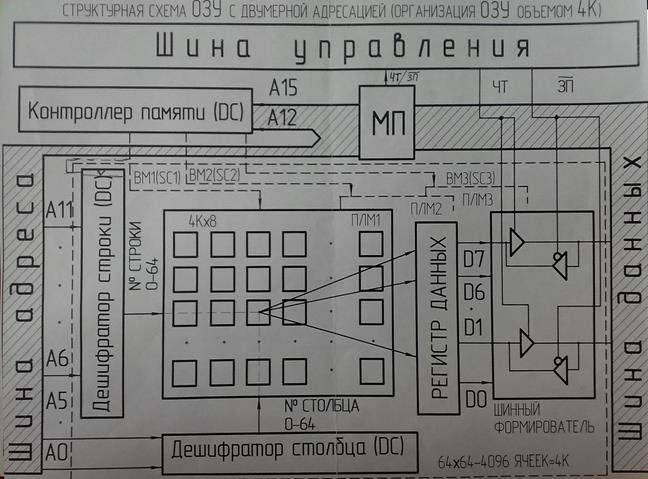

Организация ОЗУ.

Физически ОЗУ состоит из 3х блоков:

1) ПП-матрицы ячеек памяти;

2) дешифратора адреса ячейки;

3) схемы (блока) управления.

Дешифрация адреса выбранной по программе ячейки ОЗУ осуществляется с помощью регистра адреса и 2х декодеров (дешифраторов), определяющих номер строки и номер столбца, на пересечении которых находится нужная ячейка. Распределение адресов происходит следующим образом: старшие байты адреса А12-А15 идут на контроллер памяти, который выдает сигнал выбор модуля CS на выбор соответствующей ИС памяти ПЛМ1, ПЛМ2, … Нумерация адресов в каждой логической матрице одинаковая, информация считывается из ячейки памяти той матрицы, которая получила сигнал выбор модуля – CS. Остальные разряды адреса А0-А11 распределяются между декодерами строк и столбцов – это процесс адресации нужной ячейки памяти.

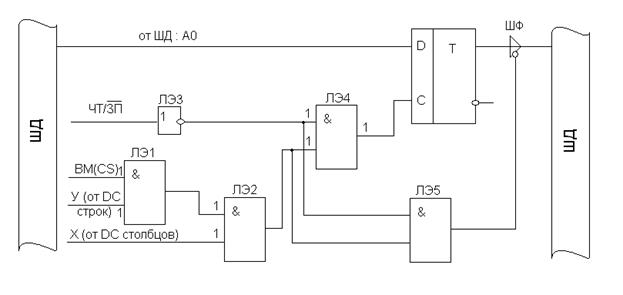

Процесс считывания или записи данных в ячейку памяти осуществляется с помощью схемы управления каждой ячейки.

Таблица состояний:

| BM(CS) | ЧТ/ЗП | Состояние |

| Чтение из ячейки | ||

| Запись | ||

| Память | ||

По поступлении CS высокого уровня, ЛЭ1 (И) срабатывает, возбуждает ЛЭ2, который также срабатывает, результирующий сигнал 1 поступает на один из входов ЛЭ4. Сигнал на втором входе ЛЭ4 зависит от выполняемой операции – чтение/запись. При записи информации в ОЗУ: на входе ЛЭ4 – 1, его схема срабатывает и подает STB-сигнал на D-триггер. В результате данные разряда А0 записываются в триггер. При чтении ячейки ОЗУ: на вход ЛЭ4 поступает 0, 1, на выходе его 0 и триггер не включается (нет STB), зато ЛЭ5 выдает сигнал 0, разрешающий инициализацию формирующую вывод данных из триггера на шину данных.

ПЗУ.

ПЗУ предназначено для постоянного хранения программ и данных. Достоинства перед ОЗУ:

1) меньше потребление мощности;

2) энергонезависимость;

3) хранение большего объема информации.

Классификация в зависимости от способа занесения информации в ПЗУ:

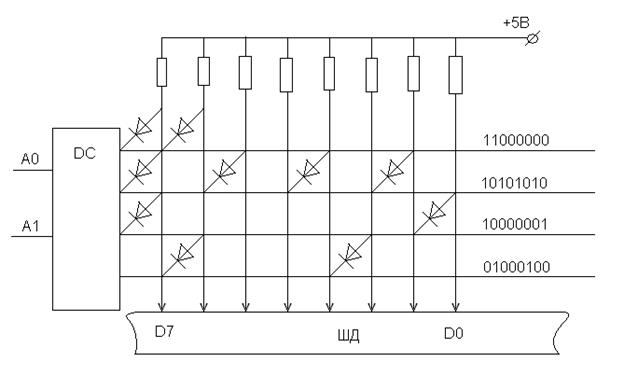

а) стандартные (масочные) ПЗУ. Запись информации в эти ИС производится на заводе изготовителе с помощью шаблонов-масок, т. к. изготовление шаблонов – дорогостоящий процесс, то экономически выгодно применять масочные ПЗУ только в массовом производстве. Примером масочной ПЗУ может служить:

Запись 1/0 – установление связи между шиной адреса и шиной данных. 1 – наличие тока между шиной адреса и шиной данных.

Потребитель не имеет возможности изменить информацию.

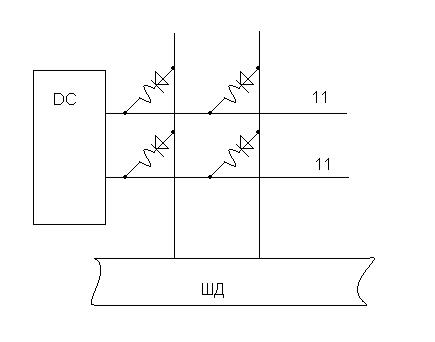

б) перепрограммируемые (ППЗУ) - схемы памяти, допускающие однократное перепрограммирование по желанию заказчика – 1 раз: схемы ПЗУ с пережигаемыми перемычками.

Завод-изготовитель выпускает ИС в которой, в каждой ячейке памяти – 1.

Пережигание перемычек осуществляется импульсами напряжения 10-12 В, и длительностью 100 мс. Эта операция выполняется на специальном программаторе.

в) многократно перепрограммируемые (СППЗУ – стираемые ППЗУ). Эти схемы допускают многократное стирание и запись информации. Стирание выполняется с помощью УФ-излучения через специальное кварцевое окно в ИС с расстояния 10 см в течение 20 мин. Запись осуществляется путем подачи импульсов определенной длительности.

г) электрически перепрограммируемые ПЗУ (ЭППЗУ) допускают многократное стирание и запись информации электрическими импульсами определенной длительности, в течение нескольких мс. Дорогая стоимость обьясняется требованием большого расстояния между соседними ячейками памяти, во избежание их повреждения во время записи/стирания информации.

Организация ПЗУ такая же как у ОЗУ, только легче, т. к. нет сигнала «запись».

Дата добавления: 2019-07-26; просмотров: 539;