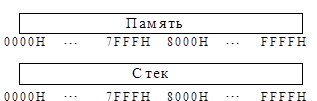

Раздельная адресация стека и памяти с произвольным доступом

Команды обращения к стеку:

PUSH rp. и POP rp;

При операциях со стеком в слове состояния устанавливается разряд D2=1, по которому формируется сигнал шины управления STACK.

Для выбора вида памяти формируются дополнительные сигналы шины управления:

(MEMR Ú MEMW) Ù STACK – для памяти с произвольным доступом;

(MEMR Ú MEMW) Ù STACK –для стека.

Сопряжение по электрическим параметрам

Виды сопряжений

а) Сопряжение по напряжению: используются уровни ТТЛ

“1” « U > 2.4 В;

“0” « U = –0.3 ¸ +0.8 В

б) Сопряжение по току нагрузки:

SIНАГР< IДОП.

Все выходы МП нагружаются на один ТТЛ вход.

в) Сопряжение по емкостной нагрузке:

SСНАГР< СДОП.

Определяется длиной проводников, подключаемых на выход.

г) Сопряжение более одного источника сигналов, подключаемых к одной цепи:

- временное разделение сигналов;

- перевод выходов не активных источников в 3-е состояние.

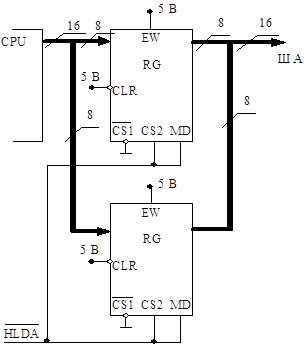

Буфер шины адреса

Обеспечивает сопряжение шины адреса по электрическим параметрам.

Реализован на многорежимных буферных регистрах К589ИР12 (К580ИР82, КР580ИР83).

При передаче шины МПС контроллеру прямого доступа к памяти выходы регистров переводятся в 3-е состояние.Схема буфера шины адреса

Рис. 3.1.

Рис. 3.1.

Управление входы МБР:

CS1, CS2 – вх. выбор кристалла;

MD – вх. выбор режима (0 –режим ввода, 1 – рåæèì вывода);

EW – вх. стробирующего сигнала;

CLR – сброс МБР;

HLDA – предоставление захвата шины при ПДП.

Буфер шины данных

Реализуется на шинных формирователях К589АП16 (К589АП 26). Применяется, если не используется системный контроллер или для увеличения нагрузки.

Дата добавления: 2017-10-09; просмотров: 651;