Вспомогательные последовательные интерфейсы и шины

Рассматриваются интерфейсы и шины, предназначенные, в основном, для «внутреннего использования».

Интерфейс SPI (Serial Peripheral Interface), — трехпроводный синхронный с раздельными линиями входных и выходных данных — применяется для связи микроконтроллеров с периферийными микросхемами и микросхемами памяти. С его помощью программируются многие микросхемы программируемой логики (например, FPGA фирмы Altera), применяемые в различных узлах ПК и периферии. Частота синхронизации может достигать 5 МГц (зависит от подключаемых устройств); при этом за каждый такт синхронизации одновременно может и передаваться, и приниматься очередной бит данных. В основном варианте использования предполагается, что интерфейс соединяет одно ведущее устройство с одним или несколькими ведомыми устройствами. Интерфейс может применяться и для обмена между несколькими микроконтроллерами, допуская наличие на шине нескольких ведущих устройств, но протокол предоставления доступа не стандартизован. Ниже рассматривается работа интерфейса с одним ведущим устройством. В интерфейсе используются 3 обязательных сигнала:

♦ SCK (Serial Clock) — синхросигнал, которым ведущее устройство стробирует каждый бит данных;

♦ MOSI (Master Output Slave Input) — выходные данные ведущего устройства и входные данные ведомого устройства;

♦ MISO (Master Input Slave Output) — входные данные ведущего устройства и выходные данные ведомого устройства.

Кроме того, может использоваться сигнал выбора ведомого устройства SS# (Slave Select, или CS# — Chip Select): ведомое устройство должно реагировать на сигналы интерфейса и генерировать выходные данные на линии MISO только при низком уровне этого сигнала; при высоком уровне выход MISO должен переводиться в высокоимпедансное состояние. С помощью сигналов SS#, раздельно формируемых ведущим устройством для каждого из ведомых устройств, ведущее устройство может выбирать партнером в транзакции одно из ведомых. При этом получается гибридная топология соединений: по сигналам SCK, MOSI и MISO — топология шинная, по SS# — звездообразная (центр — ведущее устройство).

Возможен и иной способ общения ведущего устройства с несколькими ведомыми устройствами с чисто шинной топологией. Здесь сигнал SS# для выбора устройств не используется, но ведомые устройства все время «слушают» шину, ожидая специальной адресной посылки в начале транзакции. Опознав свой адрес, устройство отрабатывает дальнейшие протокольные посылки, и теперь ему разрешается выводить данные на линию MISO до конца текущей транзакции. Однако этот вариант требует довольно сложной логики поведения ведомого устройства.

Рис..5. Форматы передач по интерфейсу SPI

Данные передаются старшим битом вперед. Устройства различных производителей могут использовать разные режимы обмена (SPI Mode 0... SPI Mode 3), различающиеся фазой и полярностью синхросигналов. Рис. 5 иллюстрирует передачу и прием байта в различных режимах. Заметим, что в любом режиме входные и выходные данные стробируются по разным перепадам синхроимпульсов. Кроме того, есть варианты в использовании сигнала SS#. В первом варианте (он и представлен на рисунке) для ведомого устройства признаком начала транзакции является спад сигнала SS#, а завершения — его подъем. Во втором варианте начало транзакции определяется по первому фронту (спаду) SCK, а сигнал SS# может иметь низкий уровень постоянно. Второй вариант иногда предпочитают для простейшего двухточечного интерфейса с единственным ведущим устройством и единствен ным ведомым устройством, когда нет опасения потери синхронизации. Микроконтроллеры с аппаратным портом SPI, как правило, имеют возможность программного выбора режима. Форматы транзакций зависят от устройств, но общая идея такова: ведущее устройство по линии MOSI посылает код операции и адресную информацию для устройства; затем следуют данные. В операции записи они передаются ведущим устройством по той же линии, в операции чтения устройство их посылает по линии MISO. На время всей транзакции ведущее устройство сохраняет активное состояние линии SS#, число требуемых синхроимпульсов зависит от формата команды.

Интерфейс последовательной шины ІІC, введенной фирмой Philips как простое и дешевое средство сопряжения микросхем бытовой электроники, стал фактическим промышленным стандартом для устройств различного назначения. Он очень удобен для обмена небольшими объемами данных, например, для конфигурации различных устройств. Спецификация шины ІІС определяет протокол двусторонней передачи данных по двум сигнальным линиям. Приложения этого протокола могут быть самыми разнообразными, информационная «начинка» зависит от конкретных применений.

Шина Inter 1C Bus (шина соединения микросхем) — синхронная последовательная шина, обеспечивающая двустороннюю передачу данных между подключенными устройствами. Шина ориентирована на 8-битные передачи. Передача данных может быть как одноадресной, к выбранному устройству, так и широковещательной. Уровни сигналов — стандартные, совместимые с широко распространенной логикой ТТЛ, КМОП, N-МОП, как с традиционным питанием +5 В, так и с низковольтным (3,3 В и ниже). Микросхемы с интерфейсом ІІС, как правило, имеют аппаратную поддержку протокольных функций. Протокол позволяет взаимодействовать на одной шине устройствам с различным быстродействием интерфейса. Требования к временным параметрам сигналов весьма свободные, так что на компьютерах и микроконтроллерах, не имеющих аппаратной поддержки шины ІІС, ее протокол может быть реализован даже чисто программно.

Шина ІІС использует режимы: Standard Mode (S) — со скоростью 0-100 Кбит/с; Fast Mode (F) — со скоростью 0-400 Кбит/с и связанные с ним изменения требований к форме сигнала и фильтрации помех. Также здесь веден режим 10-битной адресации устройств. Версия 2.1 вышла в 2000 г., когда интерфейс ІІС стал фактически промышленным стандартом, использующимся в большом числе различных ИС. Здесь появился новый высокоскоростной режим — High speed (Hs), — в котором скорость передачи может достигать 3,4 Мбит/с. Прежние режимы работают одинаково, и для них используют обобщенное обозначение F/S. В этой версии пересмотрены требования к уровням и форме сигналов с учетом высоких скоростей и возможности подключения низковольтных устройств с питанием 2 В и ниже.

Интерфейс ІІС использует две сигнальные линии: данных SDA (Serial Data) и синхронизации SCL (Serial Clock). В обменах участвуют два устройства — ведущее (master) и ведомое (slave). Ведущее и ведомое устройства могут выступать в роли и передатчика, и приемника данных. Протокол допускает наличие на шине нескольких ведущих устройств и имеет простой механизм арбитража (разрешения коллизий).

Протокол обмена для обычных устройств F/S иллюстрирует рис.1. Обе сигнальные линии имеют нагрузочные резисторы, «подтягивающие» их уровень к напряжению питания. На устройстве к каждой линии подключен приемник и передатчик типа «открытый коллектор» («открытый сток»), у ведомого устройства передатчик на линии SCL не обязателен. Все одноименные передатчики соединяются по схеме «Монтажное И»: уровень в линии будет высоким, если все передатчики пассивны, и низким, если хоть у одного передатчика выходной транзистор открыт. В покое (Idle, исходное состояние шины) все передатчики пассивны. Синхронизацию задает ведущее устройство, но ведомое, если оно не имеет достаточного быстродействия, может замедлять обмен данными.

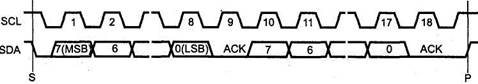

Рис. 1. Протокол передачи данных I2C

Начало любой передачи — условие Start — инициируется ведущим устройством, убедившимся в том, что шина свободна (высокий уровень сигналов SCL и SDA). Условие Start (на диаграммах обозначается как S)— перевод сигнала SDA из высокого в низкий при высоком уровне SCL Завершается операция переводом сигнала SDA из низкого уровня в высокий при высоком уровне SCL — условие Stop (обозначается как Р), также вводящееся ведущим устройством. При передаче данных состояние линии SDA может изменяться только при низком уровне SCL, биты данных считаются действительными во время высокого уровня SCL Каждая посылка данных состоит из 8 бит данных, формируемых передатчиком (старший бит — MSB — передается первым), после чего передатчик на один такт освобождает линию данных для получения подтверждения. Приемник во время девятого такта формирует бит подтверждения Ack, по которому передатчик убеждается, что его «услышали». После передачи бита подтверждения ведомое устройство может задержать следующую посылку, удерживая линию SCL на низком уровне. Ведомое устройство в режимах F/S может замедлить передачу по шине и на уровне приема каждого бита, удерживая SCL на низком уровне после его спада, сформированного передатчиком. Поэтому ведущее устройство должно генерировать сигнал SCL не «вслепую», а анализируя состояние линии SCL: сняв этот сигнал, новый импульс (открытие ключа передатчика) оно имеет право вводить, лишь убедившись, что сигнал SCL вернулся в пассивное состояние (высокий уровень). В противном случае синхронизация будет потеряна. Сигнал SCL может быть растянут и другим устройством, пытающимся захватить шину в это же время. Тактовый сигнал SCL не обязательно будет равномерным: время его нахождения на низком уровне будет определяться максимальным временем, в котором его захочет удержать самое медленное из устройств, участвующих в данном обмене (даже и конфликтующих); время нахождение на высоком уровне будет определяться самым быстрым из конфликтующих ведущих устройств.

Коллизия (конфликт) на шине может возникнуть, когда два (или более) устройства, убедившись в покое шины, одновременно (или почти одновременно) инициируют обмен данными. Все они управляют линиями SCL и SDA и наблюдают за ними. Если устройство, передающее единицу (высокий уровень), в данном такте на линии SDA видит ноль (низкий уровень), оно должно признать свой проигрыш в конфликте и освободить линии SCL и SDA. Выигравшее устройство даже и не заметит проигравших конкурентов и продолжит работу. Арбитраж может закончиться в любом месте посылки, формируемой ведущим устройством. Искажения информации, передаваемой выигравшим устройством, не происходит (приятное отличие от коллизий в сетях Ethernet).

Бит подтверждения АСК, вводящийся в конце каждого байта устройством-приемником, выполняет несколько функций. Когда передатчиком является ведущее устройство, приемник (ведомый) должен вводить нулевой бит АСК, свидетельствующий о нормальном получении очередного байта. Единичный бит АСК (нет подтверждения) в ответ на посылку адреса свидетельствует об отсутствии адресованного ведомого устройства на шине или его занятости внутренними процессами. Отсутствие подтверждения байта данных свидетельствует о занятости устройства. Не получив бита подтверждения, ведущее устройство должно сформировать условие Stop, чтобы освободить шину. Когда ведущее устройство является приемником, оно должно формировать нулевой бит АСК после каждого принятого байта, кроме последнего. Единичный бит АСК в этом случае является указанием ведомому устройству на окончание передачи — оно теперь должно освободить линии SDA и SCL, чтобы ведущее устройство смогло сформировать условие Р или Sr.

На вышеописанной физической основе строится протокол обмена данными по IIC. Каждое ведомое устройство имеет свой адрес, уникальный на шине. В начале любой передачи ведущее устройство после условия S или Sг посылает адрес ведомого устройства или специальный адрес. Ведомое устройство, опознавшее свой адрес после условия Start, становится выбранным; оно обязано ответить подтверждением на адрес и последующие сигналы со стороны ведущего устройства, до получения условия Р или Sr. В первоначальном варианте интерфейса разрядность адреса устройства составляла 7 бит, впоследствии был введен и режим 10-битной адресации, совместимый с 7-битной. На одной шине могут присутствовать устройства и с 7-битной, и 10-битной адресацией.

При 7-битной адресации в первом байте после S (Sr) ведущее устройство передает 7 бит адреса (А[6:0] в битах [7:1]) и признак операции RW (в бите О RW=1 — чтение, RW=0 — запись). Адреса ведомых устройств не должны попадать в области, указанные в таблице. Диапазоны адресов устройств различных типов централизованно выдаются изготовителям микросхем фирмой Philips. Для микросхем памяти, например, 7-битный адрес содержит две части: старшие 4 бита А[б:3] несут информацию о типе устройства (EEPROM — 1010), а младшие 3 бита А[0:2] определяют номер устройства данного типа на шине. Микросхемы с интерфейсом IIC имеют три адресных входа, коммутацией которых на логические уровни 1 и 0 задается номер устройства, на который оно «отзовется», а тип устройства «зашит» в нем самом его изготовителем.

Когда ведущее устройство является передатчиком данных, оно в первом байте передает адрес ведомого устройства, при этом RW=0. Выбранное ведомое устройство отзывается подтверждением (АСК=0), после чего ведущее устройство посылает один или несколько байт данных, на каждый из которых ведомое устройство должно отвечать подтверждением.

Когда ведущее устройство является приемником данных, оно в первом байте передает адрес ведомого устройства с RW=1. Выбранное ведомое устройство также отзывается подтверждением (АСК), после чего происходит смена направления передачи и данные уже передает ведомое устройство. Ведущее устройство подтверждает каждый принятый байт, кроме последнего.

Эти передачи могут завершаться условием Р, вводимым ведущим устройством, после которого шину может захватить любое ведущее устройство. Возможны и комбинированные передачи, когда ведущее устройство после окончания очередного обмена не отдает шину, а формирует повторный старт (Sr), после чего обращается к тому же или иному устройству.

Интерфейс 1-Wire[Конструирование устройств на микроконтроллерах. А.В.Белов ст. 161]

Интерфейс JTAG(Joint Test Action Group) предназначен для тестирования сложных логических схем, установленных в целевое устройство. Этот интерфейс описан в стандарте IEEE 1149.1 Boundary Scan Architecture и является последовательным синхронным, но в связи со спецификой назначения значительно отличается от вышеописанных интерфейсов, ориентированных на передачу данных. Интерфейсом JTAG управляет одно устройство-контроллер (чаще всего это ПК с соответствующим интерфейсным адаптером), к которому может быть подключено несколько тестируемых устройств. Ниже перечислены сигналы интерфейса JTAG.

♦ ТСК (Test Clock) — сигнал синхронизации последовательных данных; генерируется контроллером. Частота синхронизации может достигать 16 МГц.

♦ TMS (Test Mode Select) — сигнал выбора тестового режима. Генерируется контроллером.

♦ TDI (Test Data Input) — входные данные, принимаемые устройством в последовательном двоичном коде (младшим битом вперед).

♦ ТDО (Test Data Output) — выходные данные, передаваемые устройством в последовательном двоичном коде.

♦ TRST (Test Logic Reset) — необязательный сигнал сброса логики интерфейсного порта, генерируемый контроллером.

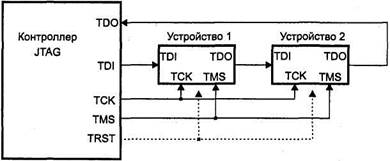

Эти сигналы (все однонаправленные), имеющие обычные логические уровни, образуют тестовый порт ТАР (Test Access Port), через который тестируемое устройство подключается к тестирующему оборудованию (контроллеру). В задачу тестирующего оборудования входит формирование тестовых сигналов по программе тестирования, определенной разработчиком тестируемого устройства, и сравнение полученных результатов с эталонами. Один и тот же контроллер и порт могут использоваться для тестирования любого числа устройств, поддерживающих JTAG. Для этого устройства своими портами ТАР соединяются в цепочку (рис. 6). Стандартизованный логический формат позволяет контроллеру независимо общаться с каждым из устройств цепочки.

Рис. 6. Цепочка устройств с интерфейсом JTAG

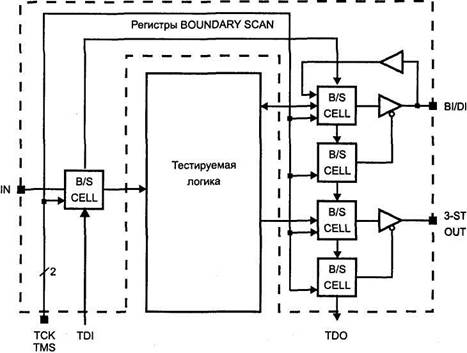

Идею тестирования любой цифровой схемы иллюстрирует рис.7, на котором показана условная цифровая система, имеющая входные, выходные (возможно, с третьим состоянием) и двунаправленные сигналы. Ячейки тестирования B/S врезаются между реальными внешними выводами устройства и собственно логическим устройством, то есть располагаются на логической границе (boundary) устройства. ТАР-контроллер способен сканировать ячейки — управлять ими и считывать с них информацию. Отсюда и пошло название Boundary Scan, которое можно перевести как «периферийное сканирование». При включенном тестовом режиме ТАР-контроллер может логически отсоединить сигналы от внешних выводов, задавать входные воздействия и считывать результаты — собственно, это все, что необходимо для тестирования последовательностных схем. Прелесть JTAG заключается в том, что независимо от сложности устройства оно тестируется с помощью всего лишь четырех сигналов — все сложности прячутся в достаточно простые ячейки, «окутывающие» его сигнальные выводы.

Рис. 11.7. Включение ячеек сканирования

Тестовая логика, встраиваемая в устройство, поддерживающее JTAG, состоит из следующих элементов:

♦ тестовый порт ТАР (четыре интерфейсных сигнала);

♦ ТАР-контроллер, управляющий тестовыми регистрами;

♦ регистр инструкций IR (Instruction Register), который принимает последовательный код со входа TDI (код инструкции используется для выбора исполняемой тестовой операции или регистра тестовых данных, к которым производится обращение);

♦ регистры тестовых данных, из которых любое устройство должно иметь три обязательных регистра: ВPR (Bupas Register), DID (Device Identification Register) и BSR (Boundary Scan Register).

Регистры инструкций и данных представляют собой независимые сдвиговые регистры, соединенные параллельно. На их входы (старшие биты) приходит сигнал TDI, с выходов (младшие биты) снимается сигнал ТОО. По каждому положительному перепаду данные продвигаются на один бит.

Регистр ВРR имеет длину в один бит. Он используется как кратчайший обходной путь для последовательных данных, когда остальные регистры не участвуют в обмене.

Контроллер тестового порта (TAP-controller) представляет собой синхронный конечный автомат, изменяющий состояние по фронту сигнала ТСК и по включению питания.

Для интерфейса JTAG существует специальный язык описания устройств BSDL (Boundary Scan Description Language). Состав и порядок следования информаци онных и управляющих ячеек в сдвиговом регистре данных специфичен для каждого устройства и сообщается его разработчиками.

Интерфейс JTAG используется не только для тестирования, но и для программирования различных устройств, в том числе и энергонезависимой памяти микроконтроллеров. Контакты для сигналов JTAG имеются на шине PCI, однако в их использовании единообразия не наблюдается (либо остаются неподключенными, либо соединяются для организации цепочки). Интерфейс JTAG имеется в современных процессорах; здесь он позволяет не только тестировать сам процессор (это не представляет особого прикладного интереса), но и организовать зондовый режим отладки. Зондовый режим является мощным средством отладки системного программного обеспечения; обычный процессор, связанный с тестовым контроллером интерфейсом JTAG, превращается во внутрисхемный эмулятор — мечту разработчика системного ПО.

Интерфейс CAN (промышленная сеть реального времени) представляет собой сеть с общей средой передачи данных. Это означает, что все узлы сети одновременно принимают сигналы передаваемые по шине. Невозможно послать сообщение какому-либо конкретному узлу. Все узлы сети принимают весь трафик передаваемый по шине. Однако, CAN-контроллеры предоставляют аппаратную возможность фильтрации CAN-сообщений.

Каждый узел состоит из двух составляющих. Это собственно CAN контроллер, который обеспечивает взаимодействие с сетью и реализует протокол, и микропроцессор (CPU).

Рис. 1. Топология сети CAN.

CAN контроллеры соединяются с помощью дифференциальной шины, которая имеет две линии - CAN_H (can-high) и CAN_L (can-low), по которым передаются сигналы. Логический ноль регистрируется, когда на линии CAN_H сигнал выше, чем на линии CAN_L. Логическая единица - в случае когда сигналы CAN_H и CAN_L одинаковы (отличаются менее чем на 0.5 В). Использование такой дифференциальной схемы передачи делает возможным работу CAN сети в очень сложных внешних условиях. Логический ноль - называется доминантным битом, а логическая единица - рецессивным. Эти названия отражают приоритет логической единицы и нуля на шине CAN. При одновременной передаче в шину лог. нуля и единицы, на шине будет зарегестрирован только логический ноль (доминантный сигнал), а логическая единица будет подавлена (рецессивный сигнал).

Дата добавления: 2017-01-29; просмотров: 1587;