Тема 2.3. Программный ПЛК, рабочий цикл и время реакции контроллера

Программные приложения, имитирующие технологию ПЛК на компьютере (оснащенном платами ввода-вывода), получили название программный ПЛК (soft PLC). Программная эмуляция

ПЛК удобна тем, что благодаря наличию многозадачной операционной системы можно совместить в одном месте контроллер, среду программирования и систему диспетчерского управления.

Существенный минус такого решения — большое время выхода на рабочий режим после включения питания или зависания компьютера. Особенно опасно, если перезапуск произвел «сторожевой таймер» в автоматическом режиме, в то время как состояние исполнительных механизмов не соответствует исходным позициям. Загрузка операционной системы может отнимать несколько минут, все это время система оказывается неуправляемой. Для ПЛК время «холодного» запуска измеряется миллисекундами.

Для достижения сравнимых с ПЛК технических показателей по надежности компьютер, конечно, должен быть промышленного исполнения (на базе магистралей РС/104 или УМЕ), а не дешевый офисный «по пате».

Задачи управления требуют непрерывного циклического контроля. В любых цифровых устройствах непрерывность достигается за счет применения дискретных алгоритмов, повторяющихся через достаточно малые промежутки времени. Таким образом, вычисления в ПЛК всегда повторяются циклически. Одна итерация,включающая замер, обсчет и выработку воздействия, называется рабочим циклом ПЛК. Выполняемые действия зависят от значения входов контроллера, предыдущего состояния и определяются

пользовательской программой.

По включению питания ПЛК выполняет самотестирование и настройку аппаратных ресурсов, очистку оперативной памяти данных (ОЗУ), контроль целостности прикладной программы пользователя. Если прикладная программа сохранена в памяти, ПЛК переходит к основной работе, которая состоит из постоянного повторения последовательности действий, входящих в рабочий цикл.

Рабочий цикл ПЛК состоит из нескольких фаз.

1. Начало цикла.

2. Чтение состояния входов.

3. Выполнение кода программы пользователя.

4. Запись состояния выходов.

5. Обслуживание аппаратных ресурсов ПЛК.

6. Монитор системы исполнения.

7. Контроль времени цикла.

8. Переход на начало цикла.

В самом начале цикла ПЛК производит физическое чтение входов. Считанные значения размещаются в области памяти входов. Таким образом, создается полная одномоментная зеркальная копия значений входов.

Далее выполняется код пользовательской программы. Пользовательская программа работает с копией значений входов и выходов, размещенной в оперативной памяти. Если прикладная программа не загружена или остановлена, то данная фаза рабочего цикла, естественно, не выполняется. Отладчик системы программирования имеет доступ к образу входов-выходов, что позволяет управлять выходами вручную и проводить исследования работы датчиков.

После выполнения пользовательского кода физические выходы ПЛК приводятся в соответствие с расчетными значениями (фаза 4).

Обслуживание аппаратных ресурсов подразумевает обеспечение работы системных таймеров, часов реального времени, оперативное самотестирование, индикацию состояния и другие аппаратно-зависимые задачи.

Монитор системы исполнения включает большое число функций, необходимых при отладке программы и обеспечении взаимодействия с системой программирования, сервером данных и сетью. В функции системы исполнения обычно включается: загрузка кода программы в оперативную и электрически перепрограммируемую память, управление последовательностью выполнения задач, отображение процесса выполнения программ, пошаговое выполнение, обеспечение просмотра и редактирования значений переменных, фиксация и трассировка значений переменных, контроль времени цикла и т. д.

Пользовательская программа работает только с мгновенной копией входов. Таким образом, значения входов в процессе выполнения пользовательской программы не изменяются в пределах одного рабочего цикла. Это фундаментальный принцип построения ПЛК сканирующего типа. Такой подход исключает неоднозначность алгоритма обработки данных в различных его ветвях. Кроме того, чтение копии значения входа из ОЗУ выполняется значительно быстрее, чем прямое чтение входа. Аппаратно чтение входа может быть связано с формированием определенных временных интервалов, передачей последовательности команд для конкретной микросхемы или даже запросом по сети.

Если заглянуть глубже, то нужно отметить, что не всегда работа по чтению входов полностью локализована в фазе чтения входов. Например, АЦП обычно требуют определенного времени с момента запуска до считывания измеренного значения. Часть работы системное программное обеспечение контроллера выполняет по прерываниям. Грамотно реализованная система исполнения нигде и никогда не использует пустые циклы ожидания готовности аппаратуры. Для прикладного программиста все эти детали не важны. Существенно только то, что значения входов обновляются автоматически исключительно в начале каждого

рабочего цикла.

Общая продолжительность рабочего цикла ПЛК называется временем сканирования. Время сканирования в значительной степени определяется длительностью фазы кода пользовательской программы. Время, занимаемое прочими фазами рабочего цикла, практически является величиной постоянной. Для задачи среднего объема в ПЛК с системой исполнения CoDeSys время распределится примерно так: 98% пользовательская программа, 2% все остальное.

Существуют задачи, в которых плавающее время цикла существенно влияет на результат, например это автоматическое регулирование. Для устранения этой проблемы в развитых ПЛК предусмотрен контроль времени цикла. Если отдельные ветви кодауправляющей программы выполняются слишком быстро, в рабочий цикл добавляется искусственная задержка. Если контроль времени цикла не предусмотрен, подобные задачи приходится решать исключительно по таймерам.

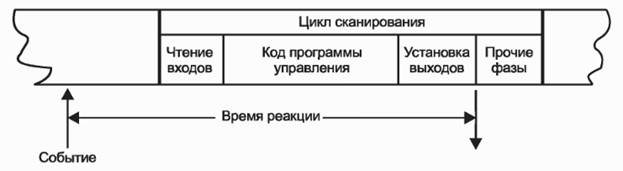

Время реакции — это время с момента изменения состояния системы до момента выработки соответствующей реакции. Очевидно, для ПЛК время реакции зависит от распределения моментов возникновения события и начала фазы чтения входов. Если изменение значений входов произошло непосредственно перед фазой чтения входов, то время реакции будет наименьшим и равным времени сканирования (рис. 1.5). Худший случай, когда изменение значений входов происходит сразу после фазы чтения входов. Тогда время реакции будет наибольшим, равным удвоенному времени сканирования минус время одного чтения входов.

Иными словами, время реакции ПЛК не превышает удвоенного времени сканирования.

Рис. 2.2. Время реакции ПЛК

Помимо времени реакции ПЛК, существенное значение имеет время реакции датчиков и исполнительных механизмов, которое также необходимо учитывать при оценке общего времени реакции системы.

Существуют ПЛК, которые реализуют команды непосредственного доступа к аппаратуре входов и выходов, что позволяет обрабатывать и формировать отдельные сигналы с длительностью меньшей длительности рабочего цикла.

Для уменьшения времени реакции сканирующих контроллеров алгоритм программы разбивается на несколько задач с различным периодом исполнения. В наиболее развитых системах пользователь имеет возможность создавать отдельные программы, исполняемые по прерыванию, помимо кода, исполняемого в рабочем цикле. Такая техника позволяет ПЛК существенно форсировать ограничение реакции временем сканирования при небольшом количестве входов, требующих сверхскоростной реакции.

Время цикла сканирования является базовым показателем быстродействия ПЛК. При измерении времени рабочего цикла пользовательская программа должна содержать 1К логических команд. Для ПЛК, поддерживающих стандарт МЭК 61131-3, используют команды на языке IL. Иногда изготовители приводят несколько значений времени цикла, полученных при работе с переменными различной разрядности.

Ориентировочно о скорости обработки различных типов данных можно судить по тактовой частоте и разрядности центрального процессора. Хотя нет ничего удивительного в том, что восьмиразрядные ПЛК не редко оказываются быстрее 32-разрядных при выполнении битовых операций. Объясняется это тем, что в 8-разрядиых микропроцессорах более распространена аппаратная поддержка работы с битами. Так, в PC-совместимых процессорах для выделения бита приходится использовать логические команды и циклический сдвиг.

Дата добавления: 2016-07-09; просмотров: 8266;