Суммирующие двоичные счетчики

.

В таких счетчиках поступление на вход очередного импульса вызывает увеличение на одну единицу хранимого в счетчиках числа.

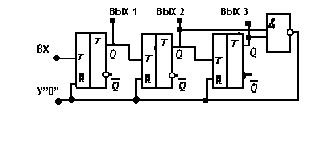

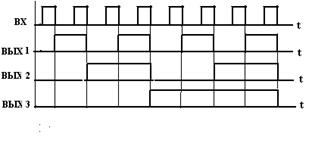

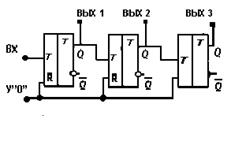

Схема трехразрядного двоичного счетчика, построенного на Т-триггерах,. показана на рис.8.1. Используются триггеры, срабатывающие “по спаду” входного сигнала. При появлении импульса на входе на выходе триггера устанавливается новое состояние, противоположное предыдущему. С каждым входным импульсом сумма увеличивается на единицу. Анализ принципа действия схемы показывает, что суммирование производится в двоичной системе счисления. Выходной сигнал первого триггера соответствует младшему разряду суммы, т.е. ему соответствует весовой коэффициент 20, для следующего триггера –21 и т.д. Нарастание числа продолжается до тех пор, пока после очередного входного импульса в счетчике не устанавливается исходное состояние 00... 0, после чего счет ведется сначала. Временная диаграмма одного цикла работы счетчика приведена на рис .8.2. Для трехразрядного счетчика цикл заканчивается после восьмого импульса на входе.

Можно построить схему трехразрядного счетчика с циклом счета менее восьми, не кратным степени двойки. Для этого используются цепи обратных связей, формирующие сигнал установки счетчика в исходное состояние после заданного входного импульса. Пример подобной схемы с циклом счета , равным шести, приведен на рис. 8.3.

Можно построить схему трехразрядного счетчика с циклом счета менее восьми, не кратным степени двойки. Для этого используются цепи обратных связей, формирующие сигнал установки счетчика в исходное состояние после заданного входного импульса. Пример подобной схемы с циклом счета , равным шести, приведен на рис. 8.3.

Сумматоры

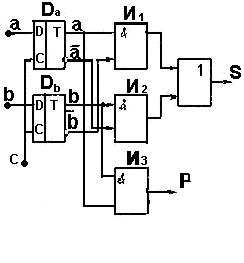

Сумматором называют устройство, осуществляющее арифметическое сложение двоичных чисел. Сумматор является одним из основных элементов ЭВМ, выполняющим арифметические операции. Сложение многоразрядных двоичных чисел производится однотипными действиями, осуществляемыми в каждом разряде с помощью одноразрядного двоичного сумматора. Для сложения многоразрядных двоичных чисел используют многоразрядные сумматоры, которые в зависимости от ввода чисел делятся на две группы: последовательного и параллельного действия. Сумматор последовательного действия складывает разряды суммируемых чисел последовательно, начиная с младших . Для сумматора последовательного действия характерно малое количество элементов, однако он обладает низким быстродействием. Сумматор параллельного действия выполняется многоразрядным , его каждый разряд образован одноразрядным сумматором. Сложение многоразрядных двоичных чисел производится однотипными действиями, осуществляемыми в каждом разряде с помощью одноразрядных двоичных сумматоров. Схема комбинационного одноразрядного сумматора для сложения младших разрядов двух чисел приведена на рис. 9.1. В двоичном одноразрядном сумматоре путем сложения по модулю 2 определяется сумма чисел в каждом

разряде. Операция сложения выполняется путем подачи соответствующих разрядов

|

двух D-триггеров.

Логика работы сумматора иллюстрируется таблицей 9.1. Проанализируем, как осуществляется операция сложения. Если, например, а = 1, b = 0, то на выходе элемента И1 вырабатывается сигнал a ^`b = 1, а на выходе элемента И2 – 0. В результате на выходе элемента ИЛИ сигнал суммы S = 1. Аналогично формируется сигнал суммы в каждом разряде двоичного одноразрядного сумматора и при других сочетаниях входных чисел. Кроме сигнала суммы на выходе должен формироваться и сигнал переноса в старший разряд, если сумма, полученная при сложении двух чисел, превышает 1. Подобный сигнал формируется на выходе элемента И3.

Дата добавления: 2016-03-15; просмотров: 1411;