Последовательно-параллельные АЦП

Последовательно-параллельные АЦП являются компромиссом между стремлением получить высокое быстродействие и желанием сделать это по возможности меньшей ценой. Они занимают промежуточное положение по разрешающей способности и быстродействию между параллельными АЦП и АЦП последовательного приближения. Последовательно-параллельные АЦП подразделяют на многоступенчатые, многотактные и конвеерные.

Многоступеньчатые АЦП

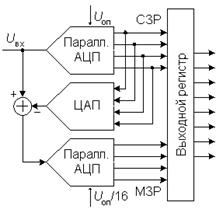

В многоступенчатом АЦП процесс преобразования входного сигнала разделен в пространстве. В качестве примера на рис. 3 представлена схема двухступенчатого 8-разрядного АЦП.

Рис. 3. Структурная схема двухступенчатого АЦП.

Верхний по схеме АЦП осуществляет грубое преобразование сигнала в четыре старших разряда выходного кода. Цифровые сигналы с выхода АЦП поступают на выходной регистр и одновременно на вход 4-разрядного быстродействующего ЦАП. Остаток от вычитания выходного напряжения ЦАП из входного напряжения схемы поступает на вход АЦП2, опорное напряжение которого в 16 раз меньше, чем у АЦП1. Как следствие, квант АЦП2 в 16 раз меньше кванта АЦП1. Этот остаток, преобразованный АЦП2 в цифровую форму представляет собой четыре младших разряда выходного кода. Различие между АЦП1 и АЦП2 заключается прежде всего в требовании к точности: у АЦП1 точность должна быть такой же как у 8-разрядного преобразователя, в то время как АЦП2 может иметь точность 4-разрядного.

Многотактные АЦП

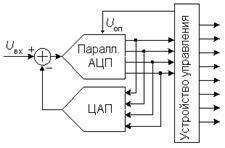

На рис. 4 приведена структурная схема 8-разрядного последовательно-параллельного АЦП, относящегося к типу многотактных. Здесь процесс преобразования разделен во времени.

Рис. 4. Структурная схема двухтактного АЦП.

Преобразователь состоит из 4-разрядного параллельного АЦП, квант h которого определяется величиной опорного напряжения, 4-разрядного ЦАП и устройства управления. Если максимальный входной сигнал равен 2,56 В, то в первом такте преобразователь работает с шагом квантования h1=0,16 В. В это время входной код ЦАП равен нулю. Устройство управления пересылает полученное от АЦП в первом такте слово в четыре старших разряда выходного регистра, подает это слово на вход ЦАП и уменьшает в 16 раз опорное напряжение АЦП. Таким образом, во втором такте шаг квантования h2=0,01 В и остаток, образовавшийся при вычитании из входного напряжения схемы выходного напряжения ЦАП, будет преобразован в младший полубайт выходного слова.

Очевидно, что используемые в этой схеме 4-разрядные АЦП и ЦАП должны обладать 8-разрядной точностью, в противном случае возможен пропуск кодов, т.е. при монотонном нарастании входного напряжения выходной код АЦП не будет принимать некоторые значения из своей шкалы.

Быстродействие рассмотренного многотактного АЦП определяется полным временем преобразования 4-разрядного АЦП, временем срабатывания цифровых схем управления, временем установления ЦАП с погрешностью, не превышающей 0,2...0,3 кванта 8-разрядного АЦП, причем время преобразования АЦП входит в общее время преобразования дважды. В результате при прочих равных условиях преобразователь такого типа оказывается медленнее двухступенчатого преобразователя, рассмотренного выше. Однако он проще и дешевле. По быстродействию многотактные АЦП занимают промежуточное положение между многоступенчатыми АЦП и АЦП последовательного приближения.

Конвеерные АЦП

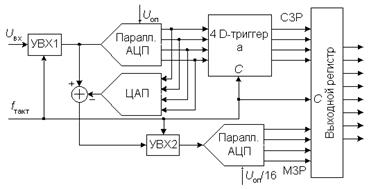

Быстродействие многоступенчатого АЦП можно повысить, применив конвеерный принцип многоступенчатой обработки входного сигнала. В обыкновенном многоступенчатом АЦП (рис. 3) вначале происходит формирование старших разрядов выходного слова преобразователем АЦП1, а затем идет период установления выходного сигнала ЦАП. На этом интервале АЦП2 простаивает. На втором этапе во время преобразования остатка преобразователем АЦП2 простаивает АЦП1. Введя элементы задержки аналогового и цифрового сигналов между ступенями преобразователя, получим конвеерный АЦП, схема 8-разрядного варианта которого приведена на рис. 5.

Рис. 5. Структурная схема конвеерного АЦП.

Роль аналогового элемента задержки выполняет устройство выборки-хранения УВХ2, а цифрового – четыре D-триггера. Триггеры задерживают передачу старшего полубайта в выходной регистр на один период тактового сигнала CLK.

Сигналы выборки, формируемые из тактового сигнала, поступают на УВХ1 и УВХ2 в разные моменты времени. УВХ2 переводится в режим хранения позже, чем УВХ1 на время, равное суммарной задержке распространения сигнала по АЦП1 и ЦАП. Задний фронт тактового сигнала управляет записью кодов в D-триггеры и выходной регистр. Полная обработка входного сигнала занимает около двух периодов CLK, но частота появления новых значений выходного кода равна частоте тактового сигнала. Таким образом, конвеерная архитектура позволяет существенно (в несколько раз) повысить максимальную частоту выборок многоступенчатого АЦП.

Дата добавления: 2016-01-18; просмотров: 1944;