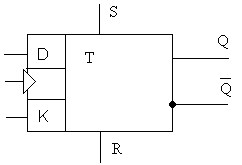

Триггер с прямыми входами

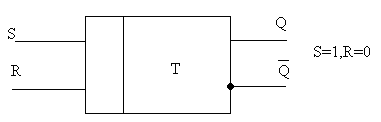

УГО

Активным переключающим сигналом является 1

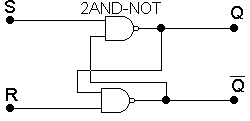

Схема триггера с инверсными входами

Таблица переключения работы триггера с инверсными входами:

| Sn | Rn | Qn-1 | Qn | Q-n |

| - | - | |||

| - | - | |||

Qn=Q-n -запрещенное состояние

Запись 1

Запись 0

хранение

Математическая запись работы триггера:

Qn= SnvR-Qn-1

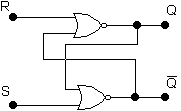

Схема триггера с прямыми входами

3-й учебный вопрос:Синхронный (RSC) триггер.

В синхронных триггерах (RSC,T,D,JK) применяются 2 способа синхронизации:

1)статическая синхронизация, когда импульсом является наличие постоянного напряжения;

2)динамическая синхронизация, когда импульсом является наличие перепада напряжения

Триггеры бывают двухтактные, когда требуется наличие переднего и заднего фронта сигнала:

Двухтактные:1-0-1 задний – передний фронты;

0-1-0 передний – задний фронты.

0-2-0

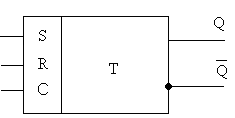

Исследуем RSC триггер с прямыми входами и статической синхронизацией

УГОRSC триггера

СхемаRSC триггера

Примечание: Любой синхронный триггер в отсутствии синхронизации находиться в режиме хранения

Таблица переключений RSC – триггера

| Сn | Sn | Rn | Qn-1 | Qn | Qn^ | Сост.триггера |

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Хранение | ||||||

| Запись «0» | ||||||

| Запись «0» | ||||||

| Запись «1» | ||||||

| Запись «1» | ||||||

| - | - | Запрещ.сост. | ||||

| - | - | Запрещ.сост. |

Лекция 5

1-й учебный вопрос. Триггер задержки(D - триггер)

Назначение: задерживает цифровую информацию на один такт(половина синхронизации С). На выходе триггера выявляется тот логический сигнал(1 или 0), который был на входе на предыдущем интервале.

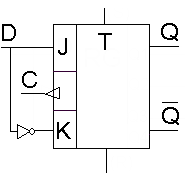

УГО D- триггера

USA

Eвро

R, S – установочные входы

Характеристика установочных входов: асинхронные, приоритетные по отношению к D входу(информационный вход) и предназначенные для начальной установки триггера.

Таблица переключений D – триггера

| Сn | Dn | Qn-1 | Qn |

| Qn-1 | |||

| Qn-1 |

Хранение

Задержка на

1 тактсинхронизации

Примечание: D триггер не имеет запрещенного состояния,однако, если использовать установочные входы, то запрещенное состояние может быть за счет комбинации сигналов на установочных входах.

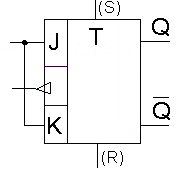

2-й учебный вопрос.Универсальный JK- триггер

Работает, как JK, RS, RSC, D иT триггеры. Поэтому называется универсальным триггером.

УГО(USA)

Таблица переключений

| Сn | Jn | Kn | Qn-1 | Qn | Сост.триггера |

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Хранение | |||||

| Запись «0» | |||||

| Запись «0» | |||||

| Запись «1» | |||||

| Запись «1» | |||||

| Инверсия предыд.сост. | |||||

| Инверсия пред.сост. |

Примечание:D – триггер можно получить,используя JK- триггер при следующем подключении.

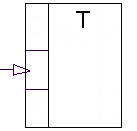

3-й учебный вопросСчетный Т – триггер

Т-триггер синхронный и предназначен для построения счетчиков и делителей частоты.

УГО

Промышленностью Т-триггер не выпускается, но используют режим счетного Т- триггера в D,JK- триггерах, а именно

Таблица переключений Т- триггера

| Сn | Jn | Kn | Qn-1 | Qn |

В Т- триггерах при поступлении синхросигнала на выходе Q триггера сигнал инвертируется, т.е. при поступлении очередного синхроимпульса осуществляется инверсия предыдущего состояния.

Примечание:T –триггер можно собрать с использованием программирования логических интегральных схем(ПЛИС).

Лекция 6 . Регистры памяти и сдвига

Учебные вопросы:

1. Назначение и классификация регистров.

2. Синтез регистров(регистры памяти, сдвига, реверсивные регистры).

1-учебный вопрос. Назначение и классификация регистров.

Регистром называется последовательное цифровое устройство (ПЦУ) предназначенное для хранения небольших объемов информации и преобразование над n-разрядным двоичным кодом.

Регистр представляет собой упорядоченную последовательность триггеров, как правило D- триггеров, число которых соответствует разрядности регистра.

А7 А6 А5 А4 А3 А2А1 А0

Регистр

Аккумул.

Восьми разрядныйрегистр.

Преобразования в регистрах:

1. Обмен информации между регистрами(пересылка данных)

2. Поразрядные логические операции

Логические операции осуществляются поразрядно

Ак

Ак

(рез AND)

^ =

В

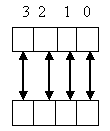

Cдвиг слова влево или вправо

Сдвиг слова влево на 1 разряд-умножение содержимого на 2

Сдвиг слова вправо на 1 разряд- деление содержимого на 2

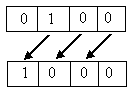

сдвиг на 1 разряд влево

сдвиг на 1 разряд влево

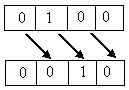

cдвиг вправо на 1 разряд

cдвиг вправо на 1 разряд

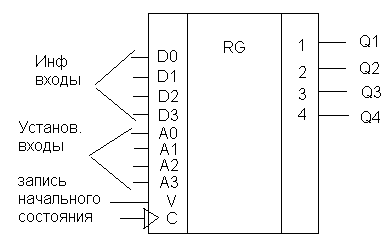

Установка регистра в начальное состояние

УГО

Дата добавления: 2015-10-09; просмотров: 1487;