ОРГАНЫ ЛОГИКИ НА ИМС

Для выполнения ЛЭ используются цифровые ИМС, предназначенные для преобразования входных двоичных сигналов высокого и низкого уровней (1 и 0) в дискретные выходные сигналы. По выполняемым функциям цифровые микросхемы можно подразделить на схемы, выполняющие логические операции И-НЕ либо ИЛИ-НЕ, И, НЕ, ИЛИ (логические схемы), и на схемы функциональных узлов (триггеры, счетчики, дешифраторы и др.). Эта группа ИМС выполняется в виде различных сочетаний типовых логических схем. На чертежах микросхемы изображаются и обозначаются так же, как и соответствующие им логические элементы (см. рис.2.72).

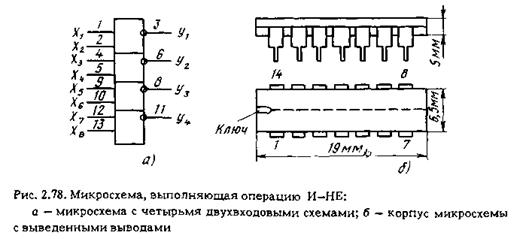

Как правило, одна микросхема обычно состоит из нескольких однотипных логических схем. При этом каждая схема имеет выведенные из корпуса входы и выходы и два общих для всех схем вывода для подсоединения источника питания (рис.2.78, а). При таком исполнении каждая из

схем, входящих в микросхему, может использоваться как самостоятельный ЛЭ в разных частях логической схемы РЗ.

Свойства логических микросхем характеризуются параметрами, которые приводятся для разных типовых микросхем в справочниках по ИМС. Для устройства РЗ наиболее важными являются следующие параметры:

помехоустойчивость, определяемая значением наибольшего допустимого напряжения UПОМ mах, поступающего на вход микросхемы, при котором не происходит ее переключения из исходного состояния в состояние срабатывания и наоборот;

мощность, потребляемая от источника питания при действии и недействии микросхемы;

нагрузочная способность микросхемы, характеризуемая числом микросхем, аналогичных рассматриваемой, которые можно подключить к ее выходу;

коэффициент объединения по входу, определяющий наибольшее число входных сигналов, которые можно допустить для данной микросхемы.

Промышленность выпускает цифровые ИМС в виде серий, содержащих по несколько различных по функциям микросхем (до 10 и более). Серии различаются по составу входящих в них микросхем и по их параметрам. Схемы одной серии имеют одинаковое конструктивно-технологическое исполнение и могут соединяться последовательно друг с другом (выход с входом) без согласующих элементов. Каждая серия имеет базовую логическую схему, на основе которой выполняются все микросхемы, входящие в серию.

В логических и функциональных устройствах РЗ, выпускаемых и подготовляемых к выпуску заводом ЧЭАЗ, используются микросхемы в основном серий К511 и К155 на биполярных транзисторах, а также К176 на КМОП. Логические микросхемы первых двух серий выполняются на базовой схеме И-НЕ. Серия МС К176 использует схемы, выполняющие операции И либо ИЛИ.

Все разновидности этих схем имеют общую структуру, приведенную на рис.2.76, в, г. Они состоят из двух основных элементов (схем): одного – выполняющего операцию И, второго – выполняющего операцию НЕ. Последняя всегда реализуется по схеме транзисторного инвертора, выполняющего одновременно функцию усиления выходного сигнала и формирования уровня выходного сигнала. Операция И обычно выполняется на резисторах, диодах или транзисторах.

Исходя из элементов, на базе которых выполняются логические элементы И или НЕ, логические схемы подразделяются на резисторно-транзисторные ИМС, диодно-транзисторные логические устройства (ДТЛ) и транзисторно-транзисторные (ТТЛ).

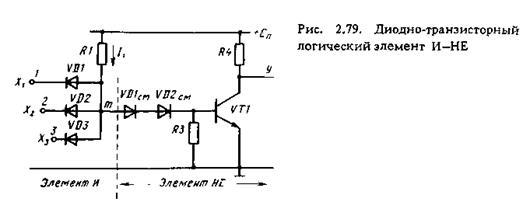

Диодно-транзисторный ЛЭ И-НЕ. На рис.2.79 показан ЛЭ на микросхеме ДТЛ. Схема состоит из элементов И, НЕ и смещения. Элемент И состоит из трех диодов VD1, VD2, VD3 (по числу входных сигналов) и резистора R1, через который на выход схемы И (в точке m) подается опорное напряжение положительного знака + ЕП от источника питания.

Элемент НЕ выполнен в виде однокаскадного инвертора на транзисторе VT1, на базу которого подается сигнал (напряжение UY) с выхода схемы И. Он преобразуется транзистором VT1 в выходной сигнал UВЫХ (точка Y) с инвертированием его уровня. В цепь базы VT1 включены два диода, называемые диодами смещения VD1CM и VD2CM. Эти диоды увеличивают пороговое напряжение, необходимое для открытия транзистора VT1 и срабатывания ЛЭ микросхемы, повышая этим отстройку элемента микросхемы от помех:

где Um и Uэ.бVT1 – напряжения открытия диода и эмиттерного перехода VT1 соответственно.

Напряжение, необходимое для открытия кремниевых диодов, UOT.Д = 0,5 ÷ 0,6 В, а для открытия транзистора Uот.VT1 = 0,4 ÷ 0,5 В. Следовательно, Um = 1,4 ÷ 1,7 В, а при отсутствии диодов U'm = 0,5 ÷ 0,6 В.

Допустим, что на всех входах одновременно появились единичные сигналы в виде напряжения высокого уровня Е1ВХ ≈ ЕП. Тогда на выходе элемента И (в точке m) возникает напряжение U1m > 0. Параметры схемы (R1, R3, ЕП) подбираются так, чтобы это напряжение превосходило напряжение (1,2–1,4 В), необходимое для открытия диодов смещения и появления на базе VT1 потенциала Uб = I1R3, достаточного для открытия транзистора инвертора для перехода его в режим полного насыщения. При этом на выходе схемы И-НЕ в точке Y установится малое напряжение нулевого уровня U0ВЫХ = 0,2 ÷ 0,4 В. Таким образом, при появлении единичных сигналов на всех входах рассматриваемой схемы на ее выходе появляется сигнал нулевого уровня. Это означает, что микросхема выполняет логическую операцию И-НЕ.

Для возврата схемы в исходное состояние необходимо подать хотя бы на один из диодов (например, на вход 3) сигнал на уровне логического 0, т. е. напряжение U0ВХ3, близкое к нулю. Диод VD3 открывается, и потенциал выхода И (точка т) скачком изменяется от единичного значения до нулевого (от U1m до U0m ). При этом диоды смещения закрываются, ток и напряжение базы VT1 падают до нуля – транзистор закрывается.

При закрытом транзисторе потенциал на выходе органа И-НЕ (в точке Y) увеличивается скачком до высокого уровня. Как видно из рис.2.79, при отсутствии нагрузки  ,а при наличии нагрузки RH

,а при наличии нагрузки RH  . Таким образом, при наличии нулевого сигнала на одном, на нескольких или на всех входах ЛЭ И-НЕ переходит в состояние недействия. При негативной логике, когда в качестве сигнала, приводящего в действие логическую схему, принимается нулевой (а не единичный) уровень входного сигнала, рассмотренная схема будет выполнять операцию ИЛИ-НЕ. Достоинством логических схем ДТЛ является относительная простота.

. Таким образом, при наличии нулевого сигнала на одном, на нескольких или на всех входах ЛЭ И-НЕ переходит в состояние недействия. При негативной логике, когда в качестве сигнала, приводящего в действие логическую схему, принимается нулевой (а не единичный) уровень входного сигнала, рассмотренная схема будет выполнять операцию ИЛИ-НЕ. Достоинством логических схем ДТЛ является относительная простота.

Органы логики И-НЕ на транзисторно-транзисторных ИМС. В микросхемах ТТЛ элемент И, входящий в состав схемы И-НЕ, может выполняться либо на обычных транзисторах ИМС, либо на интегральных транзисторах особой конструкции – многоэмиттерных, которые имеют до восьми эмиттеров, общую базу и один коллектор. База состоит из активных областей (их число равно числу эмиттеров), образующих переходы база-эмиттер и пассивных участков, разделяющих эти переходы для исключения их воздействия друг на друга. Преимуществом многоэмиттерных транзисторов является уменьшение занимаемой ими площади и улучшение некоторых параметров ИМС. В схемах ТТЛ для построения элемента И в основном применяются многоэмиттерные транзисторы. Обычные транзисторы (с одним эмиттером) используются для выполнения операции И в схемах ТТЛ лишь для получения микросхем с повышенной помехоустойчивостью (с высоким порогом переключения). Микросхемы на обычных транзисторах получают питание от источников до 15-20 В вместо 5-6 В, являющихся предельными для многоэмиттерных транзисторов. Чем выше напряжение питания ЕП, тем большим может быть порог переключения, т.е. входное напряжение единичного уровня U1ВХ, при котором происходит переключение логического элемента. С увеличением ЕП повышается уровень допустимой помехи. Высокопороговые микросхемы получили широкое применение в РЗ.

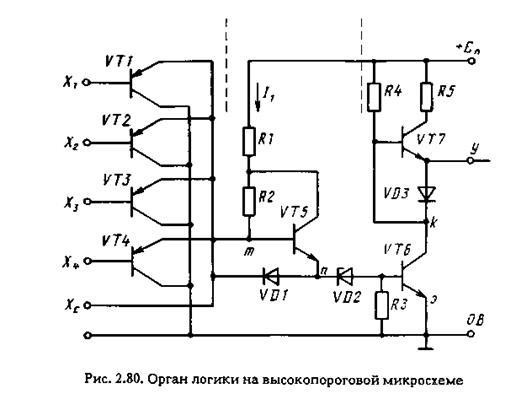

Органы логики на высокопороговых микросхемах. На рис.2.80 приведена высокопороговая микросхема с четырьмя входами. Элемент И микросхемы выполнен на транзисторах типа р-n-р, включаемых по схеме эмиттерного повторителя. Число транзисторов равно числу входных сигналов. Входные сигналы X1–Х4 приходят на базу соответствующего транзистора (VT1–VT4). Выходной сигнал возникает между эмиттером транзистора и нулевой шинкой. Эмиттеры соединены между собой в точке т, которая является выходом элемента И. На эту точку через R1 и R2 подается опорное напряжение ЕП = + 15 В. Коллекторы всех транзисторов объединены и подключены к общей шинке нулевого потенциала.

Элемент НЕ выполнен с помощью транзисторного инвертора в виде двухкаскадного усилителя на VT6 и VT7. Инвертирование сигнала, получаемого с элемента И, осуществляется VT6, а дополнительное усиление мощности выходного сигнала VT7, который включается по схеме эмиттерного повторителя. Такое включение позволяет также уменьшить выходное сопротивление схемы И-НЕ. В состав инвертора входят R3-R5 и диод VD3. Кроме элементов И и НЕ в схеме предусмотрены транзистор VT5 и стабилитрон VD2, который устанавливается вместо диодов смещения для повышения порога срабатывания и помехоустойчивости. Для прохождения сигнала, открывающего VT6 и вызывающего срабатывание ЛЭ, входное напряжение должно стать больше обратного напряжения, открывающего VD2. У кремниевого стабилитрона это напряжение Uоб.ст = 6,8 ÷ 7 В, что и позволяет повысить уровень допустимых помех.

Транзистор VT5 предназначен для усиления тока, поступающего на базу инвертора VT6, до значения, обеспечивающего его переход в режим полного насыщения, что необходимо для получения на выходе .схемы (на зажиме Y) напряжения UВЫХ на уровне логического нуля (0,5-0,6 В).

Для открытия транзистора VT6 на выходе элемента И в точке т не должно появиться напряжение, равное или большее суммы напряжений, необходимых для открытия VT5, VD2 и VT6, т.е. Um = 0,5 + 7 + 0,5 = 8 В. Это напряжение является порогом чувствительности рассматриваемой микросхемы (UПОР = Um). Входное напряжение, необходимое для срабатывания ЛЭ, UВХ.СР должно быть больше порогового напряжения UПОР. Нормальное значение UВХ, соответствующее уровню логической 1, целесообразно принять равным 10-12 В с некоторым запасом по отношению к значению UВХ.СР, учитывая возможность его понижения при колебании напряжения питания. Если единичное напряжение на входе (в рассматриваемом случае на Х2) станет меньше своего нормального значения (12-13 В), то до тех пор, пока U'ВХ остается больше UПОР (8 В), VT2 остается закрытым. При уменьшении UBX ниже UПОР (8 В) элемент переключается, транзистор VT2 начинает открываться. По мере уменьшения U0BX (которое при U < 8 В соответствует нулевому уровню) входной ток I0BX возрастает и при U0BX ≈ 0 достигает максимума, VT2 переходит в режим насыщения, при котором I0BX.mах = 0,1 ÷ 0,15 мА.

Действие микросхемы. Если на все входы микросхемы (рис.2.80) поданы единичные сигналы в виде напряжения положительного знака единичного уровня U'BX, близкие к ЕП, то эмиттерные переходы транзисторов элемента И VT1-VT4 типа р-n-р смещаются в обратном направлении, при этом все транзисторы схемы И будут заперты. В этом режиме на выходе схемы И в точке m устанавливается напряжение UIm положительного знака на уровне 1, поступающее на базу VT5 (рис.2.80).

Сопротивления резисторов R1 и R2 подобраны так, чтобы значение U'm было больше суммы напряжений, необходимых для открытия транзистора VT5, стабилитрона VD2 и транзистора VT6 элемента НЕ.

Под воздействием Um транзистор VT5 и стабилитрон VD2 открываются и пропускают напряжение положительного знака на базу VT6. Эмиттерный переход VT6 смещается в прямом направлении (так как Uб > UЭ) и открывается, в транзисторе VT6 появляется ток I, усиленный VT5 до значения, при котором VT6 переходит в режим полного насыщения. Сопротивление насыщенного транзистора очень мало, и поэтому на коллекторе VT6 в точке k появляется напряжение на уровне логического 0, равное 0,5-0,6 В. Это напряжение поступает на базу VT7 и запирает его. Напряжение на выходе микросхемы (в точке Y) складывается из падений напряжения в открытых VT6 и VD3 и равно 0,7-0,9 В.

Следовательно, напряжение UY находится на уровне логического 0. При подаче на все входы микросхемы сигнала 1 схема приходит в действие и на ее выходе возникает инвертированный сигнал на уровне 0 – схема выполняет логическую операцию И-НЕ.

Допустим теперь, что на микросхему, находящуюся в состоянии действия (выполнения операции И-НЕ), на один из входов, а значит, и на базу VT2, вместо логической 1 поступил нулевой сигнал (UBX2 < 0,8 В).

Под действием положительного потенциала, поступающего от источника питания +ЕП по R1 и R2 в точку m, транзистор VT2 открывается, поскольку UЭ > Uб, тогда через переход эмиттер – коллектор открывшегося VT2 на базу VT5 поступает нулевой потенциал от нулевой шинки схемы. Транзистор VT5 закрывается, что влечет за собой закрытие VD2 и VT6. Напряжение коллектора VT6 (точка k) резко возрастает, и, как следствие этого, на базе VT7 появляется напряжение, близкое к ЕП, открывающее транзистор VT7 (так как его Uб > UЭ). Через открытый транзистор VT7 в точке Y на выходе микросхемы ЛЭ появляется напряжение единичного уровня UY = U1BЫX.

При отсутствии нагрузки U1BЫX ≈ ЕП. При наличии нагрузки, вследствие падения напряжения в R5, U1BЫX, уменьшается в зависимости от соотношения сопротивлений резисторов R5 и R4. Следовательно, при появлении на входе микросхемы сигнала нулевого уровня на ее выходе появляется сигнал на уровне 1.

Рассмотренная схема может использоваться в качестве реализующей при единичных входных сигналах логическую операцию И—НЕ и возвращающейся в исходное состояние при появлении нулевого сигнала хотя бы на одном из входов. Эта же схема может служить для реализации операции ИЛИ-НЕ, если принять в качестве входного сигнала, выполняющего логическую операцию, сигнал нулевого уровня на одном входе микросхемы, а для возврата в исходное состояние использовать подачу на все входы сигналов на уровне логической 1.

Отечественная промышленность выпускает логические микросхемы И-НЕ серии К511, базовой схемой которой является схема, приведенная на рис.2.81.

Модифицированные схемы отличаются от базовой выполнением выходной части схемы – ее элемента НЕ. Вариант подобной схемы с пассивным выходом показан на рис.2.81, где изображены только элемент НЕ и связанная с ним схема смещения, поскольку остальная часть – схема элемента И – не изменяется.

Действие схемы совпадает с базовой схемой с тем лишь отличием, что при подаче на все входы U1BX на выходе (точка Y) появляется нулевой сигнал U0BЫX = Uэк VT6, меньший, чем в базовой схеме, на значение падения напряжения в диоде VD3.

При U0BX выходное напряжение U1BЫX будет немного больше за счет отсутствия VT7.

Дата добавления: 2015-09-07; просмотров: 1119;