Команды процессора

Команды имеют длину в 2, 4, 6 байт. Каждая команда имеет один из шести возможных форматов:

RR, RX, RS, SI, S, SS. В обозначениях форматов используются заглавные буквы, которые указывают, операнды каких классов участвуют в операциях.

RR – операция типа регистр-регистр.

RХ – операция регистр-память, в которой адрес памяти индексируется.

RS – операция регистр-память, но без индексации.

SI – операция память-непосредственный операнд.

SS – операция память-память.

S – один операнд находится в памяти, а другой операнд задан не явно.

Первый байт команды, а в формате S – первые два байта, содержат код операции. Первые два бита кода операции определяют длину и формат команды.

|

В качестве примера приведем некоторые форматы команд:

|

|

В формате RX первый адрес находится в РОНе, номер которого задан полем R1 , а второй адрес задается полями В2, Х2, D2, и указывает на ячейку ОЗУ.

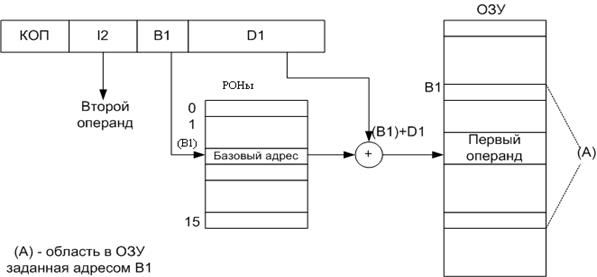

В формате SI в качестве второго операнда непосредственно используется содержимое 8-разрядного поля I2. При этом поля В1 и D1 определяют 1-ый операнд, который находится в ОЗУ. Адрес обращения ОЗУ либо содержится в регистре, номер которого указывается в поле R команды, либо формируется из трех двоичных чисел; базового адреса, индекса и смещения.

Базовый адрес – это 24-разрядное число в РОНе, номер которого задан полем В команды. Базовый адрес используется как средство независимой адресации каждой области памяти и определяет положение этой области в ОЗУ, указывая адрес первого байта области.

Индекс – представляет собой 24-разрядное число в РОНе, номер которого задан в поле Х команды.

Смещение – представляет собой 12-разрядное число в поле D команды. Смещение позволяет выполнить относительную адресацию в пределах 4096 байт, следующих за ячейкой, адрес которой равен базовому адресу.

Рассмотрим формирование физического адреса на примере формата SI.

|

В общем случае для формирования адреса, базовый адрес и индекс рассматривается в качестве 24-разрядных положительных чисел. Аналогично, смещение рассматривается в качестве 12-разрядного положительного числа, старшие 12 разрядов которого равны 0. Все три компоненты адреса (база, индекс и смещение) суммируются как 24-разрядные двоичные числа. При этом, если возникает переполнение, то оно игнорируется (не учитывается). В результате получается 24-разрядный адрес ячейки в ОЗУ, в которой находится один из операндов. При отсутствии в команде поля Х физический адрес формируется путем сложения базового адреса, заданного полем В команды, и смещением D.

Дата добавления: 2015-08-14; просмотров: 1024;