Сегментация памяти в процессоре 8086

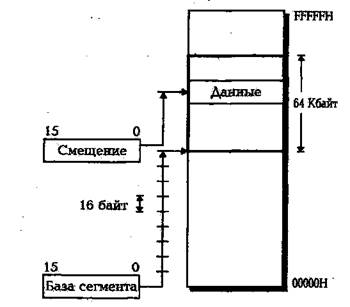

В процессоре 8086 сегментация памяти реализована довольно простыми средствами. Под сегментом понимается блок смежных ячек памяти (в адресном пространстве 1Мбайт) с максимальным размером 64 Кбайт и начальным или базовым адресом, находящимся на 16-байтной границе (такая граница называется параграфом). Для обращения к памяти необходимо определить базу сегмента и 16-битное расстояние от базы, называемое смещением (offset) или относительным адресом. Базовые адреса четырех одновременно доступных программе сегментов находятся в сегментных регистрах кода CS, данных DS, стека SS и дополнительных данных ES. Каждый из них имеет длину 16 бит, но можно считать сегментный регистр 20-битным при формировании физического адреса(четыре младших бита базового адреса содержат нули). Таким образом, две 16-битных величины (указателя), соответствующие базовому адресу сегмента (с подразумеваемыми младшими нулями) и смещению, позволяют обращаться ко всему адресному пространству 1 Мбайт, как показано на рис. 2.1.

| Рис.2.1. Сегментация памяти в процессоре 8086 |

Память

Отметим, что сегментные регистры содержат физические адреса памяти, т.е. значение в каждом сегментном регистре прямо указывает на границу параграфа в адресном пространстве 1 Мбайт. В защищенном режиме последующих процессоров значение в сегментном регистре не имеет прямой взаимосвязи с реальным адресом памяти.

Чтобы упростить обращения к памяти, за каждой командой закреплен сегментный регистр по умолчанию, который привлекается без специальных указаний. Так, команды всегда выбираются из сегмента кода (указателями служит пара CS:IP), все стековые операции выполняются в сегменте стека (SS:SP), данные (переменные) находятся в сегменте данных (база находится в регистре DS, а смещение, называемое эффективным адресом ЕА, определяется режимом адресации). Для обращения к другим сегментам перед командой помещается префикс замены сегмента. Например, команда MOV АХ,[100Н] загружает в регистр АХ слово из сегмента, базовый адрес которого находится в регистре DS, а смещение равно 100Н. Команда с префиксом замены сегмента MOV AX,ES:[100H] будет обращаться к дополнительному сегменту данных, базовый адрес которого находится в регистре ES.

Преобразование пары сегмент:смещение, называемой также логическим или виртуальным адресом, в физический адрес осуществляется довольно просто: содержимое сегментного регистра сдвигается влево на четыре бита (что эквивалентно умножению на 16), а затем суммируется со смещением. Если, например, регистр DS содержит 1234Н, а регистр SI содержит 5678Н, то физический адрес в команде MOV AX,[SI] будет равен

- (DS) * 16 + (SI) = 12340Н + 5678Н = 179В8Н

Отметим два обстоятельства, связанные с сегментацией памяти в процессоре 8086. Во-первых, преобразование логического адреса в физический всегда однозначно, т.е. каждому логическому адресу соответствует уникальный физический адрес. Однако обратное преобразование неоднозначно: каждому физическому адресу соответствуют 4К логических адресов. Поэтому во всех процессорах фирмы Intel манипуляции физическими адресами осуществляются довольно сложно. Во-вторых, в этом способе формирования физического адреса может возникнуть своеобразное переполнение. Пусть, например, регистр DS содержит 0FFFFH. Тогда в команде MOV АХ,[3000Н] физический адрес будет равен

(DS) * 16 + 3000Н = OFFFFOH + 3000Н = 102FF0H

В такой ситуации процессор просто отбрасывает старший 21-й бит адреса и выдает на шину адрес 02FF0H. Другими словами, здесь происходит так называемое «заворачивание» или «закругление» (wrap around) адреса: от адреса 0FFFFFH происходит переход к нулевому адресу. Заворачивание адреса приходится учитывать при работе процессора i486 в R- и V-режиме.

Простая сегментация памяти в процессоре 8086 обладает следующими особенностями, которые в известном смысле можно считать ее недостатками, усложняющими разработки мультизадачных систем.

1. Сегменты памяти, определяемые только одними сегментными регистрами, имеют всего два атрибута: начальный адрес, находящийся на границе параграфа, и максимальный размер 64 Кбайт. Никаких аппаратных средств контроля правильности использования сегментов нет. Размещение сегментов в памяти произвольно: сегменты могут частично или полностью перекрываться или не иметь общих частей. Программа может обращаться к любому сегменту для производства как считывания, так и записи данных, а также для выборки команд. В более общем плане, программа может обратиться по любому физическому адресу, а для защиты определенных областей памяти от несанкционированного доступа требуются внешние схемы.

2. Нет никаких препятствий для обращения даже к физически- несуществующей памяти. Когда программа выдает адрес несуществующей памяти, результат зависит только от особенностей схем дешифрирования адреса и управления внешней шиной: процессор может получить фиктивные данные, будет сформирован сигнал прерывания или система может просто зависнуть в ожидании данных, которые никогда не будут возвращены.

С учетом этих недостатков сегментация памяти сначала в процессоре 80286, а затем и в процессорах 80386 и далее была значительно усовершенствована. В этих процессорах имеются гибкие средства организации сегментов с большим числом атрибутов и эффективные механизмы контроля и защиты доступа к сегментам. Кроме того, «ниже» сегментации действует внутренний механизм страничной организации памяти, который позволяет еще более гибко управлять ресурсами памяти компьютера.

Дата добавления: 2015-06-05; просмотров: 4659;