Сетевые контролеры семейства 8254X

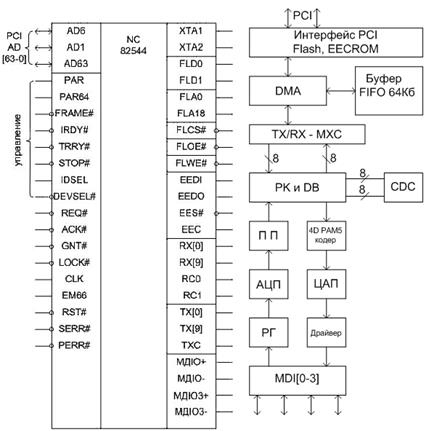

Контроллеры данного семейства способны передавать и принимать данные на скоростях 1000Мбит/c (стандарт IEEE 802.3ab), 100Мбит/c (стандарт IEEE 802.3.u) 10Мбит/c (стандарт IEEE 802.3 ) и подключаются к 64-х битному интерфейсу PCI - 2.2 и PCI – x, который работает на частоте 133 MГц. Структурная схема контроллера и его условное графическое обозначение приведено на рисунке 2.13, где TX/RX-приемопередатчик MAC-уровня; CDC-скремблер – дескремблер; РКДВ-решетчатый кодер-декодер Витерби; ПП-подавитель помех (ECHO, FEXT, NEXT); РГ-резистивный гибрид; ФИ-формирователь импульсов; MDI-интерфейс, зависящий от среды.

Рисунок 2.13

Назначение основных выводов на условном графическом обозначении контроллера Intel82544 представлено в таблице 2.4.

Сигналы управлении питанием, сигналы индикации, входы тестирования на УГО не показаны.

Таблица 2.4

| Шины адреса и данных PCI | Сигналы управления PCI | ||||

| AD0- AD63 | Мультиплицированноя двунаправленноя шина адреса-данных | FRAME# | обмен | ||

| IRDY# | Инициатор чтения | ||||

| CBEO#-CBE7# | Выбор байта | TRDY# | Чтение в пакетном режиме | ||

| PAR | Паритет AD0- AD31 | STOP# | Остановка | ||

| PAR64 | Паритет AD32- AD63 | IDSEL | Инициализация выбора | ||

| DEUSEL | Выбор устройств | ||||

| Сигналы арбитража | Системные сигналы | ||||

| REQ# | Запрос передачи | CLK | Синхронизация | ||

| ACK# | Подтверждение передачи | EM66 | Выбор 66Мгц | ||

| GMT# | Главная шина | RST# | Сброс | ||

| Lock# | Блокировка шины | SERR# | Системная ошибка | ||

| PERR# | Ошибка паритета | ||||

| Передачик | Приемник | ||||

| TX9- TX0 | Данные | RX9-RX0 | Данные | ||

| TXC | синхронизация | RXC0 | синхронизация | ||

| RXC1 | синхронизация | ||||

| Интерфейс с FLASH | Интерфейс с EEPROM | ||||

| FLD0-FLD7 | данные | EED0 | Последовательный выход | ||

| FLA0- FLA18 | адрес | EEDI | Последовательный вход | ||

| FLCS# | Выбор FLASH | EESK# | Выбор частоты | ||

| FLOE# FLWE# | Разрешение выхода Разрешение записи | EECS# | Выбор схемы | ||

| Выходные сигналы 4-х каналов MDI | |||

| MDI0+ | MDI1+ | MDI2+ | MDI3+ |

| MDI0- | MDI1- | MDI2- | MDI3- |

В состав контроллера 82544 входит блок интерфейса с шиной PCI, блок интерфейса FLASH и EEPROM. При передаче данных между рабочей станцией и сетью через шину PCI контроллер выступает как ведущее устройство (Master). Управляет передачей данных контроллер DMA.

При получении данных из сети, контроллер выбирает их из FIFO-приемника и передает во входную область буферной памяти рабочей станции. Когда идет передача данных, контроллер из буфера памяти рабочей станции, помещает их в FIFO- передатчика. Общий объем FIFO-памяти составляет 64Кб. Физический уровень обеспечивает кодирование и декодирование данных, режим автопереговоров, который определяет тип использованной сетевой технологии, автоматического определения типа кабеля, автоматического определения полярности сигнала.

В контроллере предусмотрено возможность замедления прерывания. Если бы такое замедление отсутствовало, прерывания возникали на каждом передаваемом пакете. С ростом объема трафика такое решение занимало много времени центрального процессора и приводило к значительным потерям производительности. Схема замедлений прерываний позволяет программно задавать времена таймеров, которые будут генерировать прерывания. Предусмотрено использование общего таймера и таймера приема пакетов. В связи с тем, что сетевой трафик непредсказуем, потребовалась организация такого механизма ограничения числа прерываний.

Контроллер Intel 82544 работает с многомодовым кабелем, Intel 82545 с одномодовым, Intel 82546 – двухпоротвый. Контроллер Intel 82541 расположен в корпусе 15х15 мм. и имеет 196 выводов, в контроллере Intel 82544 – корпус 27х27 мм, выводов 416, контроллер Intel 82546 имеет корпус 21х21 мм., выводов 364.

Сетевой контроллер Intel 82597 обеспечивает работу с 10-гигабитным Ethernet (10GE). Обработка сигналов (кодирование-декодирование, модуляция-демодуляция) осуществляет цифровой сигнальный процессор DSP, расположенный на его кристалле.

Дата добавления: 2015-02-16; просмотров: 1104;