Сетевые контроллеры (NC) Intel семейства 8255X

Сетевые контроллеры данного семейства обеспечивают связь с 32-х разрядной шиной PCI, для обычного E(10Мбит/с) и FE(100Мбит/с). В данное семейство включаются контроллеры Intel 82557, 82558, 82559, 82550 и 82551. Сетевой контроллер 82557 является контроллером первого покаления. Этот контроллер можно было использовать только вместе со схемой 82555, представляющей собой интерфейс физического уровня. Сетевой контроллер 82558–контроллер второго поколения. Он представляет собой большую ИС, в которой на одном кристалле расположены 82557 и 82555. Контроллер размещен в корпусе, имеющем 208 выводов и использует питание + 5 В. Сетевой контроллер 82559-контроллер третьего покаления, который может работать с напряжением +3,3В. Контролеры 82550 и 82551- последние модели данного семейства. Контроллер 82551 допускает подключение к двум каналам связи.

|

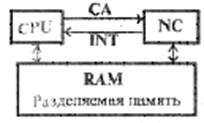

Взаимодействие сетевого контроллера с центральным процессором рабочей станции осуществляется через разделяемую память (рис.2.10) где СА - сигнал "внимание канал" (canal attention); INT - запрос на прерывание.

Рисунок 2.10

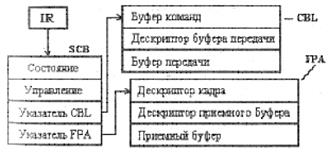

Рисунок 2.11

Разделяемая память (рис. 2.11) - это область основной оперативной памяти (RAM) ПК. В ней выделяются участки: начальный указатель IR (Initialisation Root); системный управляющий блок SCB (System Control Block); буфер приема кадров FPA (Receive Frame Area); блок списка команд CBL (Command Block List).

Обмен информацией осуществляет SCB, называемым "почтовым ящиком". При необходимости CPU помещает команду и данные в "почтовый ящик", извещая сетевой контроллер об этом путем выработки высокого уровня сигнала СА, а затем переходит к работе с другими задачами. Сетевой контроллер извлекает команду из "почтового ящика" и выполняет ее без участия CPU. После выполнения команды сетевой контроллер вырабатывает сигнал запроса прерывания ("возврат почты"), извещая этим CPU о выполнении работы. То есть, "почтовый ящик" позволяет параллельно выполнять команды в CPU и принимать кадры из сети. Начальный указатель располагается по стандартному адресу, известному как CPU, так и NC. В процессе инициализации сетевой платы этот адрес можно изменить. Начальный указатель определяет место расположения "почтового ящика". "Почтовый ящик" включает в себя два блока: FPA и CBL. В CBL находятся команды CPU, а в буфере приема кадров временно хранятся кадры, принятые из сети.

Сетевой контроллер выполняет команды высокого уровня, которые поступают в CBL. Эти команды называются командами действия и выполняются параллельно с работой CPU. Рассмотрим команду "передать кадр": в качестве параметров эта команда содержит сетевой адрес назначения, данные, которые должны быть переданы в этом кадре, длину передаваемого кадра, указатель на цепочку буферов в передаваемых кадрах. Такая цепочка буферов передаваемых кадров позволяет размещать их в оперативной памяти в произвольных местах, причем занимать в этой памяти ровно столько места, сколько для этого нужно. Служебная информация к передаваемому кадру добавляется в самом сетевом контроллере. К этой информации относятся: преамбула, адрес отправителя, код циклического контроля. Команда "прием кадра" выполняется таким образом: при инициализации сетевой карты устанавливается размер приемного буфера. Этот буфер организован тоже в виде цепочки последовательно ссылающихся друг на друга участков. Информация в этот буфер поступает из специального блока приема кадров, находящийся в сетевом контроллере. После поступления информации в приемный буфер вырабатывается сигнал прерывания. Структурная схема контроллера 82558 приведена на (рис. 2.12).

Рисунок 2.12

Где: Тх – передатчик, RX - приемник, БП - блок автопереговора, БОК - блок обработки коллизий, БСИ – блок светодиодних индикаторов, БИФУ – блок интерфейса физического уровня.

Сетевой контроллер 82558 выполняет все функции канального уровня модели OSI, а именно: формирует пакет, генерирует исходный адрес, осуществляет проверку адреса назначения, вычисляет контрольную сумму - код CRC. Функционально контроллер разбит на 3 подсистемы параллельную подсистему (ПРП), подсистему буферной памяти (FIFO), состоящую 128-байтного буфера приема и 64-байтного буфера передачи, и последовательную подсистему (ПСП).

Параллельная подсистема содержит: управляющее устройство (УП) блок интерфейса с системной шиной данных DIU (data interface unit), блок интерфейса с системной шиной управления BIU (bus interface unit), блок прямого доступа к памяти DMA (direct memory access). Внутри параллельной подсистемы все блоки связаны между собой с помощью внутренней 32 разрядной шины P-bus. УП генерирует последовательность микрокоманд которые передаются на другие блоки. Это устройство содержит 32 разрядный арифметический блок (АБ), регистровый файл (РФ), блок адресации (БА), постоянную память (ROM), командный блок (CU) и приемный блок (RU). CU выбирает команды из разделяемой памяти и выполняет их, включая команду передачи кадров. RU управляет всеми операциями по приему данных из сети. Оба эти блока имеют собственные программные счетчики, стековую память, работают независимо друг от друга и управляются микрокомандами, считывающимися из ROM. Независимость работы позволяет выполнять команды и принимать информацию одновременно, управляет блоками ROM и DMA. Блок CU осуществляет работу по инициализации контроллера, обрабатывает команду СА, посредством которой процессор компьютера сообщает контроллеру о необходимости выполнить команду размещенную в "почтовом ящике" разделяемой памяти.

Сетевой контроллер 82558 может работать в режиме задатчика шины (Bus Master). Работу по организации этого режима осуществляет блок BIU путем соглашения HOLD-HLDA, (т.е. анализа, приема и выработки сигналов HOLD-HLDA). Этот блок управляет работой регуляторов времени использования системной шины (СШ). Таких регуляторов в контроллере два: T-ON и T-OFF, которые представляют собой счетчики. Первый регулятор ограничивает максимальное время занятия системной шины сетевым контроллером. Этот счетчик запускается по сигналу HLDA. При достижении максимального времени сетевой контроллер отключается от системной шины. В этот момент включается второй счетчик, определяющий минимальное время, в течение которого сетевой контроллер может быть отключен от СШ. Этот же блок вырабатывает сигнал прерывания, сообщая центральному процессору о возникновении определенных событий, например, о получении кадра.

Блок DIU осуществляет передачу данных. Основным узлом данной блока является схема маршрутизатора, который выполняет переключения между тремя входными и тремя выходными 32-разрядными шинами данных. Всего предусмотрено 4 маршрута: из СШ в блок FIFO при передаче кадра в сеть; из FIFO в СШ при приеме; между СШ и УУ; передача между FIFO и УУ. Блок DMA обеспечивает прямой доступ к памяти по 4-м независимым каналам. В этом контроллере разделяемая память установлена на кристалле, размер буферной памяти FIFO увеличен до 6Кбайт (3 Кбайт - на передачу, 3Кбайт - на прием). Контроллер обеспечивает поддержку Flash памяти до 1 Мбайт, поддержку MII-интерфейса. В этом контроллере возможен пакетный обмен информацией через системную шину данных, состоящую из 256 двойных слов.

Последовательная подсистема осуществляет преобразование последовательного кода в параллельный и обратно (блоки БПД и БПР), содержит также блок контроля несущей и обнаружения столкновений (CSMA/CD) и таймер случайного времени (ТСВ). Преобразование параллельного кода в последовательный осуществляется с помощью блоков передачи (БПД) байтов и битов. При передаче информации БПД формирует кадр, добавляя к нему контрольную последовательность. Прием данных осуществляется с помощью блоков приема (БПР) битов и байтов. В поступившем из сети кадре удаляется преамбула, битовое заполнение (если оно есть) и вычисляется CRC, проверяется адрес назначения. Если в контроллер поступил свой кадр, он передается в буферную память.

С помощью CSMA/CD контроллер постоянно следит за состоянием канала. Как только канал освобождается, и у контроллера имеются данные для передачи, он начинает передачу, продолжая контролировать канал. Если в это же время другой сетевой адаптер тоже начал передачу, происходит конфликт. Он обнаруживается этим блоком. Если в канале происходит наложение информации от нескольких PC, возникает недопустимо короткая пауза между сигналами в канале. По ней и обнаруживается столкновение. Если возникает конфликт, данный контроллер прерывает передачу и посылает в канал специальную последовательность бит, которая извещает другие PC о возникновении конфликта. Повторная передача возможна по истечению времени, которое задается ТСВ. Этот таймер выдает фиксированные интервалы времени, кратные 51,2 мкс (время передачи от приемника к передатчику и обратно). В ТСВ имеется специальный счетчик, который обнуляется после каждой успешной передачи кадра в сеть. Содержание этого счетчика увеличивается на 1 после каждой неуспешной передачи. Программно можно задать максимальное значение этого счетчика. При достижении этого значения повторные передачи прекращаются, и CPU уведомляется о такой ситуации путем выработки сигнала прерывания и установки специальных битов в блоке SCB (рис. 2.11).

Последовательная система включает блоки для 10 и 100 Мбит/с Ethernet - поддерживает соответственно протоколы IEEE 802.3 для 10 Base T и протокол IEEE 802.3u для 100 Base TX и 100 Base T4. В режиме FE блок 100Мб/c выполняет следующие функции: при передаче преобразует 4 информационных бита в пятиразрядный символ с помощью кодера 4В/5B, после скремблирования в блоке CDC цифровой информационный поток 125 Мбит/с перекодируется в код MLT-3, который поступает на передающую пару соединителя RJ-45; при приеме поступивший с соединителя RJ-45 код MLT-3 превращается в цифровой поток 125 Мбит/с. После декодирования 4В/5B восстанавливаются информационные сигналы.

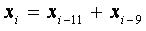

Скремблер принимает порции 5-битовых данных с кодера 4В/5В, шифрует порции по 11 бит в соответствии с логическим выражением:

Дескремблирование осуществляется с помощью 11-разрядного регистра сдвига с обратной связью и завершается получением 5-битовых символов. В последовательную систему входит также блок обнаружения коллизий (БОК), блок автопереговоров (БАП), блок светодиодных индикаторов (БСИ).

Дата добавления: 2015-02-16; просмотров: 1008;