Порядок выполнения работы. 1 Проверка подготовки учащихся к занятию по вопросам для самоконтроля в виде фронтального или программированного опроса.

1 Проверка подготовки учащихся к занятию по вопросам для самоконтроля в виде фронтального или программированного опроса.

2 Выполнить индивидуальное задание № 1. Составить схему алгоритма и программу линейного вычислительного процесса на языке Ассемблер для МП Intel 8085A, которая реализует последовательности арифметических или логических операций согласно варианту, заданному в таблице 12.1 (номер варианта выбирается в зависимости от номера учащегося в списке подгруппы учебного журнала группы, т. е. от номера рабочего места).

Таблица 12.1 – Исходные данные к индивидуальному заданию № 1

| № варианта | Последовательность операций | Значения операндов (P = 16) | ||||||

| (A) | (B) | (C) | (D) | (E) | (M1) | (M2) | ||

| M2 = 2((C) + (D)) – (M1) | – | – | 1A | – | – | |||

| M1 = (B̅) ˅ (A) ˄ (M2) | – | – | – | – | F0 | |||

| M2 = ((M1) – (A)) : 2 + 05h | 15H | – | – | – | – | 25H | – | |

| M1 = (C̅) ˅ (M2)) ˄ (A) | 2D | – | E1 | – | – | – | ||

| M2 = (D) – 2 (M1) + 10h | – | – | – | – | – | |||

M1 = (E̅) ⊕ (A)  ( (  ) )

| – | – | – | 1F | – | |||

| M2 = ((C) – (A)) : 4 – (M1) | – | 2D | – | – | – | |||

| M1 = (D̅) ˄ ((A) ⊕ (M2)) | 1E | – | – | – | – | A0 | ||

| M2 = 4((D) – (M1)) + (A) | 10H | – | – | 0A | – | – | ||

| Окончание таблицы 12.1 | ||||||||

M1 = ((B) ⊕ (D̅)) ˄ (  ) )

| – | – | – | – | 2F | |||

| M2 = (A) + ((M1) – (D)) : 2 | – | – | – | 1A | – | |||

M1 = (B) ˄ (A) ⊕ (  ) )

| – | – | – | – | FE | |||

| M2 = 2((M1) – (B)) + (A) | 1E | 1A | – | – | – | 2B | – | |

| M1 = (C̅) ⊕ (M2) ˄ (A) | – | – | – | – | ||||

| 15* | M2 = ((B) ⊕ (  )) ˄ (A) + 02 h )) ˄ (A) + 02 h

| 2C | – | – | – | 0F | – | |

| Примечания 1 M1 – ячейка памяти по адресу 2020 h. 2 M2 – ячейка памяти по адресу 2021 h. 3 Начальный адрес программы 2000 h. 4 Для варианта №15* приведен пример в методических указаниях. |

2.1 Составить алгоритм решения задачи. При этом следует помнить, что в МП Intel 8085A арифметическое умножение и деление на 2 выполняется с помощью команд сдвига влево через перенос RAL и вправо через перенос RAR соответственно.

2.2 Составить программу на языке Ассемблер в виде таблицы (таблица 12.2).

Таблица 12.2 – Линейная программа на языке Ассемблер

| Адрес | Метка | Команда | Операнд | Машинный код | Комментарий |

2.3 Определить ожидаемый результат вычисления. Для этого при выполнении арифметических операций следует подставить в заданное уравнение значения переменных в десятичной системе счисления и выполнить указанные арифметические операции в десятичной системе счисления. Порядок расчета и ожидаемый результат записать в отчет в десятичной и шестнадцатеричной системах счисления.

Логические операции следует выполнять в двоичной системе счисления поразрядно, при этом следует помнить, что логические операции обладают приоритетом. Порядок расчета и ожидаемый результат записать в отчет в двоичной и шестнадцатеричной системах счисления (см. пример в методических указаниях к данной лабораторной работе).

3 Выполнить индивидуальное задание № 2. Составить программу циклического вычислительного процесса на языке Ассемблер для МП Intel 8085A по заданному алгоритму, которая реализует умножение двух восьмиразрядных двоичных чисел без учета знака (кодовое умножение) согласно варианту, заданному в таблице 12.3. Начальный адрес программы 2000 h.

Таблица 12.3 – Исходные данные к индивидуальному заданию № 2

| Номер варианта | Значения операндов (P = 16) | Номер варианта | Значения операндов (P = 16) | ||

| (DE) | (A) | (DE) | (A) | ||

| 00A3 | B2 | 00C3 | 5B | ||

| 00B4 | C3 | 00B3 | |||

| 00D5 | 00D2 | A3 | |||

| 00E6 | 00B1 | ||||

| 00F1 | DA | 00C1 | |||

| 00D4 | 00D1 | ||||

| 00B2 | 00E1 |

Пусть множимое хранится в паре регистров DE, где оно занимает младший регистр E, старший регистр D пары регистров установлен в нуль. Множитель хранится в аккумуляторе A. 16-разрядное произведение будем формировать в паре регистров HL. Счетчик числа повторений цикла организуем на регистре B.

Процесс умножения организуем следующим образом. Будем анализировать разряды множителя, начиная с его старшего разряда. Поэтому частичные произведения будут формироваться, начиная со старшего частичного произведения. Накопление суммы частичных произведений будем производить в паре регистров HL, т.е. к содержимому предварительно сброшенной в нуль пары регистров HL вначале прибавим восьмое частичное произведение. Затем, сдвинув на один разряд влево содержимое пары регистров HL, прибавим седьмое частичное произведение и так далее, пока не будут просуммированы все частичные произведения.

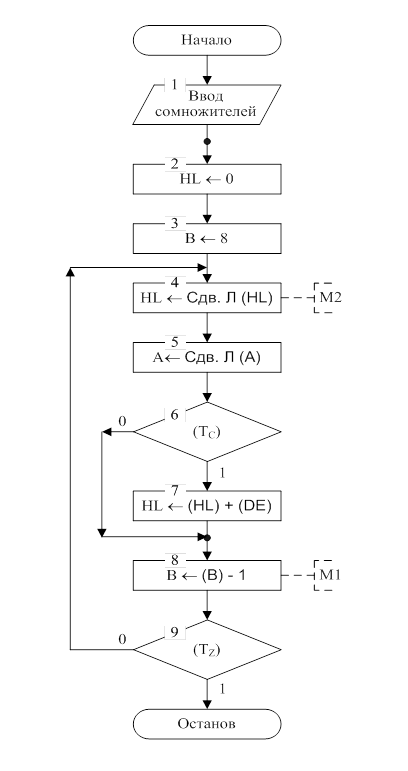

Таким образом, процесс умножения носит циклический характер. Цикл, содержащий операции сдвига влево содержимого пары регистров HL, формирования и прибавления к содержимому пары регистров HL очередного частичного произведения, должен быть повторен восемь раз. Алгоритм решения задачи представлен на рисунке 12.1.

Рисунок 12.1 – Схема алгоритма кодового умножения восьмиразрядных двоичных чисел

Блок 1(рисунок 12.1) производит загрузку множимого в пару регистров DE и множителя в регистр A. Блок 2 производит загрузку нулевого значения в пару регистров HL. Блок 3 устанавливает в регистре B (счетчике циклов) начальное значение 8. Блок 4 производит сдвиг на один разряд влево содержимого пары регистров HL (команды DAD HL). Эта операция выполняется путем удвоения содержимого пары регистров: HL (HL) + (HL). Блок 5 предназначен для анализа очередного разряда множителя. Для этого содержимое аккумулятора сдвигается влево, в результате чего очередной разряд множителя пересылается в триггер TC регистра признаков. Блок 6 производит разветвление (условный переход) по содержимому триггера перехода TC. При (TC) = 1 в блоке 7 выполняется операция суммирования множимого к сумме предыдущих частичных произведений в паре регистров HL (команда DAD DE). При (TC) = 0 операция суммирования не выполняется, по команде условного перехода JNC M1 осуществляется переход к команде блока 8. Блок 8 производит вычитание единицы из содержимого регистра B, после чего блок 9 выполняет условный переход по содержимому триггера нуля TZ регистра признаков. Если (TZ) = 0 (содержимое регистра B не равно нулю), то команда условного перехода JNZ M2 производит переход к команде блока 4, вызывая очередное повторение выполнения тела цикла. Если (TZ) = 1 (содержимое регистра B равно нулю), то происходит выход из цикла и переход к очередной команде.

3.1 Составить циклическую программу умножения восьмиразрядных двоичных чисел на языке Ассемблер в форме таблицы 12.2.

3.2 Определить время выполнения операции умножения для тактовой частоты равной 4 МГц. Для этого определить количество тактов, требуемое для однократного прохождения цикла алгоритма и полученный результат умножить на восемь. Суммарное число тактов умножить на длительность тактового периода (0,25 мкс).

4 Ответить на контрольные вопросы.

5 Оформить отчет и сдать зачет.

Содержание отчета

Отчет должен содержать:

1 Наименование и цель лабораторной работы.

2 Выполненные индивидуальные задания № 1, 2 (условия, алгоритмы и программы).

3 Расчет ожидаемого результата выполнения линейной программы.

4 Расчет времени выполнения операции умножения двух восьмиразрядных двоичных чисел.

5 Ответы на контрольные вопросы.

Контрольные вопросы

1 Поясните, как проверить переполнение разрядной сетки при выполнении операции суммирования в МП Intel 8085A?

2 Поясните, как умножить на два в МП Intel 8085A?

3 Поясните, как выполнить суммирование двух 16-разрядных двоичных чисел в МП Intel 8085A? Укажите необходимую команду и ее особенности.

Дата добавления: 2014-11-30; просмотров: 1717;