Архитектуры многопроцессорных вычислительных систем

Персональные компьютеры позволяют реализовать многие компьютерные технологии, начиная от работы в Интернете, и кончая построением анимационных трехмерных сцен. Однако существуют задачи, объем вычислений которых превышает возможности персональною компьютера. Для их решений применяются компьютеры с гораздо более высоким быстродействием. Для получения высокого быстродействия на существующей элементной базе используются архитектуры, в которых процесс обработки распараллеливается и выполняется одновременно на нескольких обрабатывающих устройствах Существует три основных подхода к построению архитектур таких компьютеров: многопроцессорные, магистральные и матричные архитектуры.

Архитектура простых многопроцессорных систем выполняется по схеме с обшей шиной. Два или более процессоров и один или несколько модулей памяти размешены на общей шине. Каждый процессор, для обмена с памятью, проверяет, свободна ли шина, и, если она свободна, он занимает ее. Если шина занята, процессор ждет, пока она освободится. При увеличении числа процессоров производительность системы будет ограничена пропускной способностью шины. Чтобы решить эту проблему, каждый процессор снабжается собственной локальной памятью (рис. 1), куда помешаются тексты исполняемых программ и локальные переменные, обрабатываемые данным процессором. Общее запоминающее устройство используется для хранения общих переменных и общего системного программного обеспечения. При такой организации нагрузка на общую шипу значительно снижается.

Рис. 4. Архитектура многопроцессорной вычислительной системы с общей шиной

Один из процессоров выделяется для управления всей системой.Он распределяет задания на исполнение программ между процессорами и управляет работой общей шины.

Периферийный процессор осуществляет обслуживание внешних устройств при вводе и выводе информации из обшей памяти. Он может быть того же типа, что и остальные процессоры, но обычно устанавливается специализированный процессор, предназначенный для выполнении операций управления внешними устройствами.

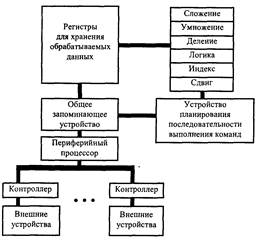

Магистральный принцип является самым распространенным при построении высокопроизводительных вычислительных систем. Процессор такой системы имеет несколько функциональных обрабатывающих устройств, выполняющих арифметические и логические операции, и быструю регистровую память для хранения обрабатываемых данных. Данные, считанные из памяти, размещаются в регистрах и из них загружаются в обрабатывающие устройства. Результаты вычислений помешаются в регистры и используются как исходные данные для дальнейших вычислений. Таким образом, получается конвейер преобразования данных: регистры – обрабатывающие устройства – регистры – …. Архитектура магистрального суперкомпьютера приведена на рис. 5. Число функциональных устройств равно шести («Сложение», «Умножение» и т.д.), однако в реальных системах их количество может быть иным. Устройство планирования последовательности выполнения команд распределяет данные, хранящиеся в регистрах, на функциональные устройства и производит запись результатов снова в регистры. Конечные результаты вычислений записываются в общее запоминающее устройство.

Рис. 5.Архитектура магистрального суперкомпьютера

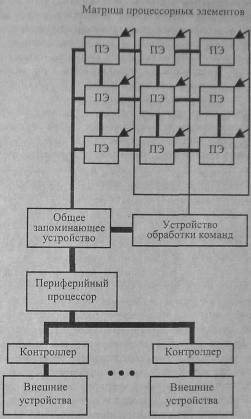

В матричной вычислительной системе процессоры объединяются в матрицу процессорных цементов. В качестве процессорных элементов могут использоваться универсальные процессоры, имеющие собственное устройство управления, или вычислители, содержащие только АЛУ и выполняющие команды внешнего устройства управления. Каждый процессорный элемент снабжен локальной памятью, хранящей обрабатываемые процессором данные, но при необходимости процессорный элемент может производить обмен со своими соседями или с общим запоминающим устройством. В первом случае, программы и данные нескольких задач или независимых частей одной задачи загружаются в локальную память процессоров и выполняются параллельно. Во втором варианте все процессорные элементы одновременно выполняют одну и ту же команду, поступающую от устройства обработки команд на все процессорные элементы, но над разными данными, хранящимися в локальной памяти каждого процессорного элемента. Вариант архитектуры с общим управлением показан на рис. 6. Обмен данными с периферийными устройствами выполняется через периферийный процессор, подключенный к общему запоминающему устройству.

Рис.6. Архитектура матричной вычислительной системы с общим управлением

Дата добавления: 2014-12-08; просмотров: 2745;