Структурная схема ВМ86

Организация циклов обращения к магистрали. Представленная на рис. 6.5 структурная схема МП ВМ86 разбита на два ассинхроно работающих блока: блок сопряжения (БС) и блок обработки (БО). Блок сопряжения формирует физические 20-разрядные адреса, осуществляет опережающую выборку команд и обмен данными, управляет шиной микропроцессора. Выбранная командная последовательность хранится в буферном файле типа FIFO (очередь), глубина которого 6 байт. Всякий раз, когда в очереди освобождаются два байта и отсутствует запрос на доступ к каналу для передачи операнда, БС выбирает из памяти следующее слово командной последовательности.

Рис. 6.5. Схема микропроцессора ВМ86

Блок обработки извлекает байты команд из очереди и исполняет их. При необходимости обмена операндом с памятью БО обращается к блоку сопряжения, который и реализует этот запрос. Любое нарушение последовательного хода выполнения программы инициирует очистку и повторное заполнение очереди команд. Совмещение операций выборки и исполнения команд привело к существенному повышению производительности МП при тех же частотных свойствах канала и быстродействии памяти МС.

Существуют два режима работы МП: минимальной и максимальной конфигурации, которые отличаются друг от друга составом входных (выходных) управляющих сигналов (рис. 6.6). Режим программируется с помощью входа MN/  .

.

Рис. 6.6. Условное графическое обозначение микропроцессора ВМ86:

а) минимальный режим, б) максимальный режим

Работа МП осуществляется синхронно с тактовыми импульсами, поступающими на вход CLK. Стандартная частота следования тактовых импульсов 5 МГц обеспечивает микротакт МП, равный 200 нс. Границей раздела микротактов Т (тактов) считается срез синхроимпульса. Скважность следования импульсов равна 1/3. Фронт и срез CLK должны быть достаточно крутыми (≤ 10 нс). В конструкцию МП включены динамические ячейки, для сохранения состояния которых необходима минимальная частота 2 МГц. Поэтому блокировка CLK с целью реализации одношагового или циклического режимов работы запрещена.

При необходимости совершить обмен данными с памятью или выбрать очередной элемент программной последовательности МП инициирует цикл обращения к магистрали. Каждый такой цикл содержит не менее четырех тактов Т1—Т4 и состоит в чтении и записи слова (байта) из МП. Временные диаграммы циклов чтения и записи показаны на рис. 6.7. В такте Т1 МП по линиям A19/S6—A16/S3, AD15—AD0 и  /S7 передает адресную информацию А19—А0,

/S7 передает адресную информацию А19—А0,  . При адресации портов ВВ на линиях А19—А16 устанавливается 0. В цикле записи МП помещает данные на шину AD15—AD0 в тактах Т2—Т4. В цикле чтения такт Т2 используется для переключения шины адресов/данных на чтение. В это время шина находится в высокоомном состоянии. Прием данных осуществляется в Т3 и Т4.

. При адресации портов ВВ на линиях А19—А16 устанавливается 0. В цикле записи МП помещает данные на шину AD15—AD0 в тактах Т2—Т4. В цикле чтения такт Т2 используется для переключения шины адресов/данных на чтение. В это время шина находится в высокоомном состоянии. Прием данных осуществляется в Т3 и Т4.

Рис. 6.7. Временные диаграммы циклов чтения (а) и записи (б) ВМ86

В такте Т3 любого машинного цикла МП опрашивает вход готовности ПУ к обмену READY. Если на входе READY сигнала готовности нет, то после такта Т3 МП входит в состояние ожидания, которое длится целое число тактов TW. После прихода сигнала READY МП завершает машинный цикл тактом Т4 и переходит к следующему циклу обращения к магистрали. Может случиться, что необходимости в таком обращении нет, тогда появляются холостые такты Т5.

Вход READY, используемый для асинхронного доступа к медленным периферийным модулям памяти и ВВ, не синхронизируется. Поэтому должны быть предусмотрены внешние средства его синхронизации импульсами CLK.

Параллельно с передачей данных в тактах Т2, Т3 (TW) и Т4 на линиях  /S7 и A19/S6—A16/S3 присутствует информация о состоянии процессора S7—S3. Сигнал S6 всегда находится в состоянии 0, сигнал S5 индицирует состояние флажка разрешения прерывания IF, а сигналы S4, S3 кодируют сегментный регистр, применяемый для формирования физического адреса согласно табл. 6.14. Сигнал S5 обновляется в начале каждого такта CLK.

/S7 и A19/S6—A16/S3 присутствует информация о состоянии процессора S7—S3. Сигнал S6 всегда находится в состоянии 0, сигнал S5 индицирует состояние флажка разрешения прерывания IF, а сигналы S4, S3 кодируют сегментный регистр, применяемый для формирования физического адреса согласно табл. 6.14. Сигнал S5 обновляется в начале каждого такта CLK.

Таблица 6.14

| S4 | S3 | Сегментный регистр |

| ES | ||

| SS | ||

| CS, BB или прерывание | ||

| DS |

Передаваемая в первом такте Т1 информация А19—А0 и  используется для адресации памяти и портов ВВ. Память на физическом уровне представляет собой набор 16-разрядных ячеек, разбитых на два байтовых банка: Н и L по 512К байт каждый. Если Н-банк состоит из старшей половины ячеек и связан со старшим байтом 16-разрядной шины данных, то L-банк содержит младшую половину ячеек и состыкован с младшим байтом шины данных. Адресные линии А19—А1 применяются для адресации ячейки. Линия А0 определяет байт в ячейке памяти (рис. 6.8).

используется для адресации памяти и портов ВВ. Память на физическом уровне представляет собой набор 16-разрядных ячеек, разбитых на два байтовых банка: Н и L по 512К байт каждый. Если Н-банк состоит из старшей половины ячеек и связан со старшим байтом 16-разрядной шины данных, то L-банк содержит младшую половину ячеек и состыкован с младшим байтом шины данных. Адресные линии А19—А1 применяются для адресации ячейки. Линия А0 определяет байт в ячейке памяти (рис. 6.8).

Рис. 6.8. Физическая (а) и логическая (б) организации памяти

Если А0 = 0, то адресуется либо младший байт, либо слово ячейки в зависимости от длины операнда, иначе при А0 = 1 адресуется только ее старший байт. В обоих случаях операция со старшим байтом разрешена, если  = 0. Этот сигнал является признаком того, что старшая половина шины данных D15—D8 участвует при обмене.

= 0. Этот сигнал является признаком того, что старшая половина шины данных D15—D8 участвует при обмене.

Запись-считывание байтов и размещенных в одной ячейке по четному адресу слов реализуется за один машинный цикл. Обмен со словом, размещенным по нечетному адресу, выполняется за два машинных цикла. Сначала по старшей половине шины данных передается младший байт слова (А0 = 1,  = 0), затем адрес получает приращение и по младшей половине шины данных производится обмен со старшим байтом слова. С учетом этого рекомендуется слова в памяти размещать по четным адресам. К данному замечанию особенно критично содержимое SP, так как обмен со стеком всегда выполняется по словам.

= 0), затем адрес получает приращение и по младшей половине шины данных производится обмен со старшим байтом слова. С учетом этого рекомендуется слова в памяти размещать по четным адресам. К данному замечанию особенно критично содержимое SP, так как обмен со стеком всегда выполняется по словам.

В МП используется логически изолированная от памяти структура BB с физически совмещенным интерфейсом. Для адресации портов BB существует отдельное адресное пространство в 64 К байт.

Адресное пространство портов BB организовано аналогично памяти в виде двух байтовых банков по 32 К байт каждый. Байтовые порты подключаются либо к старшей, либо к младшей половине шины данных. Для равномерного распределения нагрузки рекомендуется их разделить поровну между двумя банками. Шестнадцатиразрядные устройства подсоединяются ко всей шине данных. Однако при нечетном адресе обмен с такими портами будет происходить за два цикла.

Логический раздел единой магистрали между памятью и системой ВВ осуществляют управляющие сигналы, генерируемые МП. Эти сигналы указывают, какую функцию в текущем машинном цикле выполняет магистраль: обмен с памятью или операцию ВВ. Способ формирования сигналов раздела зависит от режима работы микросхемы.

Режим минимальной конфигурации (MN/  = 1) позволяет без дополнительных внешних средств создавать МС простого вида. В этом режиме все необходимые сигналы управления МП вырабатывает сам.

= 1) позволяет без дополнительных внешних средств создавать МС простого вида. В этом режиме все необходимые сигналы управления МП вырабатывает сам.

Рассмотрим более подробно управляющие сигналы этого режима:

ALE Выходной сигнал, стробирующий в такте Т1 адресную информацию.

Используется для ее записи во внешний буферный регистр

Выходной сигнал, который отличает обмен с памятью (

Выходной сигнал, который отличает обмен с памятью (  = 1) от обмена

= 1) от обмена

с портом ВВ (  = 0)

= 0)

Управляющий сигнал, информирующий о направлении обмена. При

Управляющий сигнал, информирующий о направлении обмена. При

= 1 осуществляется цикл записи, в противном случае—цикл чтения.

= 1 осуществляется цикл записи, в противном случае—цикл чтения.

Применяется для управления направлением передачи в шинных буферах

,

,  Строб чтения и строб записи соответственно. Сигнал

Строб чтения и строб записи соответственно. Сигнал  инициирует

инициирует

выдачу данных из памяти или порта ВВ в шину данных. Строб

исполняет процедуру записи данных в память или порт ВВ. Считается,

что данные действительны на фронте

Инверсный сигнал, разрешающий передачу данных через шину данных

Инверсный сигнал, разрешающий передачу данных через шину данных

В режиме максимальной конфигурации (MN/  = 0) управляющая информация передается через шину состояния

= 0) управляющая информация передается через шину состояния  —

—  в закодированном виде согласно табл. 6.15. Диаграмма вывода состояния

в закодированном виде согласно табл. 6.15. Диаграмма вывода состояния  —

—  представлена на рис. 6.9. Дешифрация состояния и формирование необходимых управляющих сигналов возлагается на внешние средства—системный контроллер, который тактируется импульсами CLK.

представлена на рис. 6.9. Дешифрация состояния и формирование необходимых управляющих сигналов возлагается на внешние средства—системный контроллер, который тактируется импульсами CLK.

Таблица 6.15

|

|

| Тип цикла |

|

|

| Тип цикла |

| 0 0 0 | Подтверждение прерывания | 1 0 0 | Выборка команды | ||||

| 0 0 1 | Чтение порта ВВ | 1 0 1 | Чтение памяти | ||||

| 0 1 0 | Запись в порт ВВ | 1 1 0 | Запись в память | ||||

| 0 1 1 | Останов | 1 1 1 | Пассивное состояние |

Рис. 6.9. Временные диаграммы вывода сигналов S2—S0

Код состояния присутствует на этих выводах в части такта Т4 предыдущего цикла, а также тактах Т1 и Т2 текущего цикла. В конце каждого машинного цикла шина  —

—  переводится в пассивное состояние (код 111). Момент окончания пассивного состояния запускает системный контроллер на формирование управляющих сигналов нового цикла в соответствии с кодом

переводится в пассивное состояние (код 111). Момент окончания пассивного состояния запускает системный контроллер на формирование управляющих сигналов нового цикла в соответствии с кодом  —

—  .

.

За счет кодирования основной управляющей информации ряд выводов МП освобождается. Эти выводы применяются для генерации дополнительной управляющей информации, упрощающей построение сложных МС. Так, выходы QS0, QS1 служат для вывода информации о состоянии очереди команд в соответствии с табл. 6.16 и могут быть использованы сопроцессором для отслеживания ее прохождения.

Таблица 6.16

| QS1 | QS0 | Состояние очереди |

| 0 0 | Нет операции | |

| 0 1 | Очистка очереди | |

| 1 0 | Выборка первого байта команды | |

| 1 1 | Выборка следующего байта команды |

Линия  применяется командой WAIT для привязки программ к внешним сигналам. По команде WAIT МП опрашивает линию

применяется командой WAIT для привязки программ к внешним сигналам. По команде WAIT МП опрашивает линию  . При отсутствии сигнала на линии МП переходит в режим с периодической проверкой линии через каждые 5 тактов. Вход может быть использован для синхронизации программы с внешней аппаратурой, например с сопроцессором.

. При отсутствии сигнала на линии МП переходит в режим с периодической проверкой линии через каждые 5 тактов. Вход может быть использован для синхронизации программы с внешней аппаратурой, например с сопроцессором.

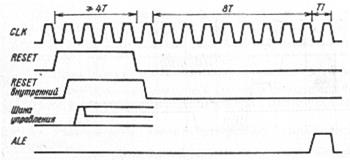

Вход RESET служит для сброса МП в начальное состояние. При запуске одновременно с включением напряжения питания на вход RESET подают сигнал, который после достижения напряжением питания номинального значения выдерживают не менее 50 мкс. При перезапуске МП на вход RESET подают сигнал длительностью не менее четырех периодов тактовой частоты (рис. 6.10).

Рис. 6.10. Пуск микропроцессора ВМ86

Сигнал сброса RESET, синхронизированный тактами CLK, поступает на внутренние узлы МП. Микропроцессор устанавливает флажок IF разрешения прерывания в 0 и переводит свои выходы в состояния, указанные в табл. 6.17, в которых они остаются на все время действия RESET.

Таблица 6.17

| Вывод | Состояние |

AD15—AD0

A19/S6—A16/S3

/S7 /S7

( (  )

DT/ )

DT/  ( (  )

DEN( )

DEN(  ) )

( (  ) )

ALE

HLDA

ALE

HLDA

/ /  — —  / /  QS1—QS0

QS1—QS0

| z z Через 1 в z Через 1 в z Через 1 в z Через 1 в z Через 1 в z Через 1 в z |

После окончания сигнала RESET МП в течении восьми первых тактов устанавливает свои регистры в исходное состояние согласно табл. 6.18 и переходит к выборке команды из ячейки с адресом 0FFFF0H. Как правило, по этому стартовому адресу находится команда межсегментного перехода FAR JMP.

Таблица 6.18

| Регистр | Состояние |

| F | Сброшен |

| IP | 0000H |

| CS | FFFFH |

| DS | 0000H |

| SS | 0000H |

| ES | 0000H |

| Очередь команд | Пусто |

Обработка прерываний. Микропроцессор ВМ86 имеет достаточно простую и эффективную векторную систему обработки прерывания. Каждому запросу поставлен во взаимно однозначное соответствие его вектор, который служит для определения адреса подпрограммы обслуживания прерывания. В МП используется 256 векторов. Способ определения вектора зависит от типа запроса. Рассмотрим более подробно запросы, поступающие от внешней аппаратуры.

Для приема этих запросов служат два входа: NMI—линия немаскируемых запросов и INTR—линия маскируемых векторных запросов. Маской служит разряд IF из флажкового регистра. Состояние флажка IF доступно внешней аппаратуре в тактах Т2—Т4 через шину A18/S5. Прерывание по входу INTR воспринимается всякий раз, когда INTR • IF = 1.

В ответ на запрос по входу INTR МП инициирует процедуру ввода вектора прерывания, состоящую из двух последовательных машинных циклов INTA, разделенных двумя холостыми тактами Т5. В минимальном режиме эти циклы аналогичны циклам ввода (  -циклы), но вместо строба RD генерируется строб INTA и состояние адресной шины не определено. Для максимального режима цикл

-циклы), но вместо строба RD генерируется строб INTA и состояние адресной шины не определено. Для максимального режима цикл  идентифицируется кодом на шине

идентифицируется кодом на шине  —

—  , а генерация

, а генерация  -строба возлагается на системный контроллер.

-строба возлагается на системный контроллер.

Первый INTA-цикл информирует интерфейс МС о начале процедуры. В течение этого цикла никаких данных МП не принимает. Во втором цикле по младшей половине 16-разрядной шины принимается вектор прерывания, который лежит в диапазоне 0—255. В максимальном режиме с такта Т2 первого цикла до такта Т2 второго генерируется сигнал  , препятствующий захвату магистрали между INTA-циклами. В минимальном режиме сигнал

, препятствующий захвату магистрали между INTA-циклами. В минимальном режиме сигнал  = 0, что свидетельствует об обмене с портом ВВ. Состояние входа HOLD до конца процедуры игнорируется.

= 0, что свидетельствует об обмене с портом ВВ. Состояние входа HOLD до конца процедуры игнорируется.

Вход немаскируемого прерывания NMI является динамическим. Запрос по нему воспринимается только при поступлении положительного перепада сигнала, который затем должен быть удержан в активном состоянии более двух тактов. Запросам по входу NMI присвоен фиксированный вектор 2, поэтому процедура ввода номера для них не выполняется.

Кроме двух источников внешних прерываний МП имеет три источника специальных внутренних прерываний: по переполнению, по ошибке деления и при пошаговой трассировке. Прерывание по переполнению возникает в результате исполнения команды INTO, если флажок переполнения OF устанавливается в 1. Этот тип прерывания имеет вектор, равный 4.

Прерывание по ошибке деления происходит, если частное операции деления DIV или IDIV превышает максимально допустимое значение, например при делении на нуль. Прерыванию по ошибке деления присвоен вектор 0. Эти два вида прерывания (по переполнению и по ошибке деления) полезны для обнаружения арифметических ошибок.

Прерывание пошаговой трассировки вырабатывается после исполнения любой команды, перед началом выполнения которой флажок трассировки TF был установлен в 1. Прерывание реализует оперативную отладку программ в режиме пошаговой работы. Вектор данного типа прерывания равен 1.

Существует еще один источник внутреннего векторного прерывания—программный. Этот тип прерываний возникает при исполнении двухбайтовой команды INT vect. В этой команде vect—число из диапазона 0—255, которое является вектором прерывания. Определен также однобайтовый вариант команды INT 3, используемой для организации контрольных точек останова в отлаживаемой программе. Программное прерывание дублирует любой тип аппаратных прерываний, что может быть полезным для проверки подпрограмм их обслуживания.

Вектор прерывания, считанный с шины из кода команды или определенный по типу радиального запроса, служит индексом обращения к таблице прерываний IDT (рис. 6.11). Таблица размещается в первом 1К байте памяти. Под каждый вектор отводится по 4 байта, в которых хранятся начальные состояния IP и CS подпрограммы обслуживания в указанной последовательности. После определения вектора прерывания МП считывает значение IP и CS из таблицы IDT. Адресом новых значений IP и CS служит учетверенное значение вектора vect. При формировании физического адреса обращения к таблице никакие сегментные регистры не используются, о чем свидетельствуют сигналы состояния S4 = 1, S3 = 0.

Рис. 6.11. Таблица прерываний IDT

Затем МП сбрасывает флажки IF и TF, выполняет загрузку в стек старого содержимого регистров F и CS, выбирает код операции первой команды подпрограммы обслуживания и «вталкивает» в стек прежнее значение IP. Эти действия он выполняет в указанной последовательности. После записи в стек старого содержимого IP МП возобновляет свою обычную работу. Сигнал С5 (состояние флажка IF) устанавливается в 0 в такте Т2 после считывания нового значения CS.

Количество тактов от конца команды и до начала выполнения подпрограммы обслуживания зависит от типа прерывания. Для запросов по входу INTR оно равно 61, для программных прерываний и прерываний при пошаговой трассировке—51, для команды INT 3—52, для команды INT 0—53 такта. Все процедуры прерываний должны оканчиваться командой IRET.

Если в МП поступает одновременно несколько запросов на прерывания, он обслуживает их в соответствии с приоритетом:

Прерывание по флагу TF (высший приоритет)

Немаскируемое прерывание NMI

Программное прерывание INT vect

Векторное прерывание INTR (низший приоритет)

Эта последовательность нарушается, когда одновременно три запроса с высшим приоритетом (за исключением INTR) активны. В данном случае последовательность обработки следующая:

Программное прерывание INT vect

Немаскируемое прерывание NMI

Прерывание по флажку TF

Управление захватом шины. Микропроцессор имеет мощные программно-аппаратные средства управления захватом шины. Эти средства применяются для построения каналов ПДП и мультипроцессорных МС.

В минимальном режиме для этих целей используются вход HOLD принимающий запросы доступа к шине, и выход HLDA, генерирующий сигнал подтверждения доступа. Вход HOLD является асинхронным и опрашивается по фронту каждого тактового импульса. При поступлении напряжения высокого уровня МП в середине последнего такта текущего цикла канала Т4 или холостого такта Т5 выдает сигнал подтверждения захвата по выходу HLDA. Одновременно с этим МП переводит в высокоомное состояние шину AD, шины  /S7, A19/S6—A16/S3 и управляющие линии

/S7, A19/S6—A16/S3 и управляющие линии  ,

,  , DT/

, DT/  ,

,  ,

,  , логически отключаясь от магистрали. При снятии сигнала HOLD МП в следующем такте сбрасывает сигнал подтверждения HLDA и возвращает себе управление магистралью (рис. 6.12, а).

, логически отключаясь от магистрали. При снятии сигнала HOLD МП в следующем такте сбрасывает сигнал подтверждения HLDA и возвращает себе управление магистралью (рис. 6.12, а).

Рис. 6.12. Временные диаграммы захвата шины для минимального (а) и максимального (б) режимов

В максимальном режиме для управления захватом шины МП служат линии  /

/  ,

,  /

/  и

и  .

.

Двунаправленные линии  /

/  и

и  /

/  имеют одно и то же функциональное назначение, однако приоритет у линии

имеют одно и то же функциональное назначение, однако приоритет у линии  /

/  выше. Процедура захвата шины в максимальном режиме состоит из трех этапов: запроса, разрешения, освобождения (рис. 6.12, б). Процедура на захват шины инициируется внешним модулем подачей на один из входов

выше. Процедура захвата шины в максимальном режиме состоит из трех этапов: запроса, разрешения, освобождения (рис. 6.12, б). Процедура на захват шины инициируется внешним модулем подачей на один из входов  /

/  или

или  /

/  импульса длительностью Т. В конце текущего машинного цикла или после очередного холостого такта Т5 МП генерирует ответный импульс, подтверждающий захват. Этот импульс передается по той же линии и имеет длительность Т. В следующем такте МП переводит выходы

импульса длительностью Т. В конце текущего машинного цикла или после очередного холостого такта Т5 МП генерирует ответный импульс, подтверждающий захват. Этот импульс передается по той же линии и имеет длительность Т. В следующем такте МП переводит выходы  /S7, A19/S6—A16/S3, AD15—AD0, а также линии

/S7, A19/S6—A16/S3, AD15—AD0, а также линии  —

—  LOCK и

LOCK и  в третье состояние, логически отключаясь от шины. После окончания цикла обмена внешний модуль генерирует еще один импульс длительностью Т, который извещает о возвращении управления шиной спустя два такта. Обмен импульсами должен происходить синхронно. Запрос по входу

в третье состояние, логически отключаясь от шины. После окончания цикла обмена внешний модуль генерирует еще один импульс длительностью Т, который извещает о возвращении управления шиной спустя два такта. Обмен импульсами должен происходить синхронно. Запрос по входу  /

/  , пришедший одновременно с запросом

, пришедший одновременно с запросом  /

/  , будет разрешен спустя один-два такта после освобождения магистрали. Запросы на захват шины имеют более высокий приоритет, чем прерывания.

, будет разрешен спустя один-два такта после освобождения магистрали. Запросы на захват шины имеют более высокий приоритет, чем прерывания.

—инверсный программно-управляемый выход блокировки захвата шины. Сигнал вырабатывается по префиксу LOCK и поддерживается в течение всего цикла выполнения команды, следующей за ним. При блокировке МП не воспринимает запросы на захват шины, обеспечивая себе возможность единоличного доступа к памяти. Такой тип доступа важен при организации семафоров. Сигнал блокировки

—инверсный программно-управляемый выход блокировки захвата шины. Сигнал вырабатывается по префиксу LOCK и поддерживается в течение всего цикла выполнения команды, следующей за ним. При блокировке МП не воспринимает запросы на захват шины, обеспечивая себе возможность единоличного доступа к памяти. Такой тип доступа важен при организации семафоров. Сигнал блокировки  не влияет на обработку запросов прерывания. В минимальном режиме сигнал

не влияет на обработку запросов прерывания. В минимальном режиме сигнал  отсутствует. Однако префикс LOCK все же используется для задержки выдачи подтверждения сигнала HLDA на время выполнения команды.

отсутствует. Однако префикс LOCK все же используется для задержки выдачи подтверждения сигнала HLDA на время выполнения команды.

Дата добавления: 2019-02-07; просмотров: 838;