Новые системные регистры микропроцессоров i80x86

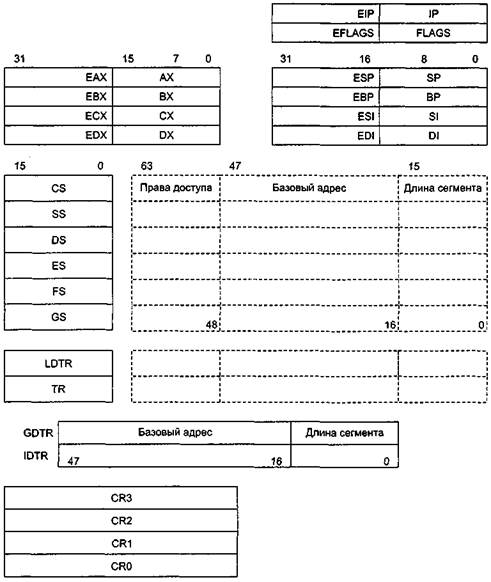

Основные регистры микропроцессора i80x86, знание которых необходимо для понимания защищенного режима работы, приведены на рис. 4.2. На этом рисунке следует обратить внимание на следующее:

- указатель команды (EIP) — это 32-разрядный регистр, младшие 16 разрядов которого представляют регистр IP;

- регистр флагов (EFLAGS) — это 32-разрядный регистр, младшие 16 разрядов которого представляют регистр FLAGS;

- регистры общего назначения ЕАХ, ЕВХ, ЕСХ, EDX, а также регистры ESP, EBP, ESI, EDI 32-разрядные, однако их младшие 16 разрядов представляют собой известные регистры АХ, ВХ, CX,DX, SP, BP, SI, DI;

- сегментные регистры CS, SS, DS, ES, FS, GS 16-разрядные, при каждом из них пунктиром изображены скрытые от программистов (недоступные никому, кроме собственно микропроцессора) 64-разрядные регистры, в которые загружаются дескрипторы соответствующих сегментов;

' На самом деле, поскольку происходит именно сложение и каждое из слагаемых может иметь значение в интервале от нуля до 2"' - 1= 65 535 = 64 Кбайт, мы можем указать адрес начала сегмента, равный FFFFFFFF00H, и к нему прибавить смещение FFFFFFFFH. В этом случае мы получим переполнение разрядной сетки, но для современных 32-разрядных процессоров (и для уже забытого i80286) имеется возможность указать первые 64 Кбайт выше первого мегабайта.

' На самом деле, поскольку происходит именно сложение и каждое из слагаемых может иметь значение в интервале от нуля до 2"' - 1= 65 535 = 64 Кбайт, мы можем указать адрес начала сегмента, равный FFFFFFFF00H, и к нему прибавить смещение FFFFFFFFH. В этом случае мы получим переполнение разрядной сетки, но для современных 32-разрядных процессоров (и для уже забытого i80286) имеется возможность указать первые 64 Кбайт выше первого мегабайта.

104________________ Глава 4, Особенности архитектуры микропроцессоров j80x86

Рис. 4.2. Основные системные регистры микропроцессоров i80x86

- при 16-разрядном регистре-указателе на локальную таблицу дескрипторов ( Local Descriptor Table Register, LDTR) также имеется «теневой» (скрытый от программиста) 64-разрядный регистр, в который микропроцессор заносит дескриптор, указывающий на таблицу дескрипторов сегментов задачи, описывающих ее локальное виртуальное адресное пространство;

- 16-разрядный регистр задачи (Task Register, TR) указывает на дескриптор в глобальной таблице дескрипторов, который позволяет получить доступ к дескрип-

Адресация в 32-разрядных микропроцессорах j80x86_________________________ 105

тору сегмента состояния задачи (Task State Segment, TSS) — информационной структуре, которую поддерживает микропроцессор для управления задачами;

- 48-разрядный регистр GDTR (Global Descriptor Table Register) глобальной таб

лицы дескрипторов (Global Descriptor Table, GDT) содержит как дескрипторы

общих сегментов, так и специальные системные дескрипторы, в частности,

в GDT находятся дескрипторы, с помощью которых можно получить доступ

к сегментам TSS;

- 48-разрядный регистр таблицы дескрипторов прерываний (IDTR) содержит

информацию, необходимую для доступа к таблице прерываний (IDT);

- 32-разрядные регистры CR0-CR3 являются управляющими. Помимо перечисленных имеются и некоторые другие регистры.

Управляющий регистр CR0 содержит целый ряд флагов, которые определяют режимы работы микропроцессора. Подробности об этих флагах можно найти, например, в [1, 8, 20]. Мы же просто ограничимся тем фактом, что самый младший бит РЕ (Protect Enable) этого регистра определяет режим работы процессора. При РЕ = 0 процессор функционирует в реальном режиме работы, а при единичном значении микропроцессор переключается в защищенный режим. Самый старший бит регистра CR0 — бит PG (PaGing) — определяет, включен (PG =1) или нет (PG = 0) режим страничного преобразования адресов.

Регистр CR2 предназначен для размещения в нем адреса подпрограммы обработки страничного исключения, то есть в случае страничного механизма отображения памяти обращение к отсутствующей странице будет вызывать переход на соответствующую подпрограмму диспетчера памяти, и для определения этой подпрограммы потребуется регистр CR2.

Регистр CR3 содержит номер физической страницы, в которой располагается таблица каталога таблиц страниц текущей задачи. Очевидно, что, приписав к этому номеру нули, мы попадем на начало этой страницы.

Дата добавления: 2016-09-20; просмотров: 1438;