Альтернативные функции.

Из-за ограниченного количества выводов корпуса ИМС микроконтроллера, большинство выводов используется для выполнения двух функций - в качестве линий портов и для альтернативных функций

- Порты P0 и Р2используются при обращении к внешней памяти. При этом на выходах P0 младший байт адреса внешней памяти мультиплексируется с вводимым/выводимым байтом. Выходы Р2 содержат старший байт адреса внешней памяти, если адрес 16-разрядный. При использовании восьмиразрядного адреса портом Р2 можно пользоваться для ввода-выввода информации обычным образом. При обращении к внешней памяти в P0 автоматически заносятся 1 во все биты. Информация в Р2 при этом остается неизменной.

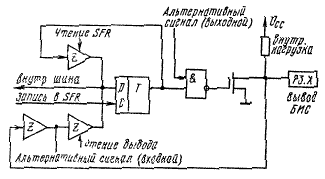

- Порт P3помимо обычного ввода и вывода информации используется для формирования и приема специальных управляющих и информационных сигналов. Разряды порта (все или частично) при этом могут выполнять следующие альтернативные функции:

Альтернативные функции могут быть активированы только в том случае, если в соответствующие биты порта P3 предварительно занесены 1. Неиспользуемые альтернативным образом разряды могут работать как обычно.

| Вывод порта | Альтернативная функция |

| РЗ.0 | RXD - вход последовательного порта |

| Р3.1 | TXD - выход последовательного порта |

| РЗ.2 | INT0 - внешнее прерывание 0 |

| Р3.3 | INT1 - внешнее прерывание 1 |

| РЗ.4 | Т0 - вход таймера-счетчика 0 |

| РЗ.5 | Т1 - вход таймера-счетчика 1 |

| РЗ.6 | WR - строб записи во внешнюю память данных |

| РЗ.7 | RD - строб чтения из внешней памяти данных |

Устройство портов.

Каждый из портов содержит регистр-защелку (SFR P0 — SFR P3), выходную цепь и входной буфер.

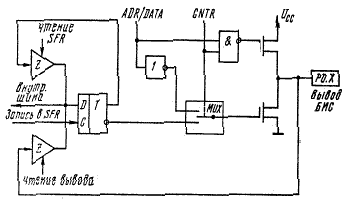

Рис.3.Порт P0

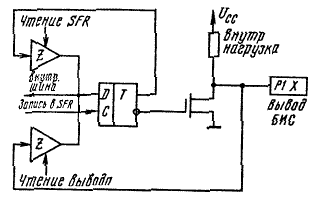

Рис.4.Порт P1

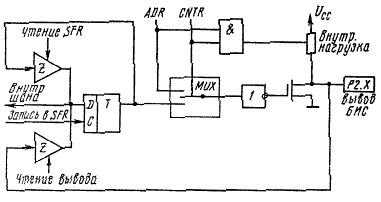

Рис.5.Порт P2

Рис.6.Порт P3

На рисунке изображены функциональные схемы регистров-защелок и буферов ввода-вывода всех портов микро-ЭВМ 8051. Каждый из разрядов регистра-защелки SFR является D-триггером, информация в который заносится с внутренней шины данных микроконтроллера по сигналу «Запись в SFR Pх» (х= 0, 1, 2, 3) от центрального процессорного элемента (CPU). С прямого выхода D-триггера информация мажет быть выведена на внутреннюю шину по сигналу «Чтение SFR Pх» от CPU, а с вывода микросхемы («из внешнего мира») по сигналу «Чтение выводов Pх». Одни команды активизируют сигнал «Чтение SFR PI», другие - «Чтение выводов РI».

Дата добавления: 2016-03-27; просмотров: 1204;