Формирование физического адреса в микропроцессоре Intel 8086

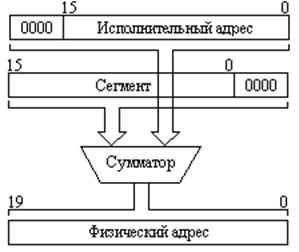

Адресное пространство микропроцессора i8086 составляет 1 Мбайт и обеспечивается 20-разрядной шиной адреса. Логически память разбивается на сегменты размером 64 Кбайт. Физический адрес (РА) памяти, поступающий на шину адреса микропроцессора, состоит из двух 16-битных частей - адреса сегмента (Seg) и исполнительного адреса (ЕА), суммируемых со смещением 4 бита. Сдвиг адреса сегмента на 4 бита влево эквивалентен его умножению на 16, т.е. физический адрес вычисляется как РА = 16 X Seg + ЕА. Адрес сегмента может храниться в одном из сегментных регистров: CS, DS, SS или ES.

|

| Рис. 5.5 Формирование физического адреса |

Исполнительный адрес, также называемый эффективным адресом, может быть константой, содержимым регистра, ячейки памяти или суммой нескольких величин (например, двух регистров и константы), но эта сумма является 16-разрядной, т.к. перенос игнорируется. Таким образом, физический адрес никогда не перейдет границу 64-килобайтного сегмента, на начало которого указывает текущий сегментный указатель.

Способы адресации микропроцессора

Регистровая адресация.Операнд (байт или слово) находится в регистре. Этот способ применим ко всем программно адресуемым регистрам микропроцессора.

Пример:

push es

mov dx,cx

xchg al,ah

Непосредственная адресация.Операнд (байт или слово) записывается непосредственно в коде команды.

Пример:

mov ax,2DF4h

mov dh,C2h

Прямая адресация к памяти.В команде указывается символическое обозначение ячейки памяти, над содержимым которой требуется выполнить операцию, либо ее адрес, заключенный в квадратные скобки.

Пример:

Mov dl,_byte

Mov word,cx

mov [00C1],bh

При использовании прямой адресации к памяти предварительно необходимо настроить какой-либо сегментный регистр на начало того участка памяти, в котором находится адресуемая ячейка.

Базовая и индексная адресация к памяти.В этом случае, относительный адрес ячейки памяти находится в регистре, обозначение которого заключается в квадратные скобки. При использовании регистра BX адресацию называют базовой, при использовании регистров SI или DI– индексной. При адресации через регистры BX,SI или DI в качестве сегментного регистра, по умолчанию, используется сегментный регистр DS. Однако, в случае необходимости можно заменить используемый по умолчанию сегментный регистр посредствам префикса замены регистра.

Пример:

mov dl,[bx]

mov es:[di],cx

mov [si],ax

Базовая и индексная адресации к памяти со смещением.Исполнительный адрес операнда определяется суммой содержимого базового или индексного регистра (BX, BP, SI, DI) и смещения, указанного в коде команды.

Пример:

mov dx,[di+12h]

mov [si+3FC0h],al

mov cx,mem[si]

mov 2[bp],dl

При этом возможно несколько вариантов записи:

Регистр вместе со смещением записывается в квадратных скобках;

Записывается мнемоническое обозначение некоторого массива элементов, после которого в квадратных скобках указывается базовый или индексный регистр;

Записывается числовое смещение, после которого в квадратных скобках базовый или индексный регистр;

При использовании регистра BP необходимо помнить, что в качестве сегментного регистра по умолчанию подразумевается регистр SS.

Базовая и индексная адресация к памяти со смещением использует не физический, а эффективный адрес ячейки памяти.

Для двухоперандных команд возможны 3 варианта размещения операндов:

1) источник и приемник в регистре;

2) источник в регистре, приемник в памяти;

3) источник в памяти, приемник в регистре.

Вариант, когда оба операнда в памяти запрещен!

Базово-индексная адресация к памяти.Исполнительный адрес операнда определяется суммой содержимого базового и индексного регистров. Для микропроцессора i8086 допускается использование следующих пар регистров:

[BX][SI]

[BX][DI]

[BP][SI]

[BP][DI]

Если в качестве базового регистра выступает BX, то в качестве сегментного регистра по умолчанию подразумевается регистр DS; при использовании в качестве базового регистра BP сегментным регистром по умолчанию считается SS. При необходимости можно явно указать требуемый сегментный регистр.

Пример:

mov cx,[bx][si]

mov [bp+di],ax

mov es:[bp+si],ah

Базово-индексная адресация к памяти со смещением.Относительный адрес операнда определяется суммой трех составляющих: содержимого базового и индексного регистров, а также дополнительного смещения. Допускается использование тех же регистровых пар, что и в базово-индексном методе адресации без смещения. Те же правила распространяются и на использование сегментных регистров.

Пример:

mov mem[bx][di],dx

mov 4[bp][si],ch

mov bx,[bx+di+0C21h]

Значительная часть рассмотренных выше способов адресации служит для обращения к ячейкам памяти. Однако, один и тот же результат можно получить, используя различные методы адресации. Например, все три приведенные ниже команды:

mov dl,mem+3

mov dl,mem[bx] ;в bx заранее занесено число 3

mov dl,[si][di] ;в bx заранее занесено число 3, а в si – смещение memприведут к загрузке в регистр DL четвертого элемента массива mem (если выполнятся условия приведенные в комментариях). Но, стоит отметить, что различные методы адресации занимают различный объем памяти и выполняются за различное число тактов микропроцессора. Таким образом, тщательный подбор методов адресации, используемых в вашем коде, может в какой- то степени увеличить скорость выполнения программы или уменьшить объем необходимой памяти, а иногда и то и другое.

Система команд микропроцессора изучается в другой дисциплине и поэтому в данном учебном пособии не приводится.

Контрольные вопросы и задания

1. Что входит в регистровую модель микропроцессора К1810ВМ86?

2. Какую структуру имеет регистр флагов?

3. Как используется бит направления DF?

4. Объясните назначение блоков в минимально укомплектованной микропроцессорной системе.

5. Чем отличаются минимальный и максимальный режимы работы микропроцессора?

6. Как формируются сигналы шины управления в системе средней сложности?

7. Опишите организацию памяти микропроцессора К1810ВМ86.

8. Как работает сумматор адреса микропроцессора К1810ВМ86?

9. Какие методы адресации использует микропроцессор К1810ВМ86?

10. Расскажите о назначении сегментных регистров.

11. Что такое эффективный адрес памяти?

12. Какой сегментный регистр будет использоваться для базово-индексной адресации через регистр BP?

Дата добавления: 2016-03-10; просмотров: 3206;