Плюс — двухмодульные отказоустойчивые вычислительные системы или способ восстановления вычислительного процесса в дублированной системе на основе двух дополнительных модулей.

Эта схема имеет возможности для восстановления после возникновения двух сбоев на одном интервале. Каждый из дополнительных модулей состоит из двух ВМ, также как и основные модули. Это позволяет применять данную схему в мультипроцессорных системах с дублированными модулями. Если в одном из дублированных модулей системы, выполняющем задачу реального времени и имеющем высокий приоритет, обнаружен сбой, то он (модуль) может обратиться к другому дублированному модулю, выполняющему в это время задачу с меньшим приоритетом, и прервать его работу. Таким образом, его можно использовать как дополнительный модуль для восстановления от сбоев. Другими словами, этим схемам не требуется специальных модулей, предназначенных для восстановления, наоборот, они имеют преимущество использовать находящиеся здесь же дублированные модули, что позволяет им генерировать процесс восстановления быстрее и с большей устойчивостью к сбоям, чем схемам, нуждающимся в одном дополнительном модуле для восстановления (см. главу 4).

Основные принципы схемы.

Пусть число пар вычислительной системы равно m, каждая пара вычислительной системы состоит из двух основных вычислительных модулей А и В. Каждая i-ая пара занята решением задачи со временем выполнения Ti. В случае сбоя в работе любой пары процессора для восстановления вычислительного процесса используются два дополнительных вычислительных модуля S1 и S2.

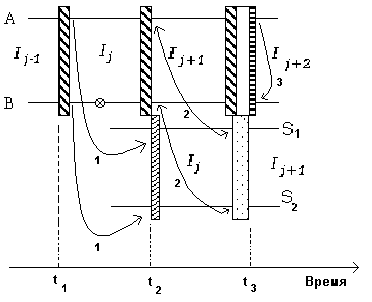

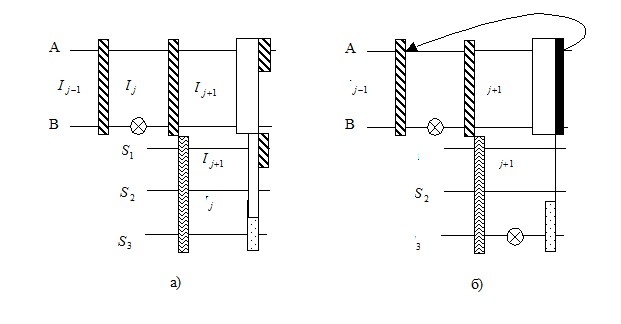

На рис. 2.6. изображено выполнение двумя модулями обработки, обозначенными А и B, одной и той же задачи. Примем, что в модуле В возник сбой, а другие модули свободны от сбоев на интервале контроля. На рис. 2.6 этот интервал обозначен Ij. Результаты в модулях А и В могут не совпадать в конце интервала Ij. Это несоответствие инициализируется восстановлением вычислительного процесса одновременно на двух дополнительных вычислительных модулях S1 и S2 следующим образом:

1) Не совпадающие результаты контрольных точек двух модулей сохраняются. Предыдущий совпадающий контрольный результат загружается в дополнительные модули S1 и S2. Программа задачи основной пары А и В должна быть загружена в модули S1 и S2. Интервал Ij решаемой задачи пары А и В выполняется в дополнительных модулях S1 и S2. Одновременно пара основных модулей А и В продолжает выполнение следующего интервала контрольной точки Ij+1 .

2) После того, как дополнительные модули S1 и S2 завершают интервал Ij, результаты дополнительных модулей сравниваются с несовпадающими результатами, которые получили модули A и B в интервале контрольной точки. Результаты модулей S1 и S2 не будут совпадать с результатом B в конце интервала Ij, и совпадать с A.

3) Когда определено, какой из модулей совпал с дополнительными, а в нашем случае модуль В является неправильным, а модуль A свободным от сбоя, то состояние модуля A копируется в модуль В. Следовательно, состояние модуля В идентично состоянию модуля A. Теперь, и A, и B корректны.

4) Параллельный механизм повторения затем продолжает определять, имеет ли модуль А сбои на интервале Ij+1. Полное объяснение этого процесса приведено ниже.

1- Состояния копируются в дополнительные модули.

2 - Сравниваются состояния дополнительных модулей с состояниями модулей А и B.

3 – Состояние модуля А копируется в B.

Рис. 2.6. Плюс — двухмодульные отказоустойчивые вычислительные системы:

Основные принципы схемы.

Ниже показаны шесть (1-6) возможных ситуаций развития событий при выполнении задачи в схеме «плюс — двухмодульные отказоустойчивые вычислительные системы».

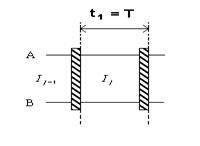

Ситуация 1.В процессорных модулях Аи Вна интервале  нет ошибок. После этого выполняется следующий интервал (Рис. 2.7). На рисунке t1 показывает, что в этой ситуации нет потерь времени в выполнении интервала задачи.

нет ошибок. После этого выполняется следующий интервал (Рис. 2.7). На рисунке t1 показывает, что в этой ситуации нет потерь времени в выполнении интервала задачи.

Рис. 2.7. Ситуация 1.

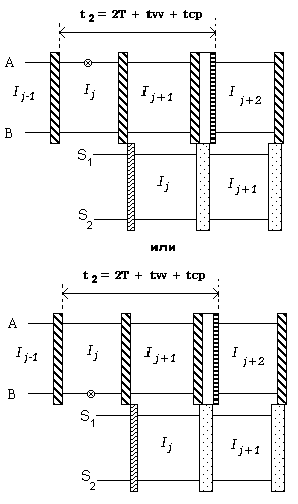

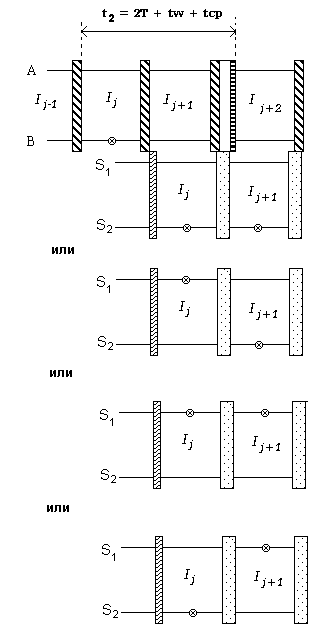

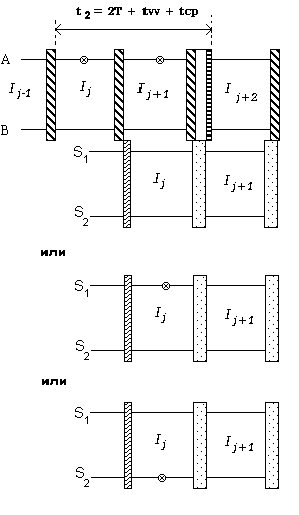

Ситуация 2. В этом случае схема не потеряла ни одного интервала в процессе восстановления. t2 показывает время, которое потребовалось паре ВМ для восстановления из этой ситуации. В этой ситуации возможны четыре случая:

Рис. 2.8. Ситуация 2а.

2 a). Один сбой на интервале IJ. На интервалах IJ+1 и IJ+2 к выполнению задачи на основных модулях подключаются дополнительные модули, выполняющие соответственно интервалы задачи IJ и IJ+1, при этом на этих интервалах сбои отсутствуют (Рис. 2.8).

2 b). Один сбой на интервале IJ в одном из основных модулей, и один сбой в одном из дополнительных модулей на интервале  (Рис. 2.9).

(Рис. 2.9).

Рис. 2.9.. Ситуация 2b.

2 c). Один сбой на интервале IJ в одном из основных модулей, и один сбой в одном (любом) дополнительном модуле на интервале  , и один сбой в одном (любом) дополнительном модуле на интервале

, и один сбой в одном (любом) дополнительном модуле на интервале  (Рис. 2.10).

(Рис. 2.10).

.

Рис. 2.10. Ситуация 2с.

2 d). На интервале IJ имеется сбой в одном из основных модулей, на интервале IJ+1 имеется сбой в том же модуле, и нет сбоев, или один сбой в дополнительном модуле на интервале IJ+1 (Рис. 2.11).

Рис. 2.11. Ситуация 2d.

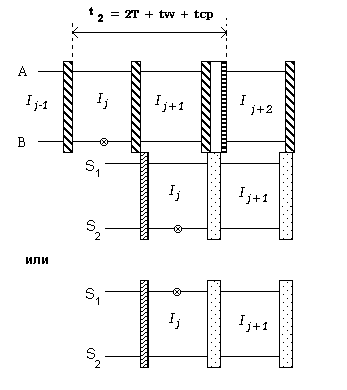

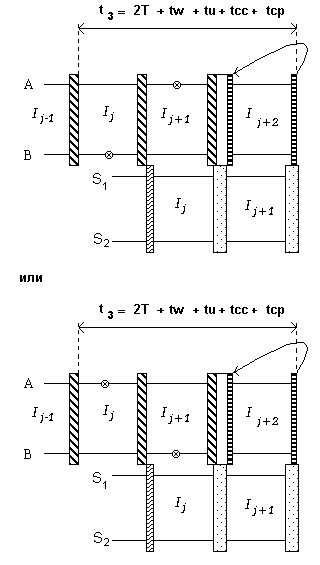

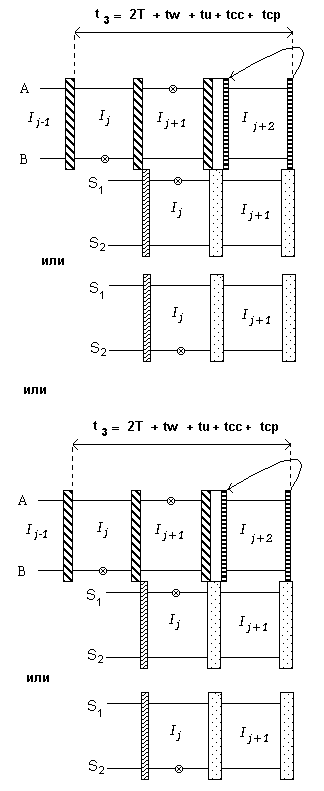

Ситуация 3.В этом случае схема успевает восстановить 2 интервала задачи с помощью дополнительных модулей, но в течение трех интервалов времени, поэтому третий (последний) интервал задачи теряет. t3 показывает время, которое потребовалось паре ВМ для восстановления из этой ситуации. В этой ситуации имеются два возможных случая:

3 a). На интервале IJ имеется сбой в одном основном модуле, на интервале IJ+1 имеется сбой в другом основном модуле. При работе дополнительных модулей сбои отсутствуют (Рис. 2.12).

Рис. 2.12. Ситуация 3a.

3 b). На интервале IJ имеется сбой в одном из основных модулей, на интервале IJ+1 имеется сбой в другом основном модуле и один сбой в дополнительном модуле на интервале  (Рис. 2.13).

(Рис. 2.13).

Рис. 2.13. Ситуация 3b.

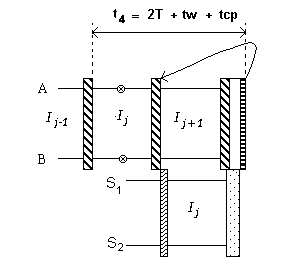

Ситуация 4. В этой ситуации показывается, что процесс восстановления с помощью дополнительных модулей позволяет восстановить 1 интервал задачи, но потерян второй интервал. t4 показывает время, которое потребовалось паре ВМ для восстановления из этой ситуации. На интервале  происходит сбой в обоих основных модулях (Рис. 2.14).

происходит сбой в обоих основных модулях (Рис. 2.14).

Рис. 2.14. Ситуация 4

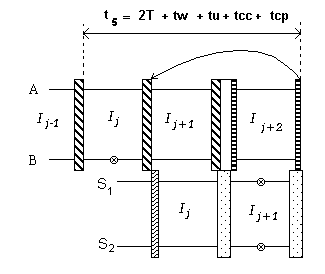

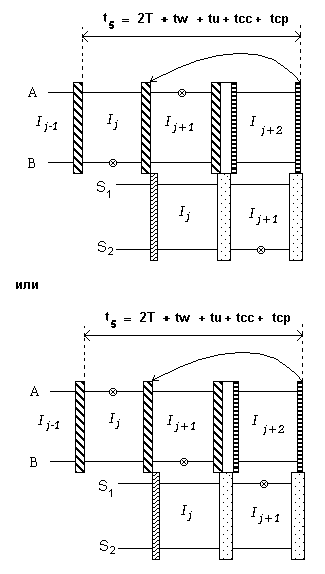

Ситуация 5. В этой ситуации показывается, что процесс восстановления позволяет восстановить первый интервал задачи, но теряются два следующих. t5 показывает время, которое потребовалось паре ВМ для восстановления. В этой ситуации имеется два возможных случая:

5 a) На интервале Ij происходит сбой в одном из основных модулей и имеется сбой в двух дополнительных модулях на интервале Ij+2 (Рис. 2.15).

Рис. 2.15 . Ситуация 5a.

5 b) На интервале IJ имеется сбой в одном из основных модулей, на интервале IJ+1 имеется сбой в другом основном модуле и один сбой в дополнительном модуле на интервале IJ+1 (Рис. 2.16).

Рис. 2.16. Ситуация 5b.

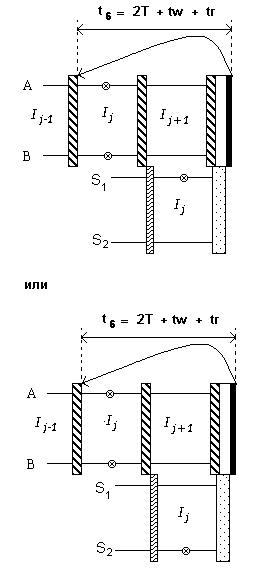

Ситуация 6. Эта ситуация показывает, что, несмотря на то, что был запущен процесс восстановления, это не помогло восстановлению ни одного интервала задачи (Рис. 2.17). Здесь t6 показывает время, которое в данном случае потеряно.

На интервале  происходит сбой в двух основных модулях и один сбой в дополнительном модуле.

происходит сбой в двух основных модулях и один сбой в дополнительном модуле.

Рис. 2.17. Ситуация 6.

Схема с двукратным резервированием задачи с использованием тройного дополнительного модуля (Double Modular Redundant with Forward recovery - DMRF)

В отличие от RFCS-схемы, DMRF-схема [56] использует три свободных модуля для восстановления вычислительного процесса. Процесс восстановления производится за один шаг.

В зависимости от места возникновения ошибки, в DMRF-схеме возможны три сценария, обозначенные как А - С.

(A) Нет ошибок: На интервале  в паре процессорных модулей A и B нет ошибок. После этого выполняется следующий интервал.

в паре процессорных модулей A и B нет ошибок. После этого выполняется следующий интервал.

(B) Одна ошибка: Эта ситуация имеет место в случае, когда в единственном модуле возникает ошибка на интервале  (рис. 2.18. (а)).

(рис. 2.18. (а)).

Рис. 2.18. Возможные ситуации при восстановлении вычислительного процесса в DMRF-схеме. а – восстановление без отката назад; б – откат после интервала повтора.

Предположим, что на интервале  возникла ошибка в процессорном модуле B. После ее обнаружения для восстановления вычислительного процесса дополнительно подключаются три свободных модуля.

возникла ошибка в процессорном модуле B. После ее обнаружения для восстановления вычислительного процесса дополнительно подключаются три свободных модуля.

Шаг 1: Состояния процессорных модулей А и В, выполняющих задачу, копируются в свободные модули  и

и  . Состояние третьего свободного модуля

. Состояние третьего свободного модуля  приводится в соответствие с состоянием модулей А и В в контрольной точке

приводится в соответствие с состоянием модулей А и В в контрольной точке  .

.

Шаг 2: После завершения выполнения  интервала

интервала  , его контрольная точка сравнивается с

, его контрольная точка сравнивается с  и

и  . Поскольку А и

. Поскольку А и  завершили интервал

завершили интервал  без ошибок, их контрольные точки совпадают. Поэтому модуль А рассматривается как безошибочный на интервале

без ошибок, их контрольные точки совпадают. Поэтому модуль А рассматривается как безошибочный на интервале  .

.

Шаг 3: Модули А и  продолжают работу, и процесс восстановления на этом можно считать законченным.

продолжают работу, и процесс восстановления на этом можно считать законченным.

(C) Две ошибки: В данной ситуации два модуля завершили  с ошибкой. Восстановление не является успешным и система производит откат назад к последней корректной контрольной точке (рис. 2.18. (б)).

с ошибкой. Восстановление не является успешным и система производит откат назад к последней корректной контрольной точке (рис. 2.18. (б)).

Сравнение  с

с  и

и  выявит их несовпадение (поскольку или в обоих основных процессорах, или в одном из основных и свободном процессоре была ошибка на интервале

выявит их несовпадение (поскольку или в обоих основных процессорах, или в одном из основных и свободном процессоре была ошибка на интервале  ). После этого производится откат к последней безошибочной контрольной точке.

). После этого производится откат к последней безошибочной контрольной точке.

При возникновении ошибки на последнем интервале выполнения задачи восстановление вычислительного процесса производится путем повторного выполнения этого интервала.

Дата добавления: 2016-01-11; просмотров: 703;