Регистры специального назначения

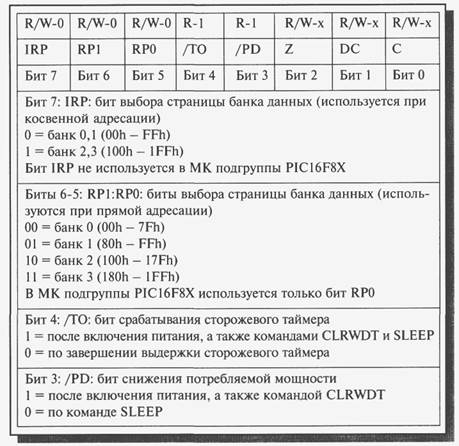

Регистр статуса (STATUS) содержит признаки операции (арифметические флаги) АЛУ, состояние контроллера при сбросе и биты выбора страниц для памяти данных. Назначение бит регистра приведено в табл. 5.3.

Табл. 5.3. Назначение бит регистра STATUS (адрес 03h, 83h).

Табл. 5.3. Назначение бит регистра STATUS (адрес 03h, 83h) (продолжение).

Здесь и далее: R — читаемый бит; W — записываемый бит; S — устанавливаемый бит; U — неиспользуемый бит (читается как «0»); -n = 0 или 1 — значение бита после сброса.

Регистр статуса доступен для любой команды так же, как любой другой регистр. Однако если регистр STATUS является регистром назначения для команды, влияющей на биты Z, DC или С, то запись в эти три бита запрещается. Кроме того, биты /ТО и /PD устанавливаются аппаратно и не могут быть записаны в статус программно. Это следует иметь в виду при выполнении команды с использованием регистра статуса. Например, команда CLRF STATUS обнулит все биты, кроме битов /ТО и /PD, а затем установит бит Z=l. После выполнения этой команды регистр статуса может и не иметь нулевого значения (из-за битов /ТО и /PD) STATUS=000uuluu, где u — неизменяемое состояние. Поэтому рекомендуется для изменения регистра статуса использовать только команды битовой установки BCF, BSF, MOVWF, которые не изменяют остальные биты статуса. Воздействие всех команд на биты статуса рассматривается в разделе «Описание системы команд».

Регистр конфигурации (OPTION) является доступным по чтению и записи регистром, который содержит управляющие биты для конфигурации предварительного делителя (пределителя), внешних прерываний, таймера, а также резисторов «pull-up» на выводах PORTB. Назначение бит регистра приведено в табл. 5.4.

Табл. 5.4. Назначение бит регистра OPTION (адрес 81h).

В том случае, когда пределитель обслуживает сторожевой таймер WDT, таймеру TMR0 назначается коэффициент предварительного деления 1:1.

Регистр условий прерывания (INTCON) является доступным по чтению и записи регистром, который содержит биты доступа для всех источников прерываний. Назначение бит регистра приведено в табл. 5.5.

Табл. 5.5. Назначение бит регистра INTCON (адреса 0Bh, 8Bh).

Бит разрешения всех прерываний GIE сбрасывается автоматически при следующих обстоятельствах:

• по включению питания;

• по внешнему сигналу /MCLR при нормальной работе;

• по внешнему сигналу /MCLR в режиме SLEEP;

• по окончанию задержки таймера WDT при нормальной работе;

• по окончанию задержки таймера WDT в режиме SLEEP.

Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет: будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP.

Сброс битов - запросов прерываний - должен осуществляться соответствующей программой обработки.

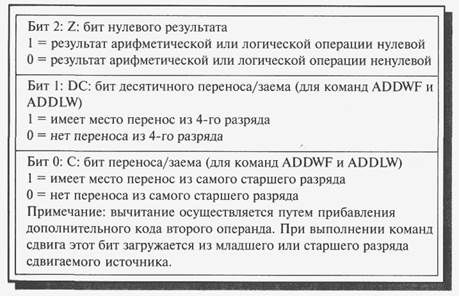

Счетчик команд

Счетчик команд PCL и PCLATH имеет разрядность 13 бит. Младший байт счетчика (PCL) доступен для чтения и записи и находится в регистре 02h. Старший байт счетчика команд не может быть напрямую записан или считан и берется из регистра PCLATH (PC latch high), адрес которого OAh. Содержимое PCLATH передается в старший байт счетчика команд, когда он загружается новым значением.

В зависимости от того, загружается ли в счетчик команд новое значение во время выполнения команд CALL, GOTO, или в младший байт счетчика команд (PCL) производится запись, - старшие биты счетчика команд загружаются из PCLATH разными способами, как показано на рис. 5.6.

Рис. 5.6. Загрузка старших бит счетчика команд.

Команды CALL и GOTO оперируют 11-разрядным адресным диапазоном, достаточным для смещения в пределах страницы программной памяти объемом 2К слов. Для МК подгруппы PIC16F8X этого хватает. С целью обеспечения возможности расширения памяти команд для будущих моделей МК предусмотрена загрузка двух старших бит счетчика команд из регистра PCLATH<4:3>. При использовании команд CALL и GOTO пользователь должен убедиться в том, что эти страничные биты запрограммированы для выхода на нужную страницу. При выполнении команды CALL или выполнении прерывания весь 13-битный счетчик команд помещается в стек, поэтому для возвращения из подпрограммы не нужны манипуляции с разрядами PCLATH<4:3>.

Микроконтроллеры подгруппы PIC16F8X игнорируют значения бит PCLATH<4:3>, которые используются для обращения к страницам 1, 2 и 3 программной памяти. Однако применять биты РС1_АТН<4:3> в качестве ячеек памяти общего назначения не рекомендуется, так как это может повлиять на совместимость с будущими поколениями изделий.

Возможность выполнять арифметические операции непосредственно над счетчиком команд позволяет очень быстро и эффективно осуществлять табличные преобразования в Р1С-контроллерах.

Микроконтроллеры подгруппы PIC16F8X имеют восьмиуровневый аппаратный стек шириной 13 бит (см. рис. 5.4). Область стека не принадлежит ни к программной области, ни к области данных, а указатель стека пользователю недоступен. Текущее значение счетчика команд посылается в стек, когда выполняется команда CALL или производится обработка прерывания. При выполнении процедуры возврата из подпрограммы (команды RETLW, RETFIE или RETURN) содержимое счетчика команд восстанавливается из стека. Регистр PCLATH при операциях со стеком не изменяется.

Стек работает как циклический буфер. Следовательно, после того как стек был загружен 8 раз, девятая загрузка перепишет значение первой. Десятая загрузка перепишет вторую и т.д. Если стек был выгружен 9 раз, счетчик команд становится таким же, как после первой выгрузки.

Признаков положения стека в контроллере не предусмотрено, поэтому пользователь должен самостоятельно следить за уровнем вложения подпрограмм.

5.2.8. Прямая и косвенная адресации

Когда производится прямая 9-битная адресация, младшие 7 бит берутся как прямой адрес из кода операции, а два бита указателя страниц (RP1, RPO) из регистра статуса, как показано на рис. 5.7.

Рис. 5.7. Методы адресации данных.

Признаком косвенной адресации является обращение к регистру INDF. Любая команда, которая использует INDF (адрес ООН) в качестве регистра фактически обращается к указателю, который хранится в FSR (адрес 04h). Чтение косвенным образом самого регистра INDF даст результат ООН. Запись в регистр INDF косвенным образом будет выглядеть как NOP, но биты статуса могут быть изменены. Необходимый 9-битный адрес формируется объединением содержимого 8-битного FSR регистра и бита IRP из регистра статуса (см. рис. 5.7).

Обратите внимание, что некоторые регистры специальных функций располагаются в банке 1. Чтобы адресоваться к ним, нужно дополнительно установить в единицу бит RPO в регистре статуса.

5.2.9. Порты ввода/вывода

Контроллеры подгруппы PIC16F8X имеют два порта: PORTA (5 бит) и PORTB (8 бит) с побитовой индивидуальной настройкой на ввод или на вывод.

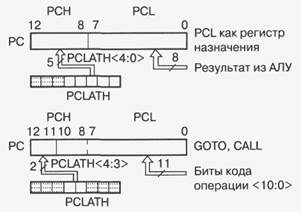

Порт A (PORTA) представляет собой 5-битовый фиксатор, соответствующий выводам контроллера RA<4:0>. Линия RA4 имеет вход триггера Шмит-та и выход с открытым стоком. Все остальные линии порта имеют ТТЛ входные уровни и КМОП выходные буферы. Адрес регистра порта А - 05Н.

Каждой линии порта поставлен в соответствие бит направления передачи данных, который хранится в управляющем регистре TRISA, расположенном по адресу 85Н. Если бит управляющего TRISA регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра-фиксатора порта. При включении питания все линии порта по умолчанию настроены на ввод.

На рис. 5.8 дана схема линий RA<3:0> порта А.

Рис. 5.8. Схема линий RA<3:0> порта А. Выводы порта имеют защитные диоды к Vdd и Vss.

Операция чтения порта А считывает состояние выводов порта, в то время как запись в него изменяет состояние триггеров порта. Все операции с портом являются операциями типа «чтение-модификация-запись». Поэтому запись в порт предполагает, что состояние выводов порта вначале считывается, затем модифицируется и записывается в триггер-фиксатор.

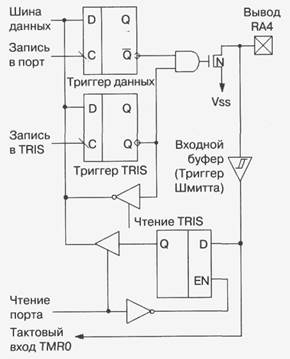

Вывод RA4 мультиплексирован с тактовым входом таймера TMRO. Схема линии RA4 порта А приведена на рис. 5.9.

Порт В (PORTB) - это двунаправленный 8-битовый порт, соответствующий выводам RB<7:0> контроллера и расположенный по адресу 06Н. От-

носящийся к порту В управляющий регистр TRISB расположен на первой странице регистров по адресу 86h. Если бит управляющего TRISB регистра имеет значение 1, то соответствующая линия будет устанавливаться на ввод. Ноль переключает линию на вывод и одновременно выводит на нее содержимое соответствующего регистра защелки. При включении питания все линии порта по умолчанию настроены на ввод.

Рис. 5.9. Схема линии RA4 порта А. Вывод порта имеет защитный диод только к Vss.

У каждой ножки порта В имеется небольшая активная нагрузка (около ЮОмкА) на линию питания (pull-up). Она автоматически отключается, если эта ножка запрограммирована как вывод. Более того, управляющий бит / RBPU регистра OPTION<7> может отключить (при RBPU=1) все нагрузки. Сброс при включении питания также отключает все нагрузки.

Четыре линии порта В (RB<7:4>) могут вызвать прерывание при изменении значения сигнала на любой из них. Если эти линии настроены на ввод, то они опрашиваются и защелкиваются в цикле чтения Q1. Новая величина входного сигнала сравнивается со старой в каждом командном

цикле. При несовпадении значения сигнала на ножке и в фиксаторе генерируется высокий уровень. Выходы детекторов «несовпадений» RB4, RB5, RB6, RB7 объединяются по ИЛИ и генерируют прерывание RBIF (запоминаемое в регистре INTCON<0>). Любая линия, настроенная как вывод, в этом сравнении не участвует. Прерывание может вывести кристалл из режима SLEEP. В подпрограмме обработки прерывания следует сбросить запрос прерывания одним из следующих способов:

• прочитать (или записать в) порт В. Это завершит состояние сравнения;

• обнулить бит RBIF регистра INTCON<0>.

При этом необходимо иметь в виду, что условие «несовпадения» будет продолжать устанавливать признак RBIF. Только чтение порта В может устранить «несовпадение» и позволит обнулить бит RBIF.

Прерывание по несовпадению и программно устанавливаемые внутренние активные нагрузки на этих четырех линиях могут обеспечить простой интерфейс, например, с клавиатурой, с выходом из режима SLEEP по нажатию клавиш.

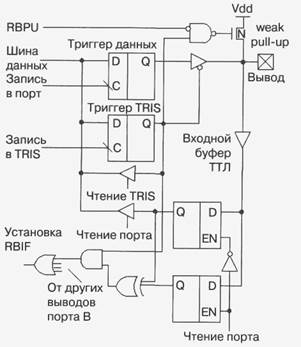

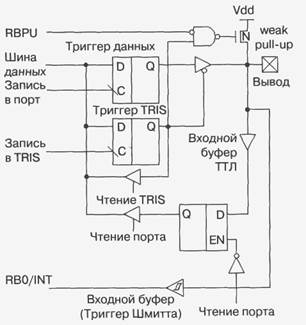

Схемы линий порта В приведены на рис. 5.10 и 5.11.

Рис. 5.10. Схема линий RB<7:4> порта В. Выводы порта имеют защитные диоды к Vdd и Vss.

Рис. 5.11. Схема линий RB<3:0> порта В. Выводы порта имеют защитные диоды к Vdd и Vss.

При организации двунаправленных портов необходимо учитывать особенности организации ввода/вывода данных МК. Любая команда, которая осуществляет запись, выполняет ее внутри как «чтение-модификация-запись». Например, команды BCF и BSF считывают порт целиком, модифицируют один бит и выводят результат обратно. Здесь необходима осторожность. В частности, команда BSF PORTB, 5 (установить в единицу бит 5 порта В) сначала считывает все реальные значения сигналов, присутствующие в данный момент на выводах порта. Затем выполняются действия над битом 5, и новое значение байта целиком записывается в выходные фиксаторы. Если другой бит регистра PORTB используется в качестве двунаправленного ввода/вывода (скажем, бит 0), и в данный момент он определен как входной, то входной сигнал на этом выводе будет считан и записан обратно в выходной триггер-фиксатор этого же вывода, стирая предыдущее состояние. До тех пор, пока эта ножка остается в режиме ввода, никаких проблем не возникает. Однако если позднее линия О переключится в режим вывода, ее состояние будет неопределенным.

На ножку, работающую в режиме вывода, не должны нагружаться внешние источники токов («монтажное И», «монтажное ИЛИ»). Большие результирующие токи могут повредить кристалл.

Необходимо выдерживать определенную последовательность обращения к портам ввода/вывода. Запись в порт вывода происходит в конце командного цикла. Но при чтении данные должны быть стабильны в начале командного цикла. Будьте внимательны в операциях чтения, следующих сразу за записью в тот же порт. Здесь надо учитывать инерционность установления напряжения на выводах. Может потребоваться программная задержка, чтобы напряжение на ножке (которое зависит от нагрузки) успело стабилизироваться до начала исполнения следующей команды чтения.

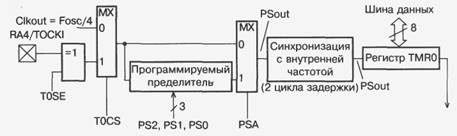

5.2.10. Модуль таймера и регистр таймера

Структура модуля таймера/счетчика TIMERO и его взаимосвязь с регистрами TMRO и OPTION показаны на рис. 5.12. TIMERO является программируемым модулем и содержит следующие компоненты:

• 8-разрядный таймер/счетчик TMRO с возможностью чтения и записи как регистр;

• 8-разрядный программно управляемый предварительный делитель (пределитель);

• мультиплексор входного сигнала для выбора внутреннего или внешнего тактового сигнала;

• схему выбора фронта внешнего тактового сигнала;

• формирователь запроса прерывания по переполнению регистра TMRO с FFh до OOh.

Режим таймера выбирается путем сбрасывания в ноль бита TOCS регистра OPTION <5>. В режиме таймера TMRO инкрементируется каждый командный цикл (без пределителя). После записи информации в TMRO инкрементирование его начнется после двух командных циклов. Это происходит со всеми командами, которые производят запись или чтение-модификацию-запись TMRO (например, MOVF TMRO, CLRF TMRO). Избежать этого можно при помощи записи в TMRO скорректированного ишчения. Если TMRO нужно проверить на равенство нулю без останова счета, следует использовать инструкцию MOVF TMRO,W.

Режим счетчика выбирается путем установки в единицу бита TOCS ре-Iнегра OPTION<5>. В этом режиме регистр TMRO будет инкрементиро-шпъся либо нарастающим, либо спадающим фронтом на выводе RA4/ IOCKI от внешних событий. Направление фронта определяется управляющим битом TOSE в регистре OPTION<4>. При TOSE = 0 будет выбран нарастающий фронт.

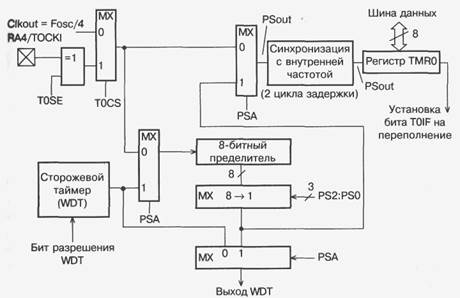

Пределитель может использоваться или совместно с TMRO, или со сторожевым (Watchdog) таймером. Вариант подключения делителя контро-•шрустся битом PSAрегистра OPTION<3>. При PSA=0 делитель будет под-

соединен к TMRO. Содержимое делителя программе недоступно. Коэффициент деления пределителя программируется битами PS2...PSO регистра OPTION<2:0>.

Рмс. 5.12. Структурная схема таймера/счетчика TMRO.

Прерывание по TMRO вырабатывается тогда, когда происходит переполнение регистра таймера/счетчика при переходе от FFh к OOh. Тогда устанавливается бит запроса TOIF в регистре INTCON<2>. Данное прерывание можно замаскировать битом TOIE в регистре INTCON<5>. Бит запроса TOIF должен быть сброшен программно при обработке прерывания. Прерывание по TMRO не может вывести процессор из режима SLEEP потому, что таймер в этом режиме не функционирует.

При PSA= 1 делитель будет подсоединен к сторожевому таймеру как постделитель (делитель на выходе). Возможные варианты использования пределителя показаны на рис. 5.13.

При использовании пределителя совместно с TMRO, все команды, изменяющие содержимое TMRO, обнуляют пределитель. Если пределитель используется совместно с WDT, команда CLRWDT обнуляет содержимое пределителя вместе с WDT.

При использовании модуля TIMERO в режиме счетчика внешних событий необходимо учитывать то, что внешний тактовый сигнал синхронизируется внутренней частотой Fosc. Это приводит к появлению задержки во времени фактического инкрементирования содержимого TMRO.

Синхронизация происходит по окончании 2-го и 4-го тактов работы МК, поэтому, если пределитель не используется, то для фиксации входного события необходимо, чтобы длительности высокого и низкого состояний сигнала на входе RA4/TOCKI были бы не менее 2 периодов тактовой частоты Tosc плюс некоторая задержка ( ~ 20 не).

Если модуль TIMERO используется совместно с пределителем, то частота входного сигнала делится асинхронным счетчиком так, что сигнал на выходе пределителя становится симметричным. При этом необходимо,

чтобы длительности высокого и низкого уровней сигнала на входе RA4/ TOCKI были бы не менее 10 не. Синхронизация сигнала происходит на выходе пределителя, поэтому существует небольшая задержка между фронтом внешнего сигнала и временем фактического инкремента таймера/счетчика. Эта задержка находится в диапазоне от 3 до 7 периодов колебаний тактового генератора. Таким образом, измерение интервала между событиями будет выполнено с точностью +4 • Tosc.

Рис. 5.13. Структура и возможные варианты использования пределителя.

5.2.11. Память данных в РПЗУ (EEPROM)

Микроконтроллеры подгруппы PIC6F8X имеют энергонезависимую память данных 64x8 EEPROM бит, которая допускает запись и чтение во время нормальной работы (во всем диапазоне питающих напряжений). Эта память не принадлежит области регистровой памяти ОЗУ. Доступ к ней осуществляется посредством косвенной адресации через регистры специальных функций: EEDATA<08h>, который содержит 8-битовые данные для чтения/записи и EEADR <09h>, включающий адрес ячейки, к которой идет обращение. Для управления процессом чтения/записи исполь-•уются два регистра: EECON1 <88h> и EECON2 <89h>.

При записи байта автоматически стирается предыдущее значение, и шписываются новые данные (стирание перед записью). Все эти операции

производит встроенный автомат записи EEPROM. Содержимое ячеек этой памяти при выключении питания сохраняется.

Регистр EEADR может адресовать до 256 байт данных EEPROM. В МК подгруппы PIC6F8X используются только первые 64 байта, адресуемые шестью младшими битами EEADR<5:0>. Однако старшие два бита также декодируются. Поэтому эти два бита должны быть установлены в '0', чтобы адрес попал в доступные 64 бита адресного пространства.

Назначение бит регистра EECON1 приведено в табл. 5.6.

Табл. 5.6. Назначение бит регистра EECON1 (адреса 88h).

Регистр EECON2 не является физическим регистром. Он используется исключительно при организации записи данных в EEPROM. Чтение регистра EECON2 дает нули.

При считывании данных из памяти EEPROM необходимо записать нужный адрес в EEADR регистр и затем установить бит RD EECONKO в единицу. Данные появятся в следующем командном цикле в регистре EEDATA и могут быть прочитаны. Данные в регистре EEDATA фиксируются.

При записи в память EEPROM необходимо сначала записать адрес в EEADR-регистр и данные в EEDATA-регистр. Затем следует выполнить специальную последовательность команд, производящую непосредственную запись:

movlw 55h

movwf EECON2

movlw AAh

movwf EECON2

bsf EECON1 ,WRустановить WR бит, начать запись

Во время выполнения этого участка программы все прерывания должны быть запрещены, для точного выполнения временной диаграммы. Время записи - примерно 10 мс. Фактическое время записи может изменяться в зависимости от напряжения, температуры и индивидуальных свойств кристалла. В конце записи бит WR автоматически обнуляется, а флаг завершения записи EEIF, он же запрос на прерывание, устанавливается.

Для предотвращения случайных записей в память данных предусмотрен специальный бит WREN в регистре EECON1. Рекомендуется держать бит WREN выключенным, кроме тех случаев, когда нужно обновить память данных. Более того, кодовые сегменты, которые устанавливают бит WREN, и те, которые выполняют запись, следует хранить на различных адресах, чтобы избежать случайного выполнения их обоих при сбое программы.

5.2.12. Организация прерываний

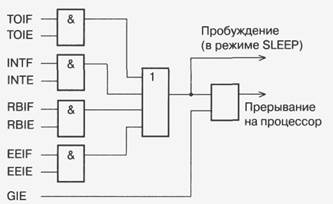

МК подгруппы PIC16F8X имеют четыре источника прерываний:

• внешнее прерывание с вывода RBO/INT;

• прерывание от переполнения счетчика/таймера TMRO;

• прерывание от изменения сигналов на линиях порта RB<7:4>;

• прерывание по окончании записи данных в EEPROM.

Все прерывания имеют один и тот же вектор/адрес — 0004Н. Однако в управляющем регистре прерываний INTCON соответствующим битом-признаком записывается, от какого именно источника поступил запрос прерывания. Исключение составляет прерывание по завершении записи н EEPROM, признак которого находится в регистре EECON1.

Бит общего разрешения/запрещения прерывания GIE (INTCON <7>) разрешает (если = 1) все индивидуально незамаскированные прерывания или запрещает их (если = 0). Каждое прерывание в отдельности может быть дополнительно разрешено/запрещено установкой/сбросом соответствующего бита в регистре INTCON.

Бит GIE при сбросе обнуляется. Когда начинает обрабатываться прерывание, бит GIE обнуляется, чтобы запретить дальнейшие прерывания, адрес возврата посылается в стек, а в программный счетчик загружается адрес 0004Н. Время реакции на прерывание для внешних событий, таких как прерывание от ножки INT или порта В, составляет приблизительно пять циклов. Это на один цикл меньше, чем для внутренних событий, таких как прерывание по переполнению от таймера TMRO. Время реакции всегда одинаковое.

В подпрограмме обработки прерывания источник прерывания может быть определен по соответствующему биту в регистре признаков. Этот флаг-признак должен быть программно сброшен внутри подпрограммы. Признаки запросов прерываний не зависят от соответствующих маскирующих битов и бита общего маскирования GIE.

Команда возврата из прерывания RETFIE завершает прерывающую подпрограмму и устанавливает бит GIE, чтобы опять разрешить прерывания.

Логика прерываний контроллера изображена на рис. 5.14.

Рис.5.14. Логика прерываний микроконтроллера.

Внешнее прерывание на ножке RBO/INT осуществляется по фронту: либо по нарастающему (если в регистре OPTION бит INTEDG=1), либо по спадающему (если INTEDG=0). Когда фронт обнаруживается на ножке INT, бит запроса INTF устанавливается в единицу (INTCON < 1 >). Это

прерывание может быть замаскировано сбросом управляющего бита INTE в ноль (INTCON <4>). Бит запроса INTF необходимо очистить прерывающей программой перед тем, как опять разрешить это прерывание. Прерывание INT может вывести процессор из режима SLEEP, если перед входом в этот режим бит INTE был установлен в единицу. Состояние бита GIE также определяет, будет ли процессор переходить на подпрограмму прерывания после выхода из режима SLEEP.

Переполнение счетчика TMRO (FFh->OOh) устанавливает в единицу бит запроса TOIF (INTCON<2>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски TOIE (INTCON<5>). Сброс запроса TOIF — дело программы обработки.

Любое изменение сигнала на одном из четырех входов порта RB<7:4> устанавливает в единицу бит RBIF (INTCON<0>). Это прерывание может быть разрешено/запрещено установкой/сбросом бита маски RBIE (INTCON<3>). Сброс запроса RBIF - дело программы обработки.

Признак запроса прерывания по завершении записи в EEPROM, EEIF (EECON1<4>) устанавливается в единицу по окончании автоматической чаписи данных в EEPROM. Это прерывание может быть замаскировано сбросом бита EEIE (INTCON<6>). Сброс запроса EEIF — дело программы обработки.

Дата добавления: 2016-01-07; просмотров: 4336;