Процессор ввода-вывода

Для организации обмена данными в вычислительных системах обычно используются различные контроллеры, позволяющие согласовывать работу того или иного ВУ с работой системы. Примерами могут служить контроллеры ПКП и ПДП. В функции контроллеров входит анализ сигналов от ВУ, дешифрация адреса ВУ, адресация памяти (для ПДП), синхронизация обмена, согласование форматов данных, выдача управляющих сигналов и т. д. Чем шире многообразие ВУ, тем большее число различных контроллеров необходимо для их обслуживания. Специфика ВС состоит, в частности, в использовании большого числа специализированных ВУ, что заставляет каждый раз проектировать соответствующий контроллер. Кроме того, помимо функций управления ВУ и передачей данных на эти контроллеры возлагают дополнительные функции по предварительной обработке передаваемых данных (например, кодирование, декодирование, анализ условий окончания передачи).

Для снижения трудоемкости проектирования и повышения эффективности системы ввода-вывода в ВС, создаваемых на основе ЦП Intel 8086, удобно использовать специализированный процессор ввода-вывода Intel 8089. Этот процессор сочетает в себе свойства универсальноro контроллера ПДП со свойствами специализированного процессора, который позволяет осуществлять различные преобразования данных во время пересылок.

Рис. 8.1. Архитектура процессора ввода-вывода Intel 8089

Процессор ввода-вывода (ПВВ) имеет два канала ввода-вывода, каждый из которых может осуществлять высокоскоростные пересылки в режиме ПДП с одновременным преобразованием пересылаемых данных. ПВВ удобно рассматривать как два независимых канала, каждый из которых может находиться в одном из трех основных режимов работы: простаивать (пассивное состояние), выполнять программу канала и осуществлять пересылку в режиме ПДП.

По способу «общения» ЦП с ПВВ различают два режима взаимодействия: начальная инициализация и управление.

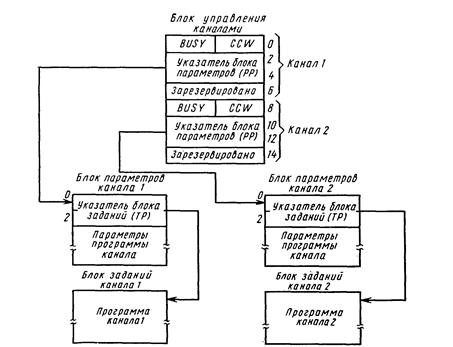

Общее устройство управления УУ обеспечивает начальную инициализацию ПВВ. По включении питания или сигналу начальной установки RESET центральный процессор подготавливает в памяти ряд связанных друг с другом блоков (рис. 8.2) с сообщениями для ПВВ. После этого ЦП выдает сигналы СА (готовность канала) и SEL (выбор канала), запрашивающие готовность каналов. По сигналу СА сопроцессор прекращает какие-либо действия и анализирует сигнал SEL, указывающий номер канала (1 или 2), которому предназначается сообщение. Когда канал выбран, ПВВ исследует слово управления каналом CCW, которое задает режим работы канала (простаивание, программа канала, пересылка с ПДП). Если управляющее слово требует запуск выполнения программы, то ПВВ загружает адреса блока параметров и блока заданий во внутренние регистры соответствующего канала, устанавливает флаг занятости BUSY и переходит к выполнению программы канала.

Рис. 8.2. Структура блоков сообщений при начальной инициализации ПВВ

Центральный процессор после выдачи сигнала СА освобождается для выполнения другой работы. После окончания выполнения программы канал сбрасывает флаг занятости BUSY в блоке управления. Таким образом, взаимодействие ЦП и ПВВ строится по схеме, показанной на рис. 8.3. При необходимости ПВВ может выдать запрос прерывания в ЦП.

По способу организации ВС, включающей ЦП и ПВВ, различают два вида конфигурации системы: местную и удаленную. Местная конфигурация характеризуется тем, что ЦП и ПВВ совместно используют системные шины, в то время как при удаленной конфигурации шина ввода-вывода «удалена» от ЦП и ПВВ может обращаться к ВУ, не используя общую системную шину. Таким образом, удаленная конфигурация повышает степень параллельности работы ЦП и ПВВ и увеличивает производительность ВС.

ПВВ может обращаться к элементам памяти, расположенным в двух различных пространствах адресов. Системное пространство, совпадающее с пространством памяти ЦП, может содержать до 220 = 1048676 байт. Пространство ввода-вывода, которое также может совпадать с пространством ввода-вывода ЦП или быть принадлежностью только ПВВ, содержит до 216 = 65 536 байт. Когда пространства ввода-вывода ЦП и ПВВ не совпадают, говорят, что ВС имеет удаленную конфигурацию.

Поскольку ВУ можно кодировать как адреса памяти, то в обоих пространствах могут размещаться как устройства памяти, так и ВУ. Причем ВУ, расположенные в системном пространстве, являются отображенными на память, а память, расположенная в пространстве ввода-вывода, оказывается отображенной на ввод-вывод. С точки зрения программирования оба пространства памяти ПВВ организованы как несегментированные массивы, состоящие из индивидуально адресуемых байтов. Команды и данные могут размещаться в любых адресах без выравнивания, т. е. без предпочтительного размещения младшего байта по четному адресу. ПВВ «рассматривает» системное пространство иначе, чем ЦП, с которым он совместно использует это пространство. Центральный процессор, как было ранее показано, делает различие между логическим адресом памяти, состоящим из 16-разрядного начального адреса сегмента и 16-разрядного смещения в сегменте, и ее физическим 20-разрядным адресом. ПВВ игнорирует логическую сегментированную структуру пространства памяти и пользуется только 20-разрядным физическим адресом. Память, расположенная в пространстве ввода-вывода ПВВ, рассматривается аналогично, за исключением того, что для обращения к любой ячейке требуется только 16 разрядов адреса.

Схема сопроцессора (рис. 8.1) подразделена на ряд функциональных узлов, которые соединяются между собой 20-разрядной шиной, обеспечивающей максимальную скорость внутренних пересылок.

Общее устройство управления.Устройство управления (УУ) координирует работу сопроцессора, определяя приоритеты каналов, синхронизируя циклы выполнения команд, пересылки с ПДП, ответы на запросы готовности канала. В частности, под управлением общего УУ выполняется начальная инициализация сопроцессор а.

Арифметико-логическое устройство(АЛУ). Может выполнять арифметические операции над 8- и 16-разрядными двоичными числами, причем длина результата может доходить до 20 разрядов. Имеются арифметические команды сложения, увеличения и уменьшения на единицу, а также логические операции И, ИЛИ и НЕ.

Регистры сборки-разборки.Служат для выполнения пересылки данных за минимально возможное число циклов работы с шиной, когда данные пересылаются между шинами разной разрядности. Например, при пересылке с ПДП данных от 8-разрядного ВУ в 16-разрядную память сопроцессор выполняет два цикла работы с шиной, принимая 8 разрядов за каждый цикл, собирает 16-разрядное слово, а затем пересылает это слово в память за один цикл.

Регистр выборки команд.Служит для хранения команд, выбираемых из памяти для работающего канала. Команды поступают по 16-разрядной шине данных через буфер шины (БШ) и запоминаются в этом регистре в виде очереди из байтов команд. Каждый канал имеет свою собственную очередь, и работа одного канала не влияет на очередь другого канала. Преимущества использования внутренней очереди из байтов команд были показаны для ЦП.

Устройство сопряжения с шиной(УСШ). Управляет всеми циклами работы с ША/Д, пересылая команды и данные между сопроцессором и памятью или ВУ. Устройство сопряжения с шиной выдает сигналы управления S2, Sl и S0, которые затем декодируются системным контроллером Intel 8288. При работе с сопроцессором контроллер вырабатывает управляющие сигналы, аналогичные тем, которые формируются при работе с ЦП. Кроме пересылок УСШ осуществляет управление совместным использованием шин СП и ЦП путем формирования и анализа сигнала RQ/GT - запроса и предоставления шины. В функции УСШ входит также формирование сигналов LOCK - захват шины и ВНЕ - разрешение старшего байта.

Рассмотрим особенности организации каналов сопроцессора.

Устройство управления вводом - выводом(УУВВ) . Имеется в каждом канале, выполняет следующие функции:

· если пересылка синхронная, то УУВВ ожидает поступления сигнала по

входу DRQ (запрос ПДП) перед выполнением очередного цикла чтения - записи;

· если пересылка должна заканчиваться при получении внешнего

сигнала, то УУВВ наблюдает за поступлением сигнала по входу ЕХТ (внешнее окончание);

· между циклами чтения и записи, когда данные находятся в ПВВ, канал

может подсчитать, перекодировать и проанализировать данные, причем УУВВ может прекратить пересылку на основании результатов этих операций;

· УУВВ имеет выход SINTR (системное прерывание), который может

быть активизирован программно для передачи запроса прерывания в ЦП.

Дата добавления: 2015-12-22; просмотров: 3088;