Преобразователи кодов

Кодирующие устройства

Преобразователи кодов

В цифровых устройствах часто возникает необходимость преобразования информации из одной двоичной системы в другую (из одного двоичного кода в другой). Для представления двоичных систем используются различные виды кодирования: прямой, обратный, дополнительный, двоично-десятичный и т. д. Особая роль отводится корректирующим кодам и кодам, обнаруживающим и исправляющим ошибки. Они удобны для передачи сигналов по линиям связи в условиях воздействия помех.

На аппаратном уровне задачу преобразования информации из одного кода в другой выполняют комбинационные устройства — преобразователи кодов.

Преобразователь кода — комбинационное устройство, предназначенное для изменения вида кодирования информации (английское — converter).

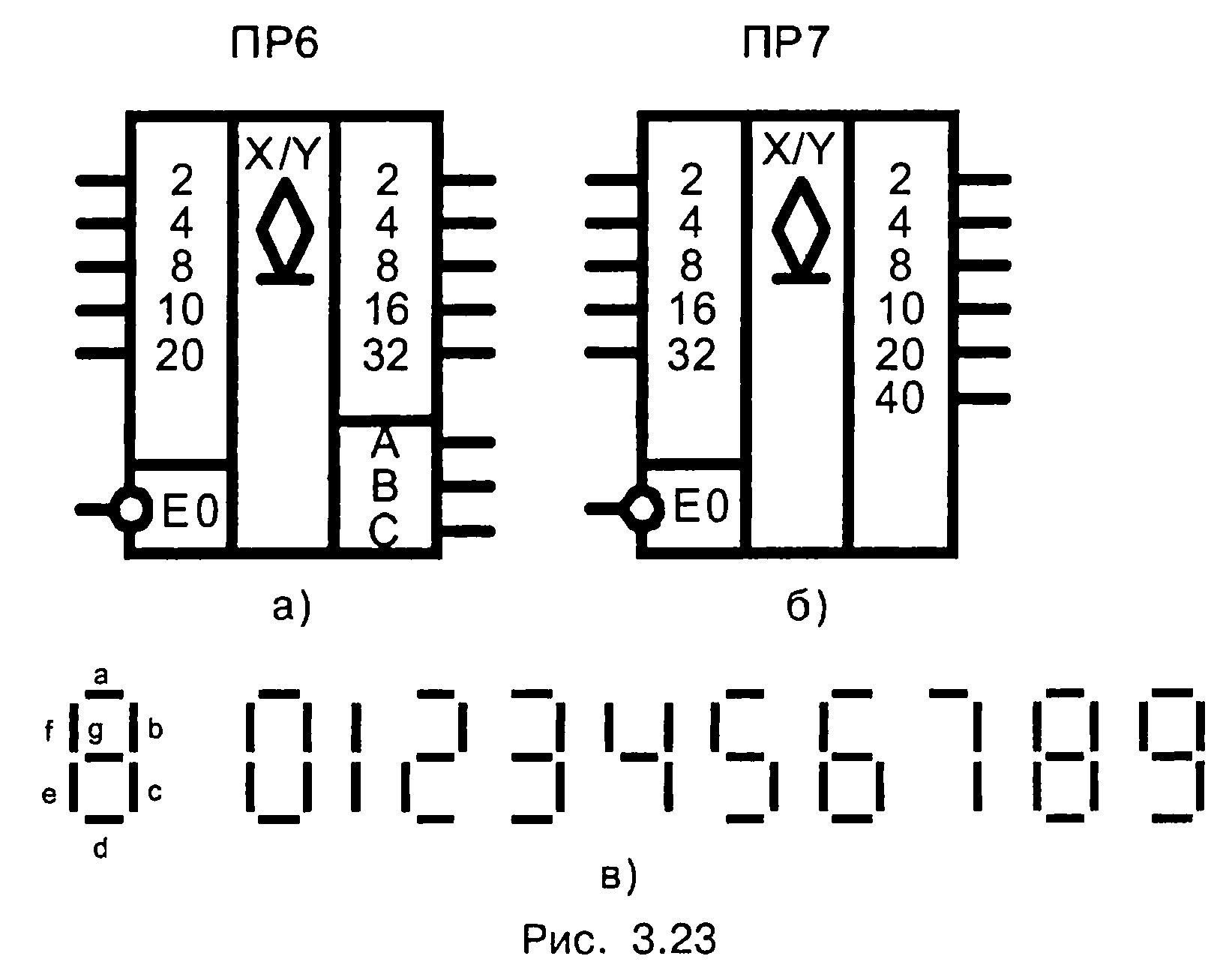

На принципиальных схемах преобразователи кодов обозначаются X/Y. В отечественных сериях преобразователи код-код можно определить по буквам ПР. Буква П соответствует подгруппе преобразователей сигналов. Например, 155ПР6 — преобразователь двоично-десятичного кода в двоичный; 155ПР7 — преобразователь двоичного кода в двоично-десятичный (рис. 3.23, а, б). Вход ЕО является входом разрешения выхода.

При проектировании и конструировании преобразователей кодов можно выделить два подхода:

1) метод, основанный на преобразовании исходного двоичного кода в десятичный и последующем преобразовании десятичного представления в требуемый код;

2) метод, основанный на использовании логического устройства комбинационного типа, непосредственно реализующего данное преобразование.

В первом методе каскадно соединяют дешифратор и шифратор. Сами шифраторы и дешифраторы являются частным случаем преобразователей кодов.

Во втором случае, как для любого комбинационного устройства, составляют таблицу истинности и устанавливают однозначное соответствие между подаваемыми на входы и снимаемыми на выходах комбинациями. Далее проводят синтез логического комбинационного устройства в заданном базисе.

Отметим также, что любые преобразования параллельных кодов легко и удобно осуществить на микросхемах постоянной памяти и программируемых логических матрицах.

Рассмотрим пример управления семисегментным светодиодным либо жидкокристаллическим индикатором (рис. 3.23, в). Такие индикаторы при различных комбинациях светящихся элементов высвечивают цифры от 0 до 9. Для цифры 0 необходимо погасить сегмент g, а остальные должны светится. Для цифры 1 — светятся сегменты b и с; сегменты a, d, е, f, g погашены и т. д.. Сегмент будет гореть, если на него будет подано напряжение логического нуля. Сегмент будет погашен, если на него будет подано напряжение логической единицы.

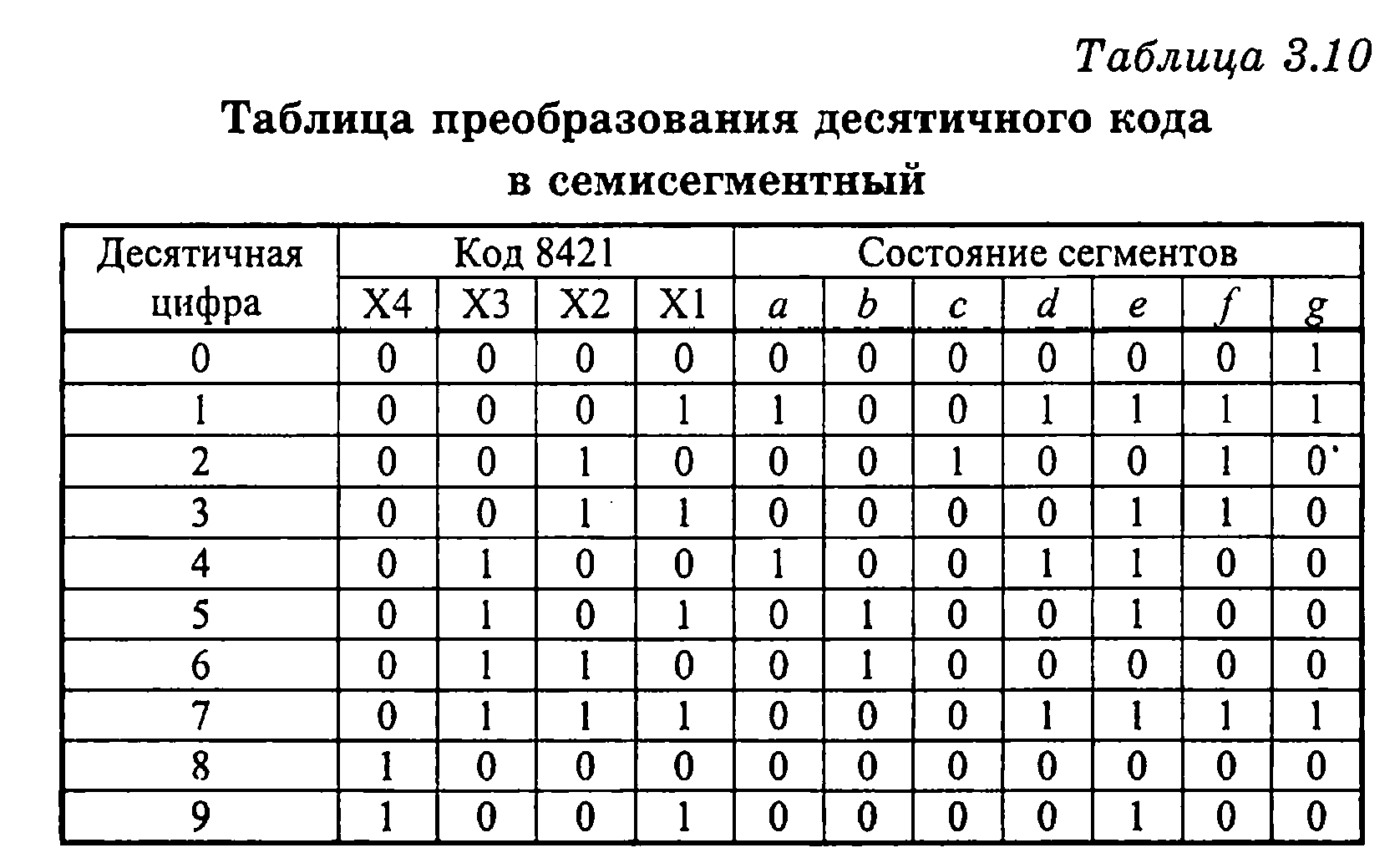

Запишем таблицу истинности для данного преобразования кодов.

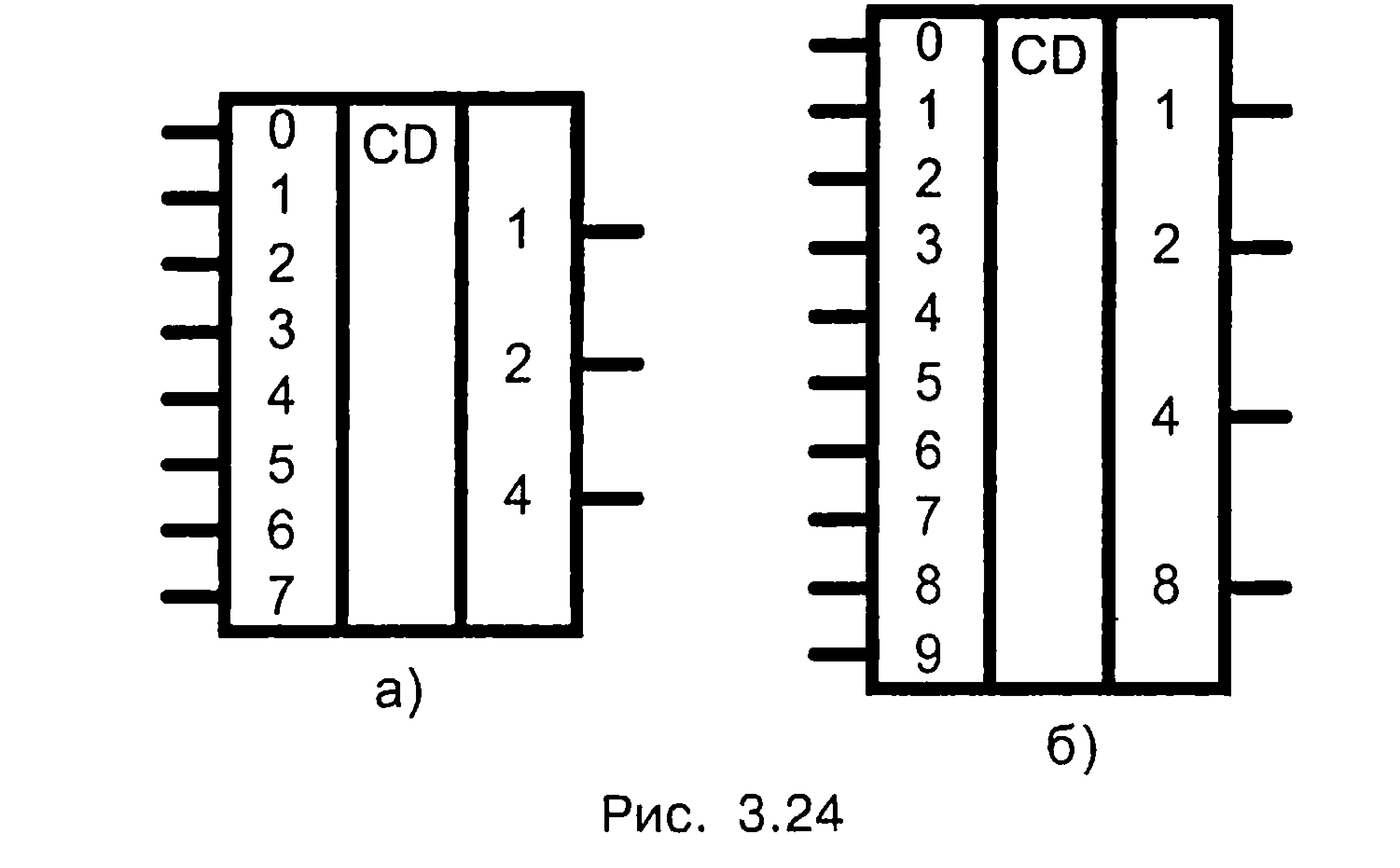

Синтезируемое комбинационное устройство имеет четыре входа и семь выходов, поэтому для каждого из семи выходов получаем формулу в базисе И-НЕ:

Полученные формулы (3.12) позволяют без большого труда построить схему преобразователя кода двоичного в семисегментный.

Шифраторы

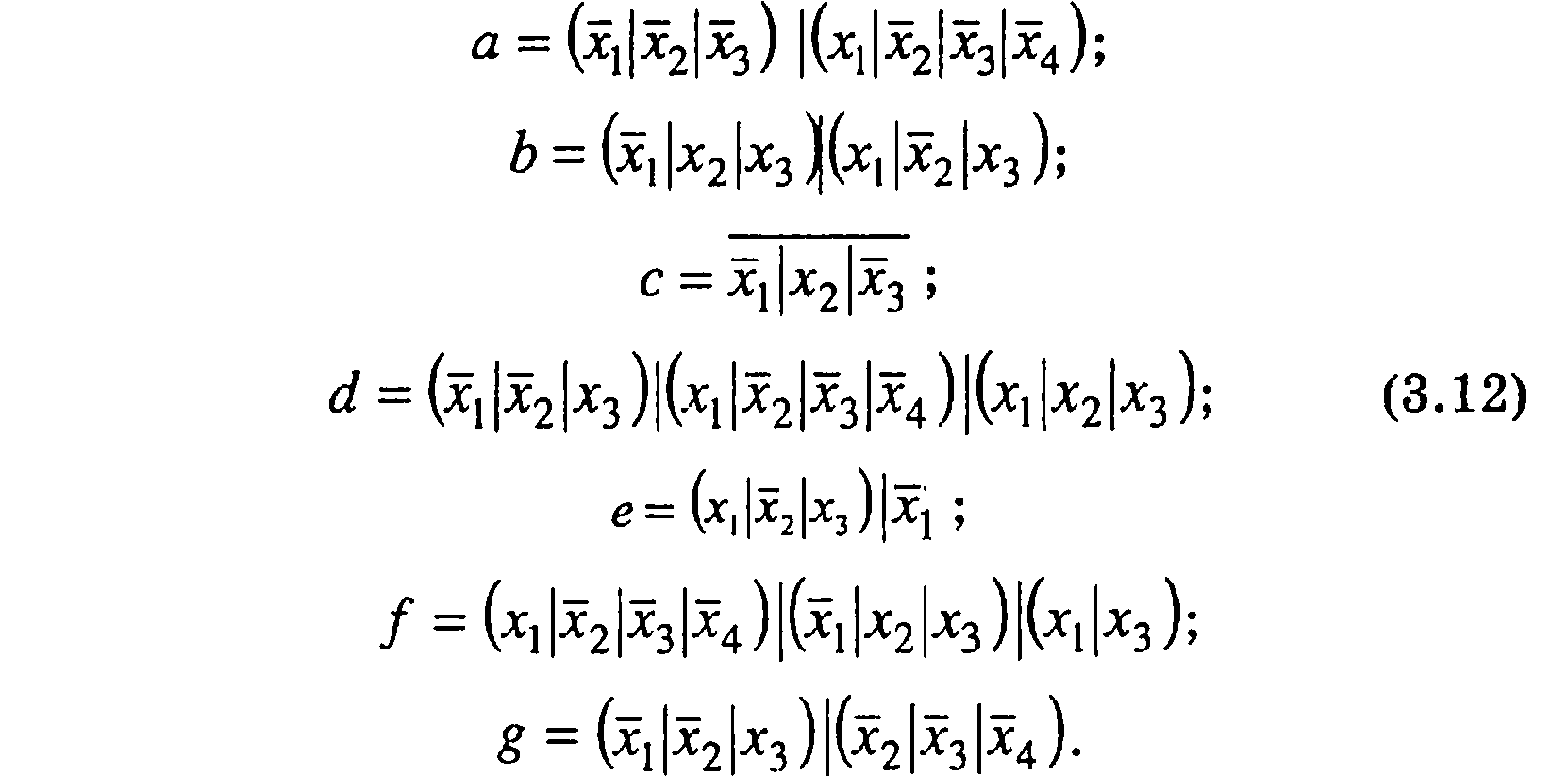

Шифратор преобразует сигнал, поданный только в один входной провод, в выходной параллельный двоичный код на выходах шифратора. Шифратор также называют кодером (CD). Таким образом, подача сигнала на один из входов приводит к появлению на выходах двоичного числа, соответствующего номеру возбужденного входа.

Полный шифратор имеет 2п входов и п выходов (рис. 3.24, а).

В отечественных схемах шифраторы обозначаются буквами ИВ, например К555ИВ1.

Шифраторы также применяются для преобразования десятичных чисел в двоичную систему счисления (рис. 3.24,б), тогда число входов меньше 2п, где п — число выходов. Например, шифратор на рис. 3.24, б при возбуждении одного из 10 входов (х0,х1..., х9) формирует на выходах двоичный код номера возбужденной входной линии. Так, при подаче сигнала на вход х9 на выходах появится код 1001.

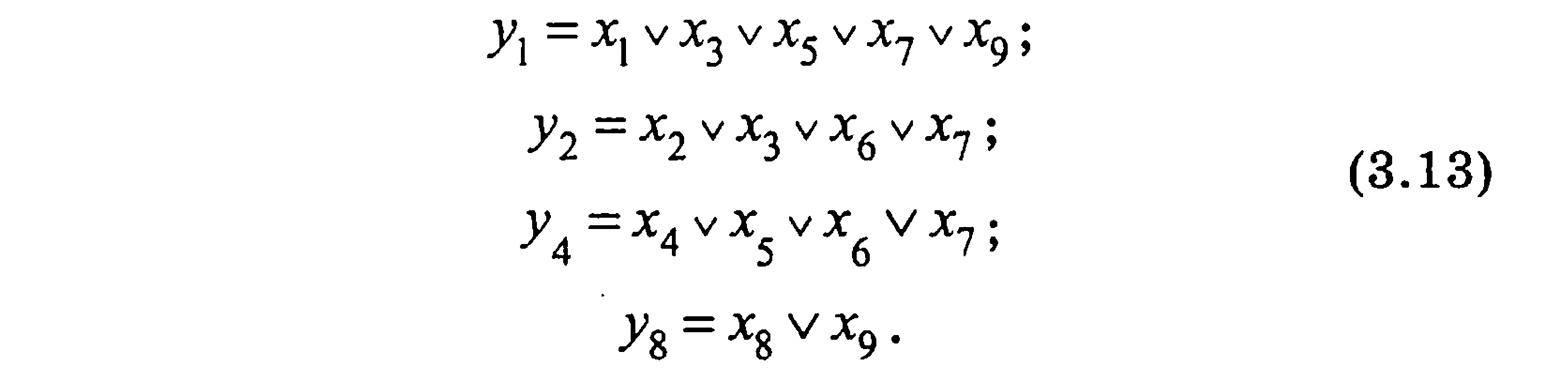

Применение шифраторов приводит к сокращению количества сигналов в цифровых устройствах (линий передачи). Также шифраторы используют в разнообразных устройствах ввода информации в цифровые системы. Рассмотрим таблицу истинности шифратора (рис. 3.24, б), преобразующего десятичные числа 0, 1, 2, ..., 9 в двоичное представление в коде 8421.

Входные и выходные сигналы могут быть как прямыми, так и инверсными.

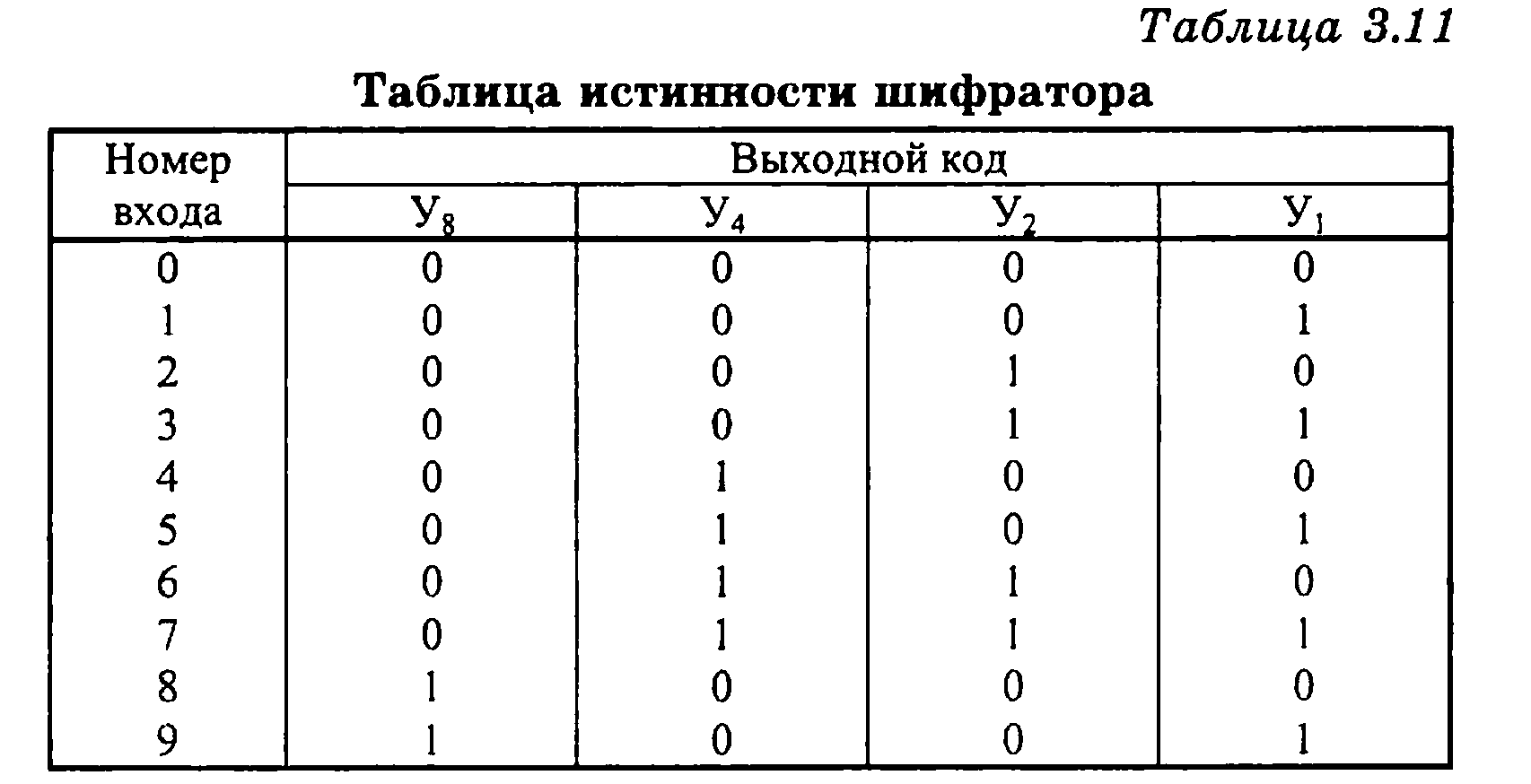

В соответствии с таблицей 3.11 для входов можно записать, полагая активной логическую 1:

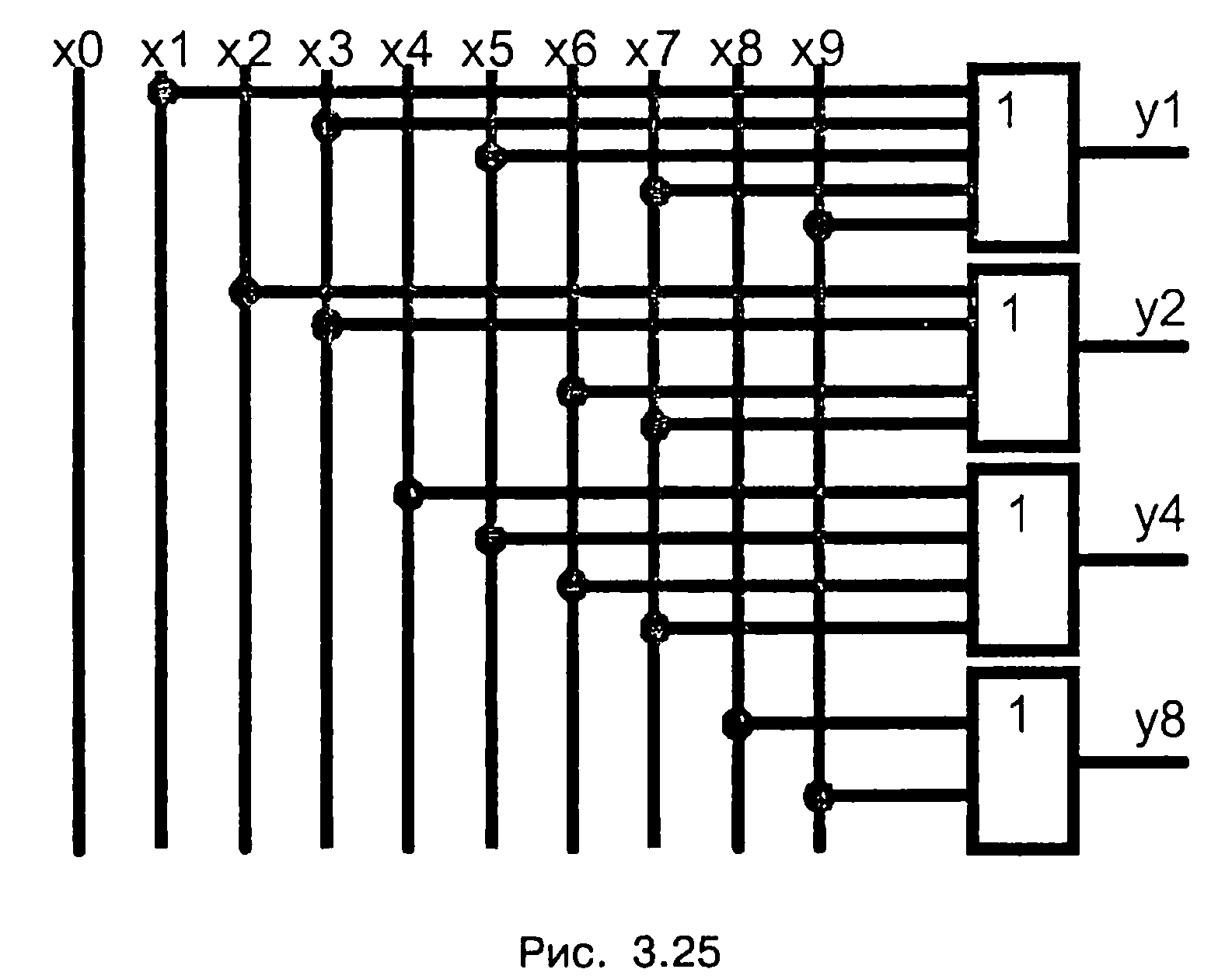

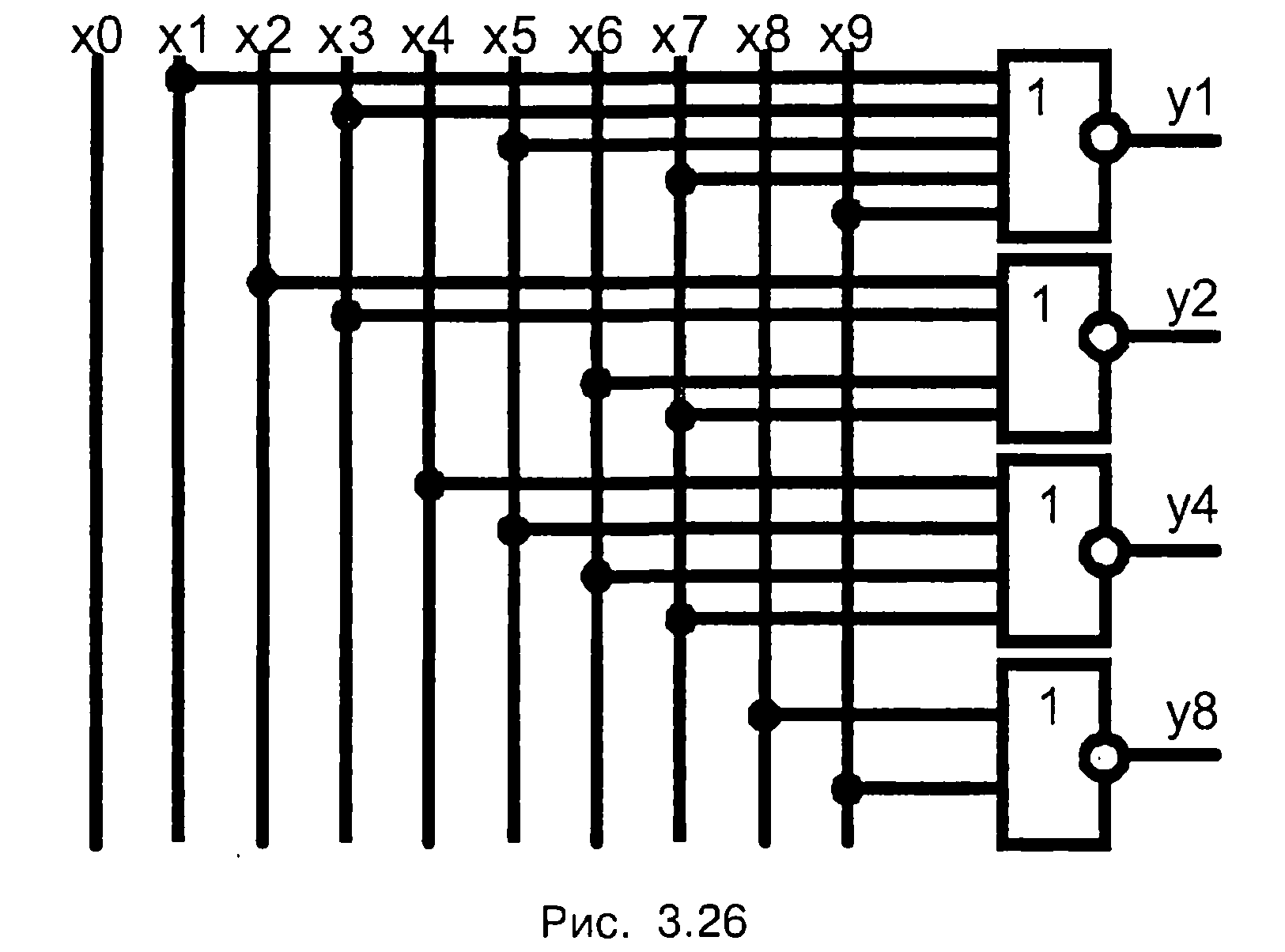

Этой системе уравнений соответствует схема на элементах ИЛИ, показанная на рис. 3.25.

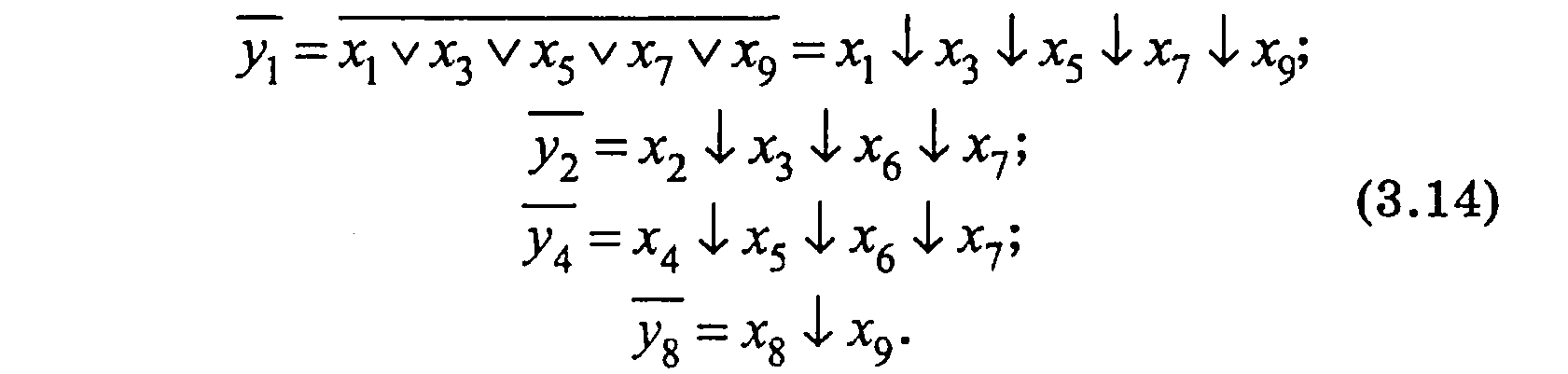

При построении шифратора на элементах ИЛИ-HE он будет иметь инверсные выходы в соответствии с выражениями.

Схема шифратора показана на рис. 3.26.

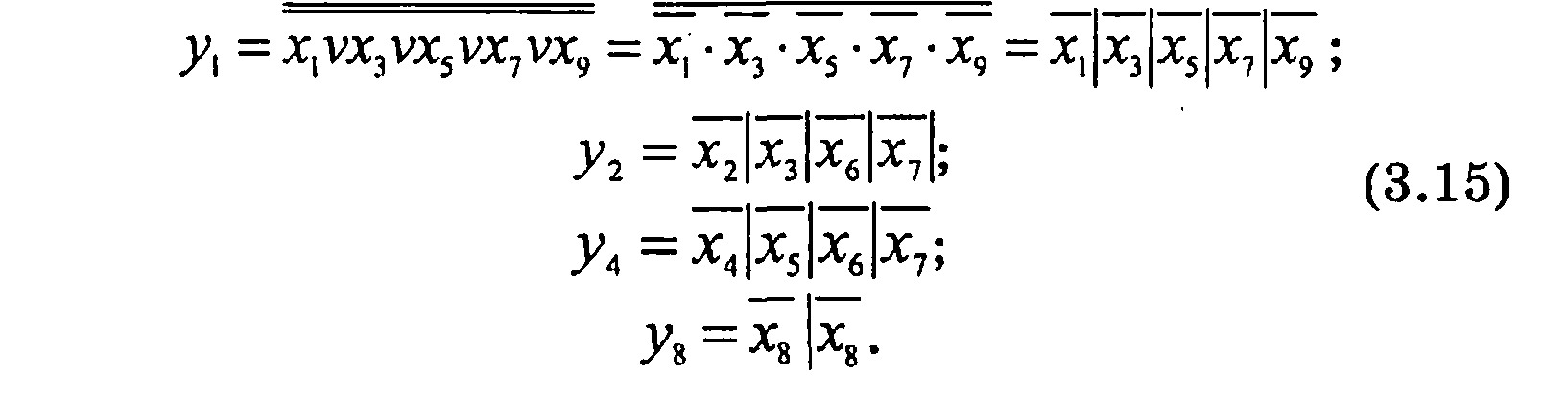

При выполнении шифратора на элементах И-НЕ система выражений приводится к виду

В этом случае на входы необходимо подавать инверсные значения, т. е. для получения на выходе двоичного числа, представляющего определенный вход (десятичную цифру), должен поступить логический 0 на соответствующий вход, а на остальные входы — логическая 1. Схема шифратора на элементах И-НЕ показана на рис. 3.27.

В ТТЛ микросхемах используются шифраторы 8 —> 3 (ИВ1, ИВ2), 10 —> 4 (ИВЗ).

Помимо информационных входов, шифраторы содержат дополнительные, обеспечивающие разрешение ввода и вывода, осуществление расширения без привлечения дополнительных цепей.

При работе шифратора в составе цифрового устройства возможен приход сигналов на несколько входов. В этом случае необходимо выбрать тот вход, которому предоставляется право первоочередного обслуживания. Поэтому шифраторы осуществляют приоритетное кодирование входных сигналов со входа с наивысшим приоритетом.

Таким образом, при наличии на входах нескольких возбужденных линий на выходе будет та комбинация, которая соответствует старшему (приоритетному) входу.

Дополнительные входы также позволяют проводить наращивание шифраторов.

Дешифраторы

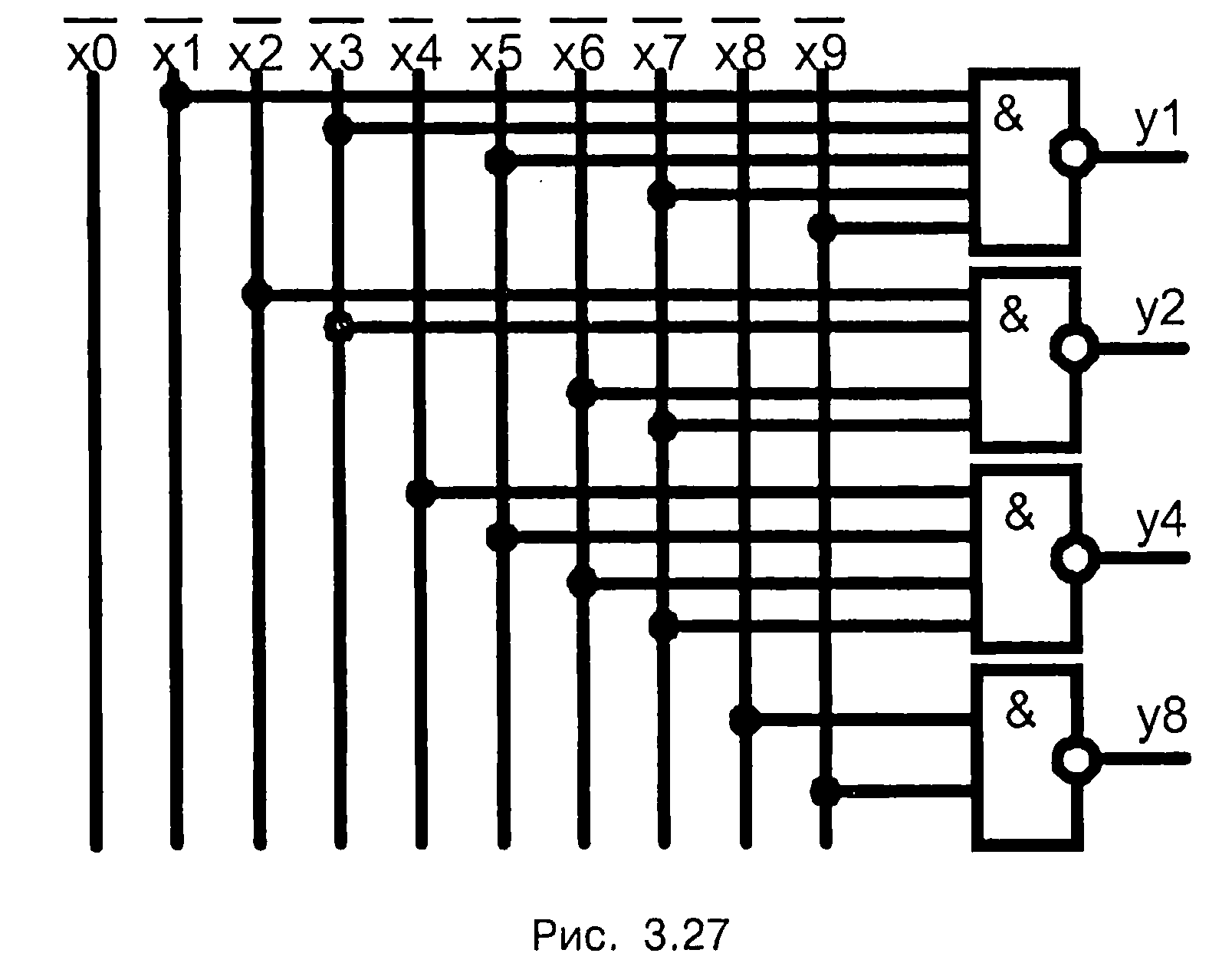

Дешифратор преобразует код, поступающий на его входы, в сигнал только на одном из его выходов, т. е. двоичные дешифраторы преобразуют двоичный код в код «1 из N».

Активным всегда является только один выход дешифратора, причем номер этого выхода однозначно определяется входным кодом.

Дешифраторы относятся к комбинационным устройствам. На принципиальных схемах в условном обозначении дешифраторов ставятся буквы DC (от английского Decoder) (рис. 3.28). Входы дешифраторов обозначаются двоичными весами 1248. В отечественных микросхемах маркировка дешифраторов содержит две буквы ИД, например, К555ИД4, 564ИД5.

Если число адресных входов дешифратора п, то максимальное число выходов 2n. В этом случае дешифратор называют полным. Если число выходов меньше 2n, дешифратор называют неполным. В стандартные серии микросхем входят дешифраторы на 4 выхода (2 разряда входного кода), на 8 выходов (3 разряда входного кода), на 16 выходов (4 разряда входного кода), неполный двоичнодесятичный дешифратор 4x10 (ИД6). Они обозначаются 2-4, 3-8, 4-16, 4-10. Имеются дешифраторы управления различного типа светоизлучающими шкалами.

Дешифраторы различаются по емкости, по числу каналов, а также форматом выходного кода.

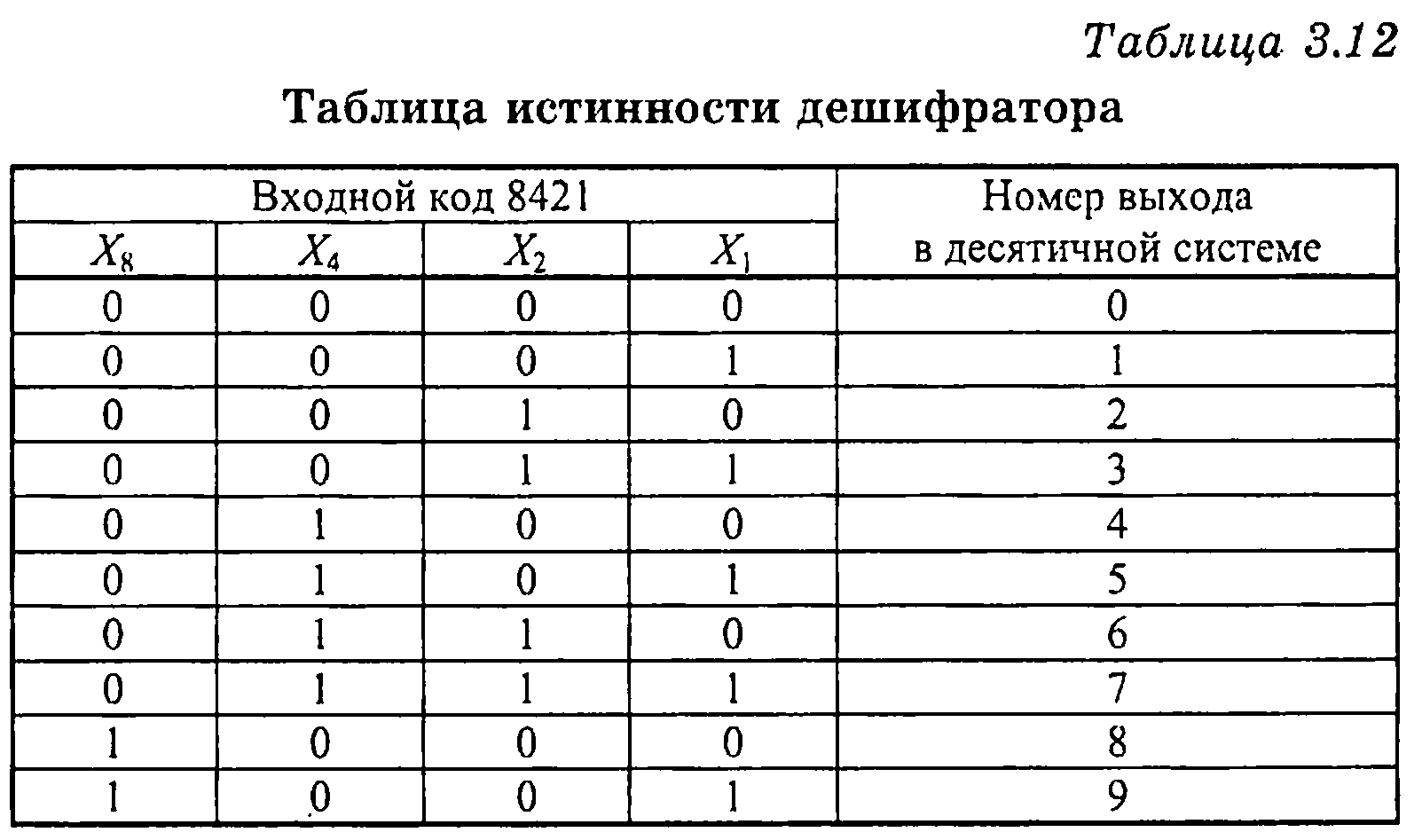

Работа дешифратора описывается таблицей истинности, обратной таблице истинности шифратора. В них входные и выходные сигналы меняются местами. Входные сигналы представлены в коде 8421. В выходной колонке обозначен номер активного выхода.

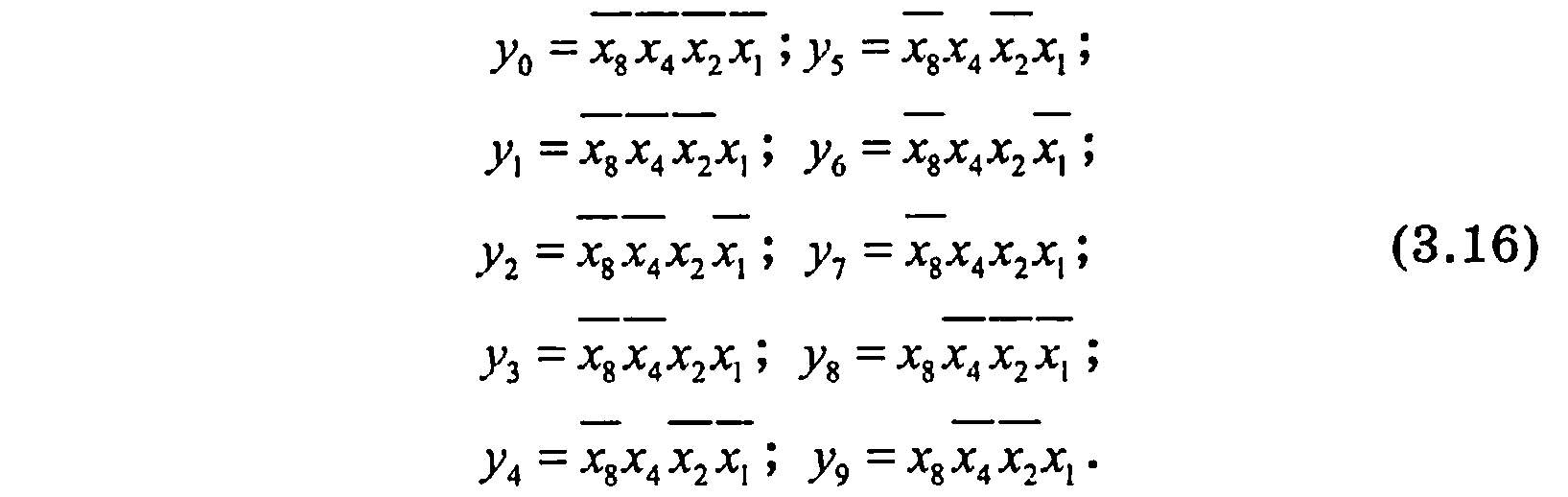

На каждом выходе образуется уровень логической 1 при определенной комбинации на входах. Значения выходных переменных описываются логическими выражениями:

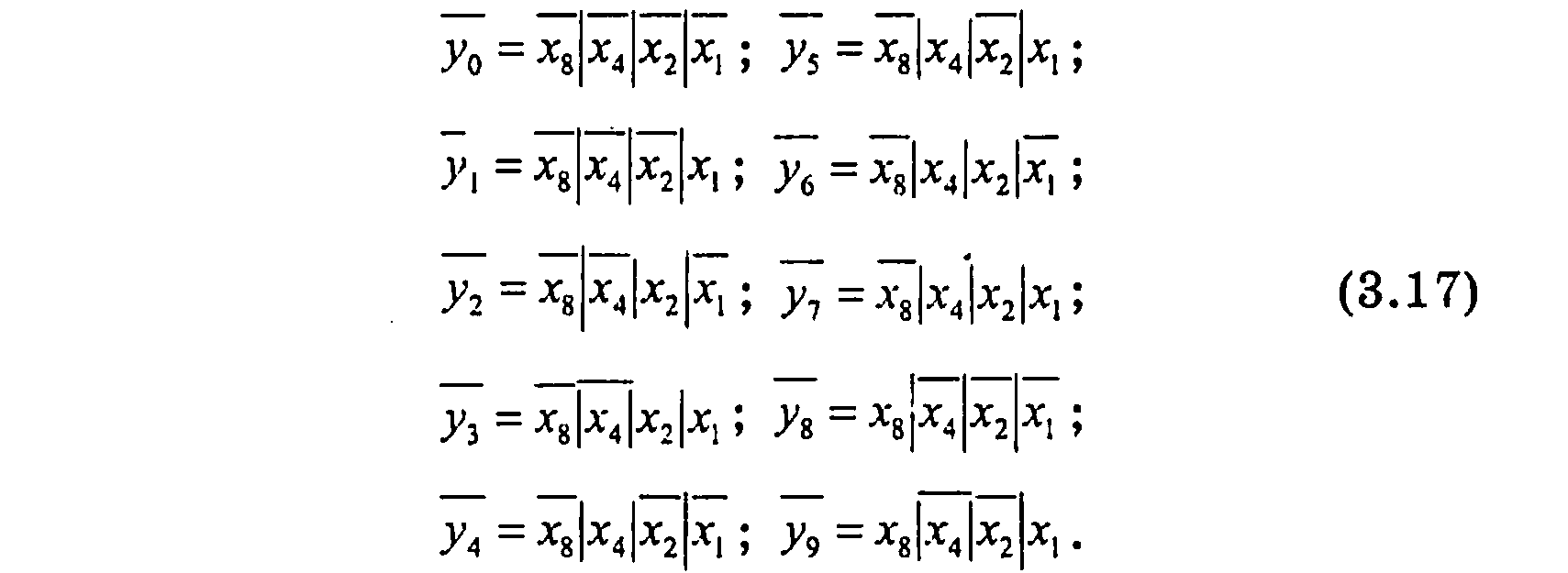

Если дешифратор выполняется на элементах И-НЕ, то выходные сигналы получаем с инверсией. Каждой комбинации входного кода соответствует активный уровень логического нуля на определенном выходе, а на остальных выходах устанавливается уровень логической единицы, формулы (3.16) записываются в виде:

Структура дешифратора с инверсными выходами и его условное графическое обозначение показаны на рис. 3.29.

Дешифраторы с инверсными выходами удобно применять в схемах позиционной индикации на светодиодах. В качестве примера, на рис. 3.29, б показано подключение светодиода к четвертому выходу дешифратора.

Дешифраторы бывают с парафазными и однофазными входами. Применение однофазных входов позволяет уменьшить число линий связи и исключает необходимость дополнительного применения инверторов. Инверсный вход формируется в самом дешифраторе. Более того, входной прямой сигнал также непосредственно в схеме не используется, а получается как двоичная инверсия от входного. Тем самым максимально снимается нагрузка, обусловленная длиной линии связи, ее емкостью, что повышает быстродействие.

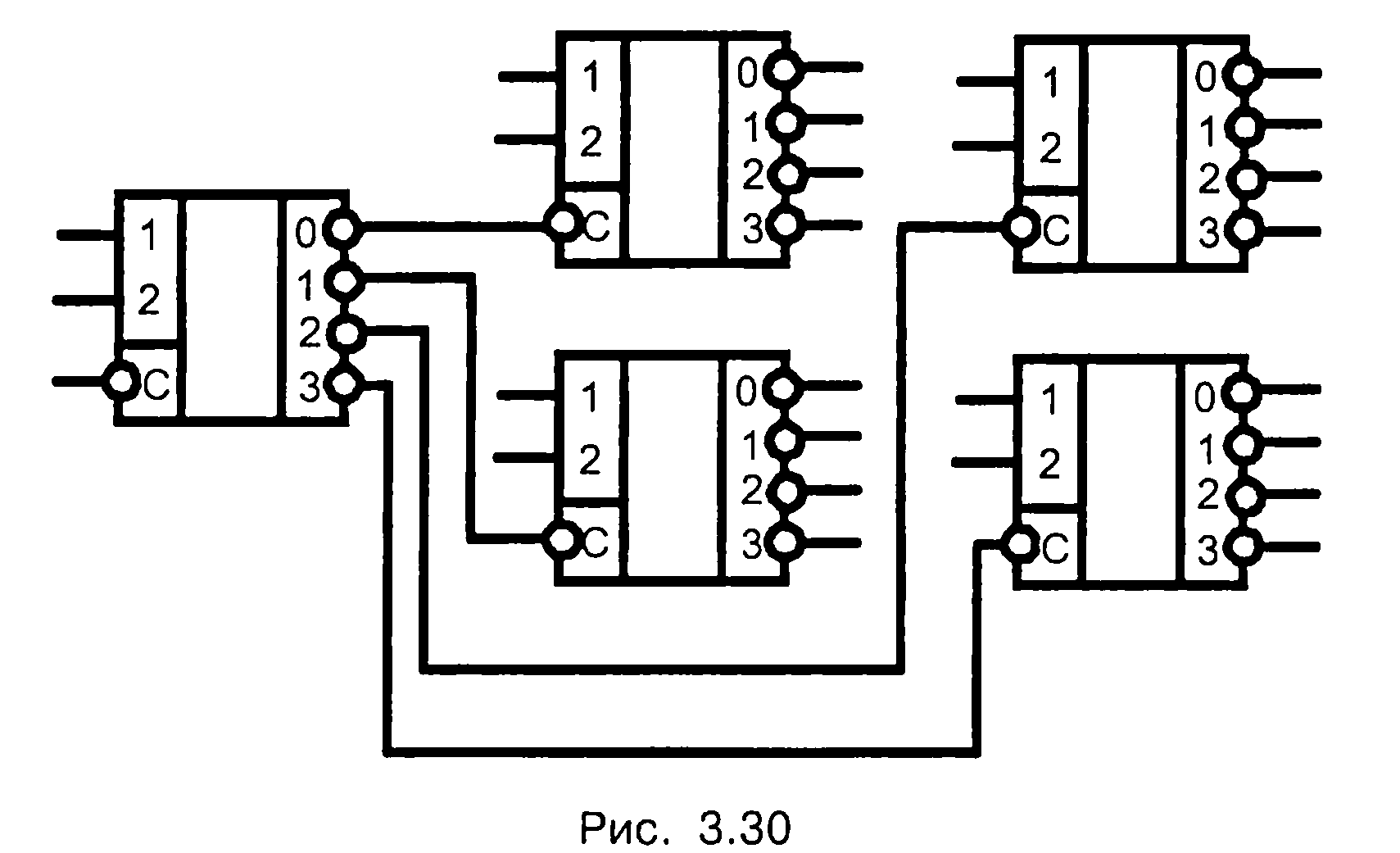

Дешифраторы при относительно малом числе элементов и несложной внутренней структуре имеют большое число внешних выходных выводов. Поэтому не изготавливают дешифраторов с более, чем 4 информационными входами. Увеличение числа выходов осуществляется путем наращивания разрядности (рис. 3.30).

Выходы дешифратора первой ступени подключают к стробирующим входам С разрешения/запрета работы дешифраторов второй ступени. Из дешифраторов второй ступени активным будет только один выход только одного из дешифраторов.

При использовании на второй ступени дешифраторов 3-8 получаем устройство с 24 выходами.

На основе дешифраторов можно строить различные схемы преобразования кодов: мультиплексоры, демультиплексоры, формирователи произвольных логических функций, схемы управления различными индикаторными устройствами и т. д.

Компараторы кодов

Цифровой компаратор — комбинационное устройство, предназначенное для сравнения двоичных слов.

Компаратор выполняет следующие действия над двумя двоичными словами:

F (А = В) — равенство двоичных слов А и В;

F (А > В) — слово А больше слова В;

F (А < В) — слово А меньше слова В.

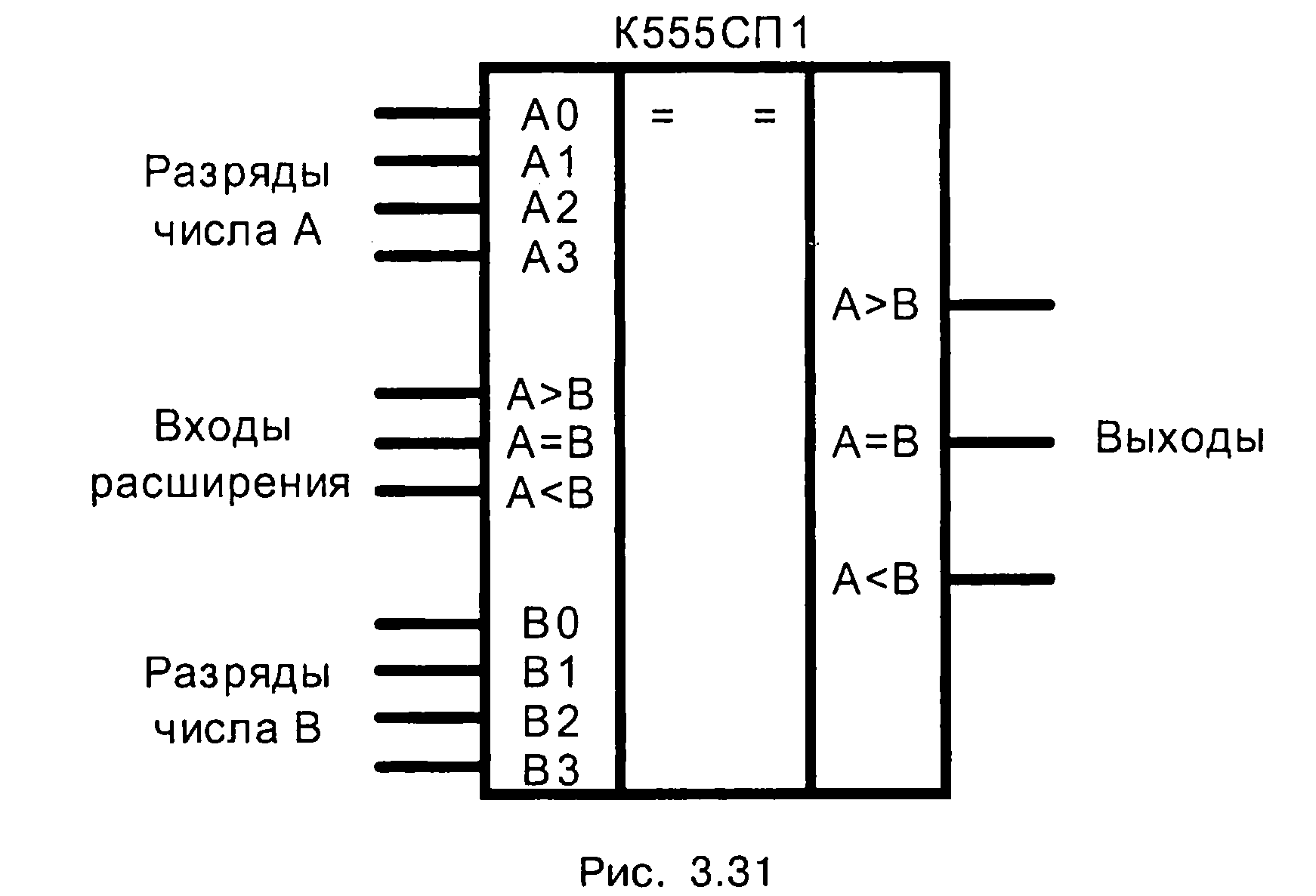

Примером компараторов является микросхема К554СП1 — схема сравнения двух четырехразрядных слов. Результатом является обнаружение одного из трех возможных состояний: А < В,А = В,А> В. Критерием равенства двух двоичных чисел является совпадение их по всем разрядам. Выход схемы сравнения устанавливается в высокое состояние логической 1, если два числа равны, в противном случае выход находится в нулевом состоянии логического нуля.

Микросхема К555СП1 имеет четыре сравниваемых входа чисел А и В (АО, ВО, А1, В1, А2, В2, АЗ, ВЗ) и три дополнительных входа переноса А < В,А = В,А> В для сравнения чисел большей разрядности путем последовательного соединения компараторов в каскад. Возможно построение многоразрядных компараторов в двоичном коде.

Устройства сравнения на равенство строятся на основе поразрядных операций над одноименными разрядами обоих слов. Слова равны, если равны все одноименные разряды, т. е. если в обоих нули или единицы.

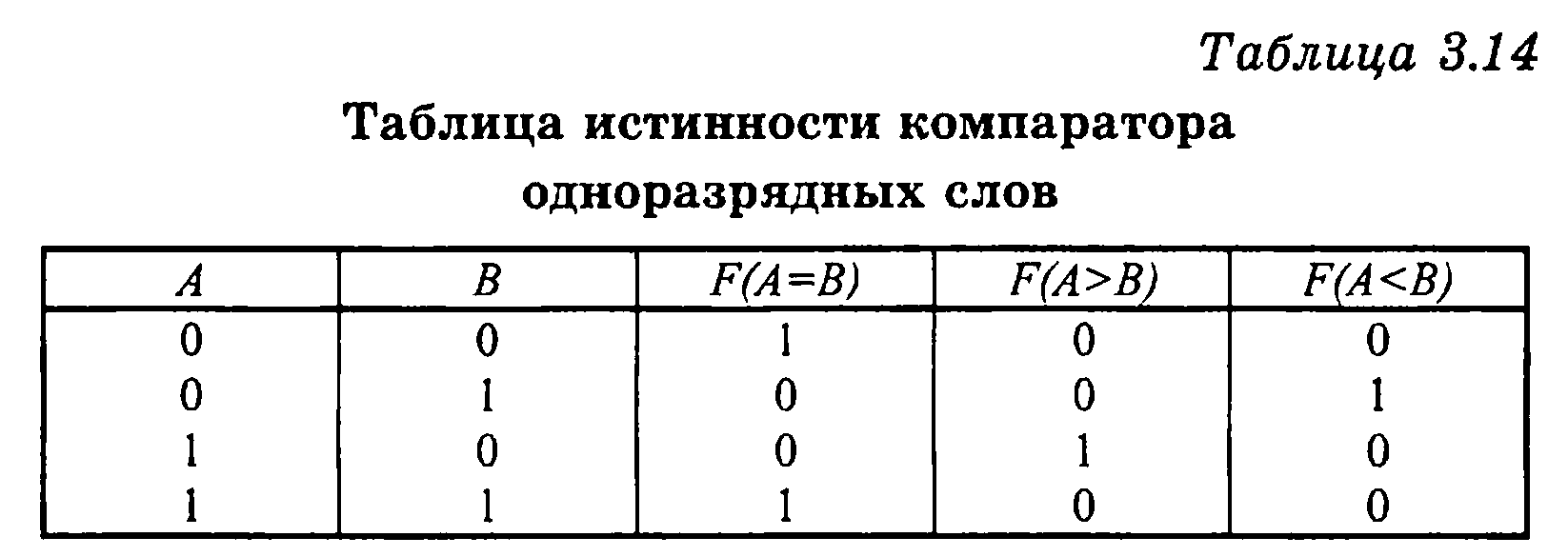

Рассмотрим случай сравнения одного двоичного разряда.

Из таблицы 3.14 видно, что при любой комбинации входных сигналов на выходе компаратора может быть сформирован только один активный логический сигнал.

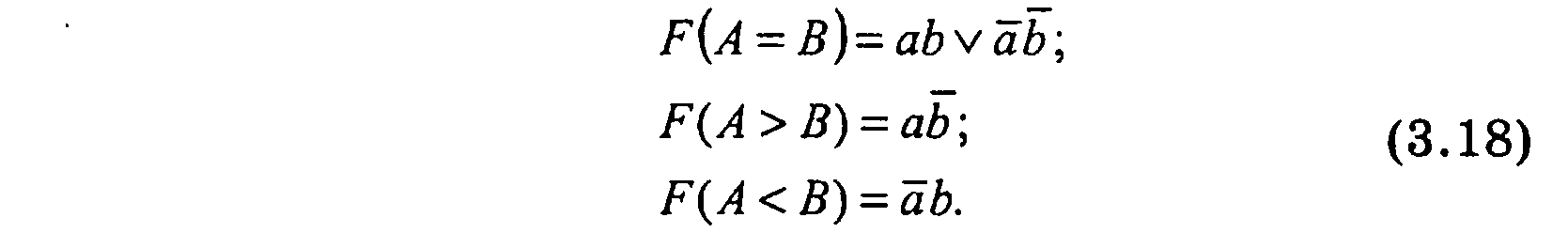

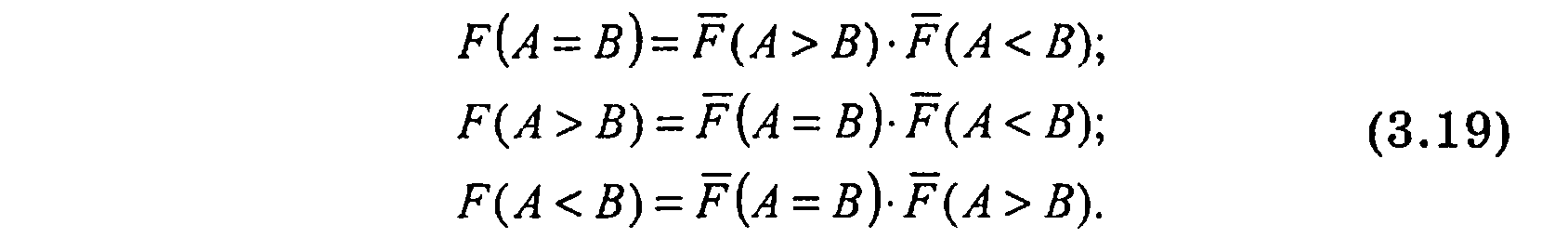

Таблице 3.14 соответствует система логических выражений

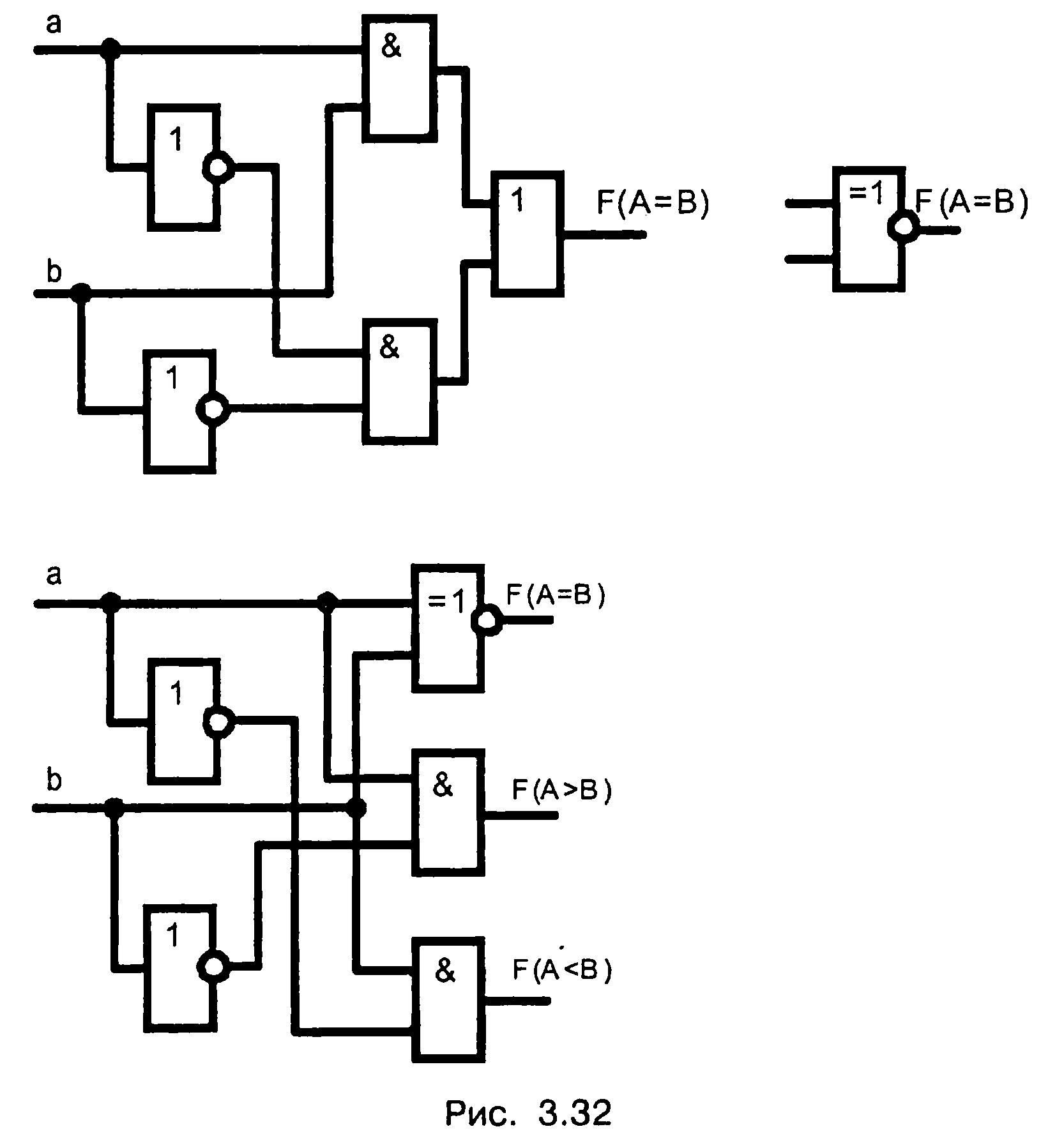

Формулы (3.18) можно реализовать в базисе (И, ИЛИ, НЕ). Остановимся более внимательно на функции F (А = В). Эта функция имеет самостоятельное значение, широко применяется в практике цифровых устройств и называется «ИСКЛЮЧАЮЩЕЕ ИЛИ-HE» (рис. 3.32), инверсия суммы по модулю два.

Использование элемента ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ позволяет упростить реализацию функций F (А = В), F (А > В), F (А < В) согласно формулам (3.18). Соответствующая схема компаратора для одного разряда показана на рис. 3.32.

Отметим, что две из трех функций F (А = В), F (А> В), F (А < В) никогда не могут одновременно принимать единичные значения. Поэтому возможно реализовать только две из них, а третью получить по двум известным. Они связаны между собою соотношениями:

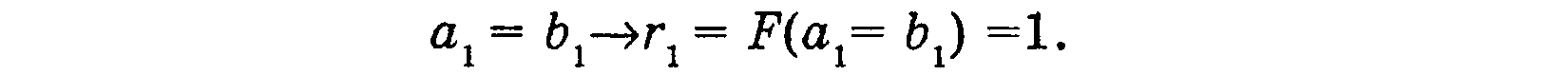

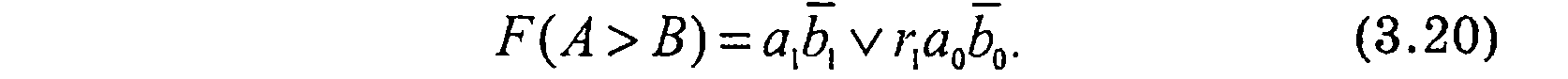

Проверка на равенство двух слов подразумевает равенство каждого разряда. При проверке на «больше» F (А> В) старшие разряды преобладают. Младшие разряды следует проверять при равенстве старших. Обозначим r1 = F (аi = bi) — равенство i-го разряда слова. Тогда для двухразрядных слов проверка А > В сводится к проверке старших разрядов a1,b1 Младшие разряды а0, b0 проверяются при равенстве старших:

Поэтому для слов, имеющих два разряда А (а0, a1), В (b0, b1), запишем формулу проверки А>В

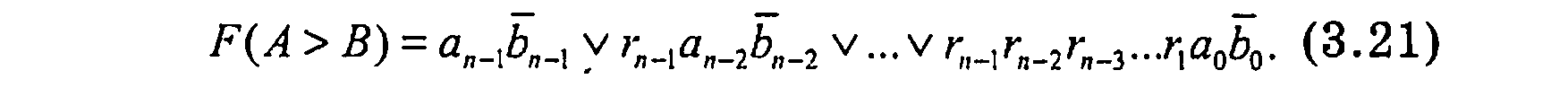

Обобщая формулу (3.20) для слов произвольной разрядности п, получим

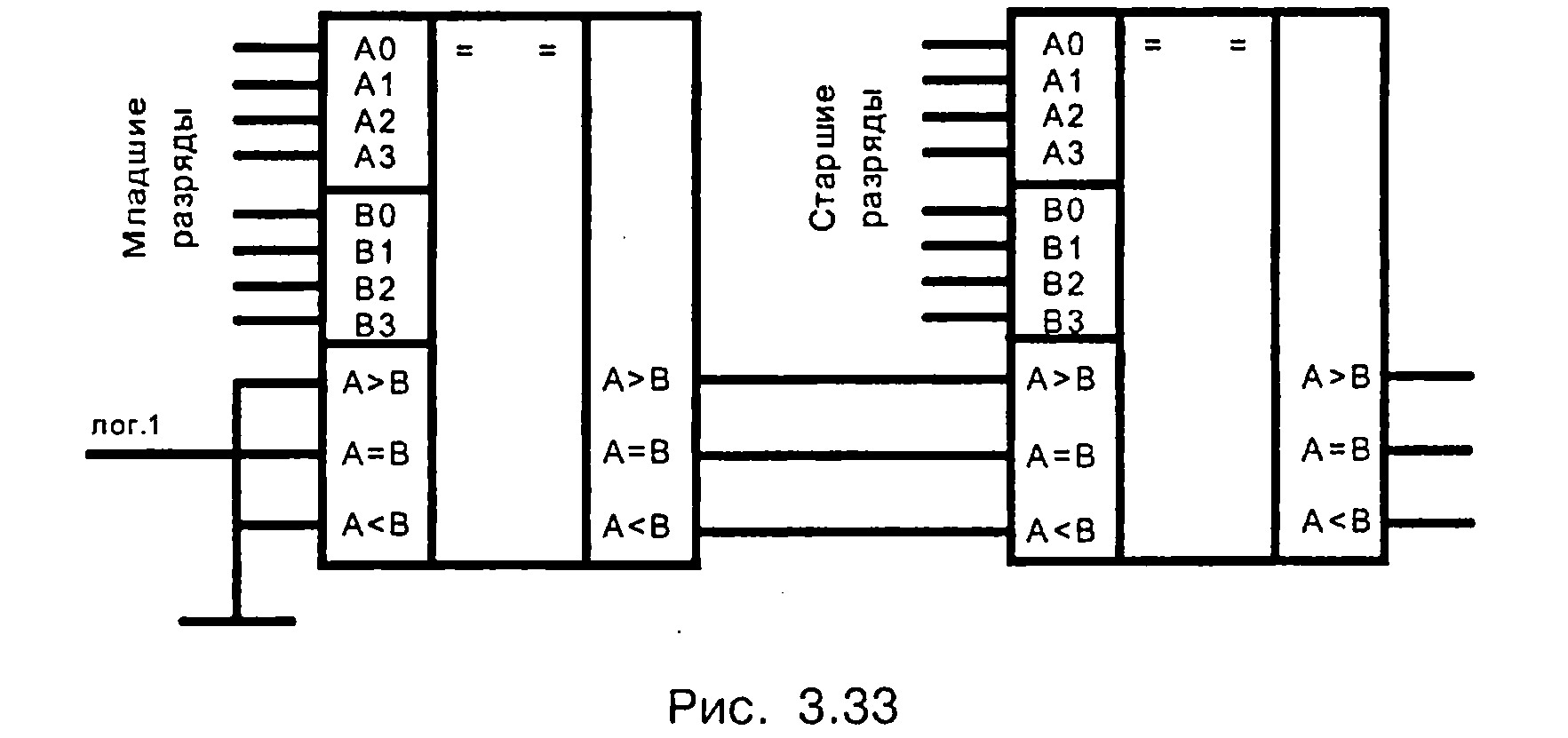

Как уже отмечалась, микросхема К555СП1 предназначена для сравнения четырехразрядных слов. Для сравнения слов большей разрядности компаратор строят наращиванием с использованием нескольких интегральных схем компараторов (рис. 3.33).

Неопределенные состояния на выходах компараторов могут возникать при смене любого из кодов. Это вызвано неодновременным изменением входных сигналов в различных разрядах. На выходах появляются короткие паразитные помеховые импульсы. Борьба с ними осуществляется путем синхронизации и стробирования.

Также надо учитывать, что при каскадировании (рис. 3.32) n-микросхем общая задержка сигнала возрастает в n-раз. Компараторы кодов являются довольно медленно действующими устройствами.

Мультиплексоры

Устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу, называется мультиплексором.

Название произошло от английского Multiplexer. Другими словами мультиплексоры подключают один из входных каналов к выходному под действием управляющего (адресного) кода.

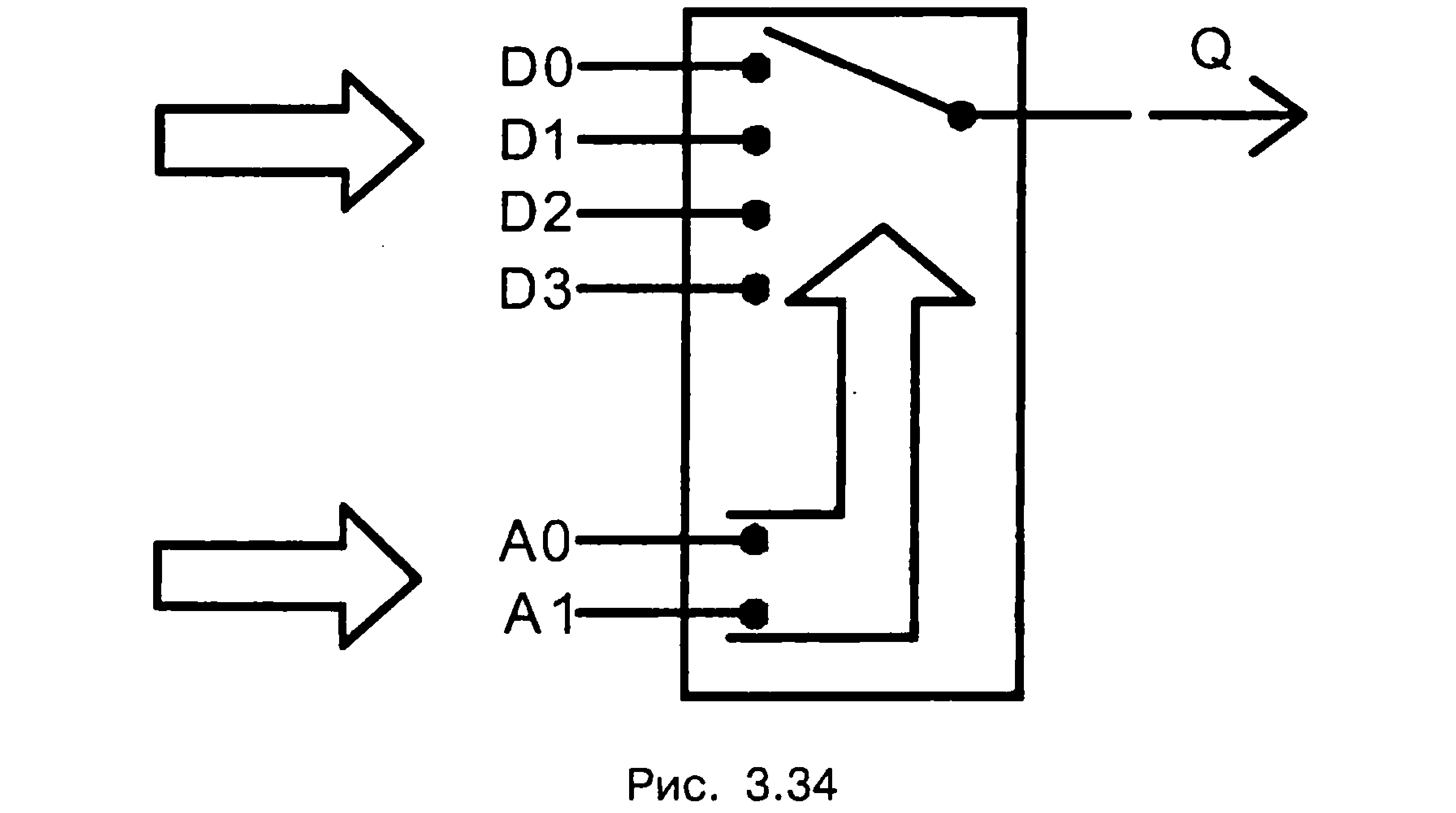

Мультиплексор имеет информационные входы (D0, D1,...), адресные входы (А0, А1, ...), вход С для подачи стробирующего сигнала и один выход Q.

Символически мультиплексор можно представить многоканальным коммутатором, имеющим одностороннюю передачу данных (рис. 3.34).

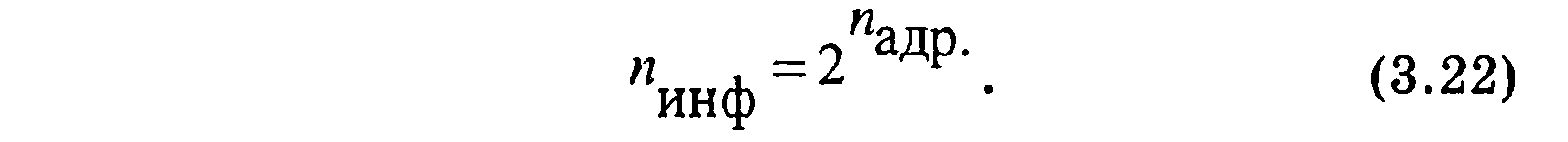

Каждому информационному входу Di мультиплексора присваивается номер А, называемый адресом. При подаче стробирующего сигнала на вход С мультиплексор выбирает один из входов Di, адрес которого задается двоичным кодом на адресных входах А, и подключает его к выходу Q. Число информационных входов пинф и число адресных входов падр связаны соотношением

Мультиплексор представляет собой двухступенчатое устройство, выполненное на основе инверторов и схем типа И-ИЛИ, И-ИЛИ-НЕ, которые используют стробирующие свойства функции И аргументов канала информации и адреса.

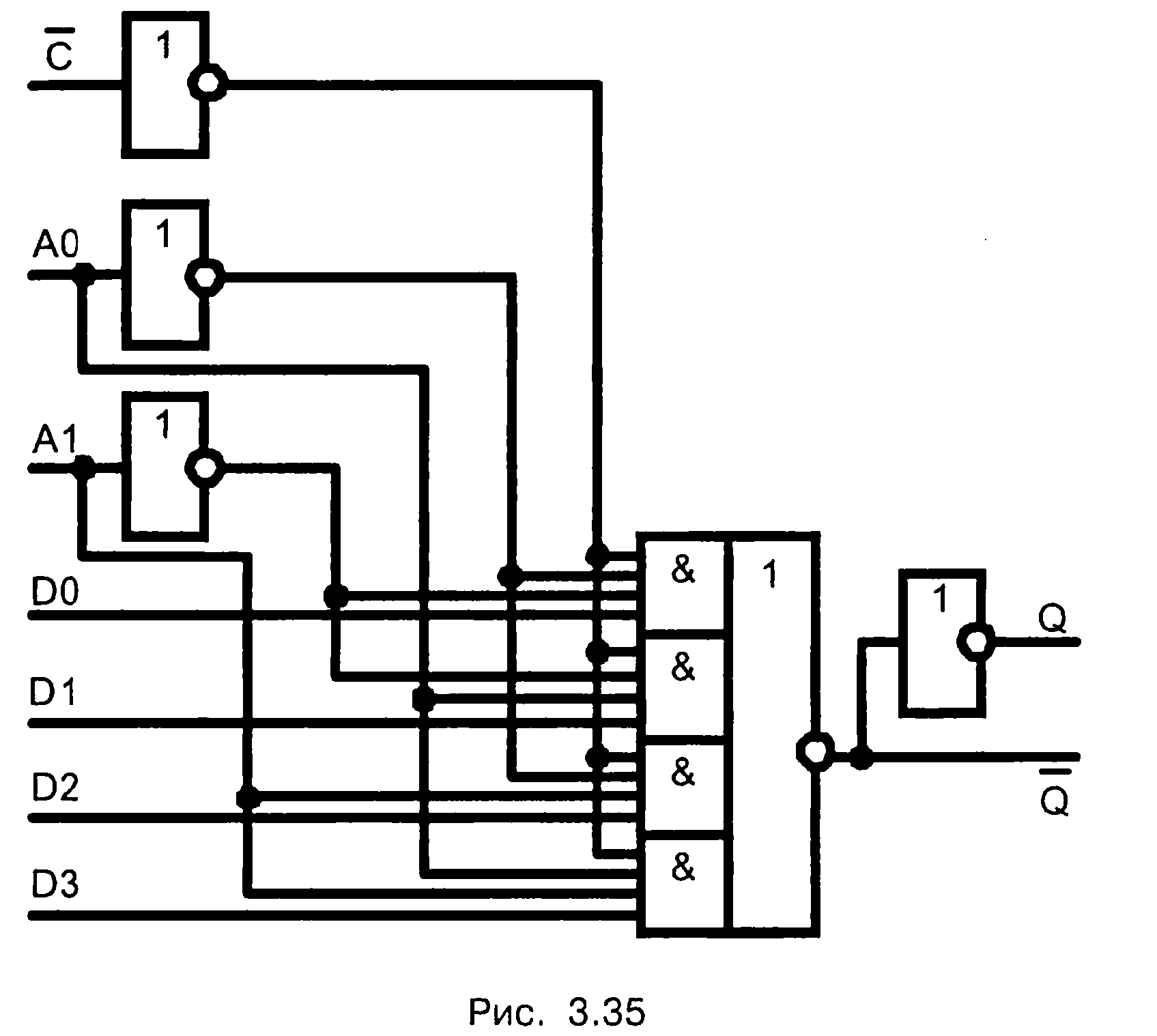

На рис. 3.35 показано символическое изображение мультиплексора с четырьмя информационными входами.

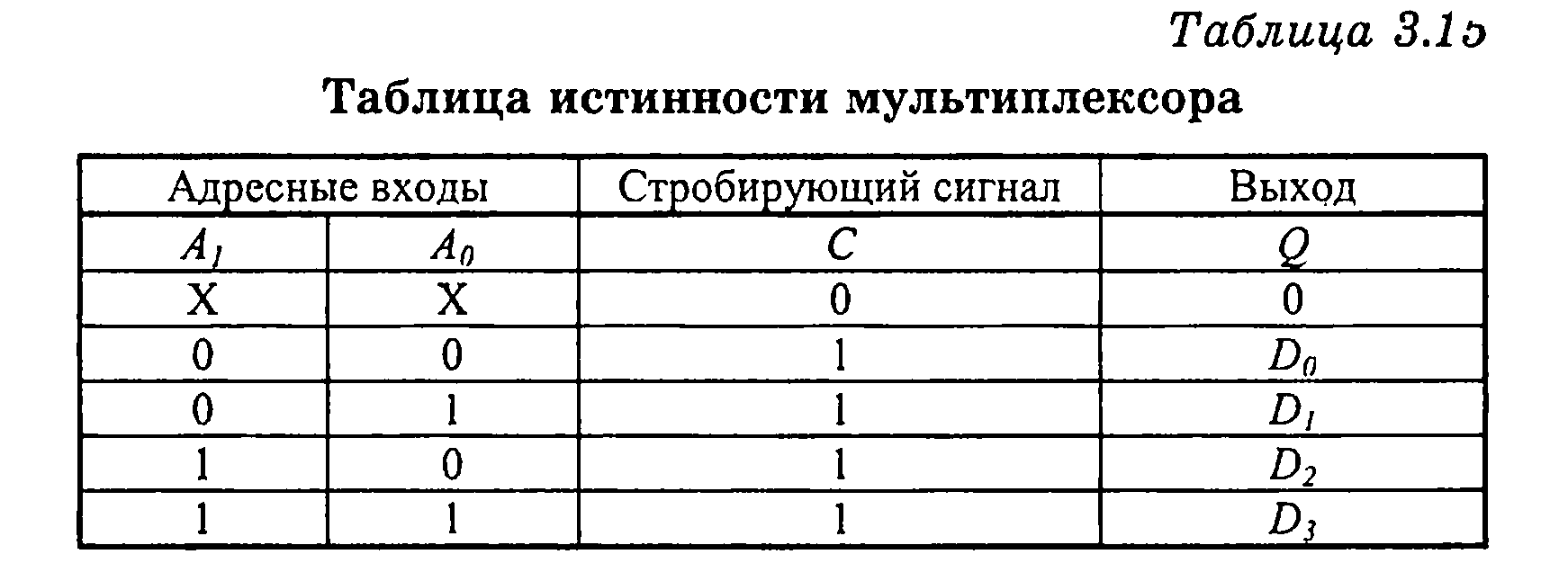

В общем случае функционирование мультиплексора описывается таблицей 3.15.

При отсутствии стробирующего сигнала (С = 0) отсутствует разрешение работы, отсутствует связь между информационными входами и выходом Q = 0. Выход является нулевым независимо от информационных и адресных сигналов. При подаче стробирующего сигнала (С = 1) на выход передается логический уровень того из информационных входов Di номер которого i в двоичной форме задан на адресных входах.

Так, например, при задании адреса А1А0 = 112 = 310 на выход Q будет передаваться сигнал информационного входа с адресом 310, т. е. D2.

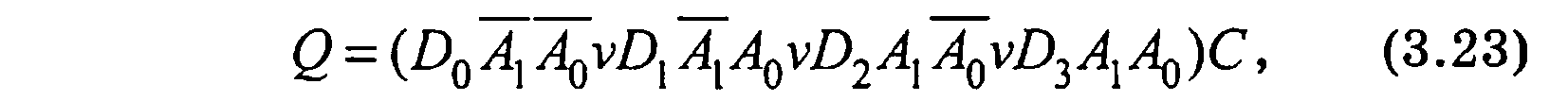

По таблице истинности можно записать следующее логическое выражение для выхода Q:

которое называется мультиплексной формулой. Нетрудно записать формулу для другого количества входов.

В тех случаях, когда требуется передавать на выходы многоразрядные входные данные в параллельной форме, используется параллельное включение мультиплексоров по числу разрядов передаваемых данных.

На схемах мультиплексора обозначаются буквами MS или MUX (MULtipleXer). В отечественных сериях микросхем мультиплексорам соответствуют буквы КП, например: К555КП2 — два мультиплексора ТТЛШ с общим дешифратором адреса канала, К564КП1 — двойной четырехканальный мультиплексор КМОП.

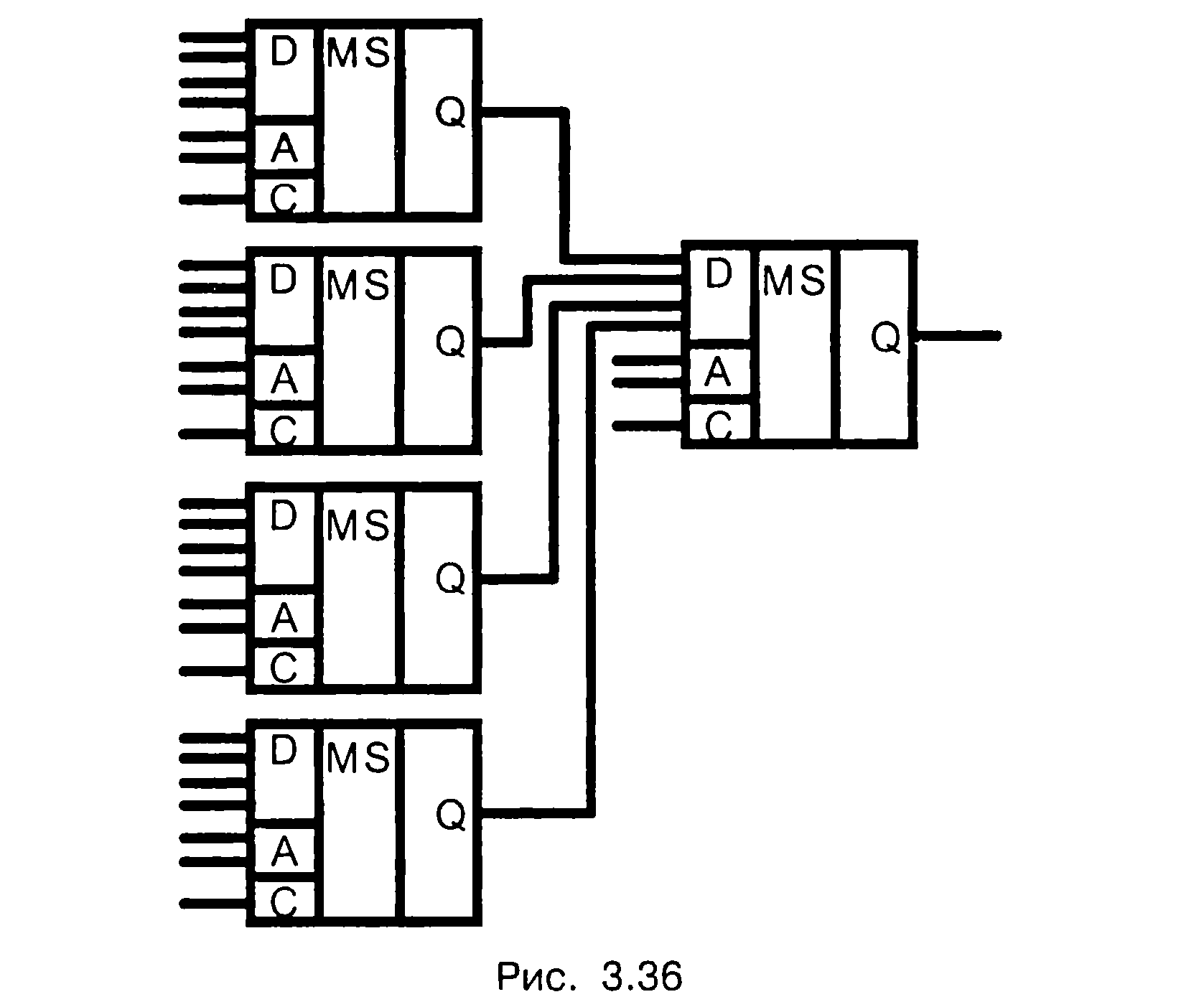

Максимальное число информационных входов мультиплексоров, выполненных в виде интегральных схем, равно 16. Если требуется построить мультиплексорное устройство с большим числом входов, можно объединить мультиплексоры в схему так называемого мультиплексорного дерева. Такое мультиплексорное дерево, построенное на четырехвходовых мультиплексорах, показано на рис. 3.36.

Схема состоит из четырех мультиплексоров первого уровня с адресными переменными A1, А2 и мультиплексора второго уровня с адресными переменными А3, А4. Мультиплексорное устройство имеет 16 входов, разбитых на четверки, которые подключены к отдельным мультиплексорам первого уровня. Мультиплексор второго уровня, подключая к общему выходу устройства выходы отдельных мультиплексоров первого уровня, переключает четверки входов. Внутри четверки требуемый вход выбирается мультиплексором первого уровня. По такой схеме, используя восьмивходовые мультиплексоры, можно построить мультиплексорное устройство, имеющее 64 входа.

На первом и втором уровнях мультиплексорного дерева можно использовать мультиплексоры с разным числом входов. Если на первом уровне такого дерева используются мультиплексоры с числом адресных переменных nадр1, на втором — с числом переменных nадр2, то общее число входов мультиплексорного дерева

а число мультиплексоров в схеме составит

Формулы (3.25) и (3.24) при сравнении с формулой (3.22) показывают эффективность и целесообразность построения мультиплексорного дерева.

Демультиплексор

Демультиплексоры выполняют операцию, обратную операции мультиплексоров — передают данные из одного входного канала в один из нескольких каналов приемников. Демультиплексор имеет один информационный вход и несколько выходов и осуществляет коммутацию входа к одному из выходов, имеющему заданный адрес (номер).

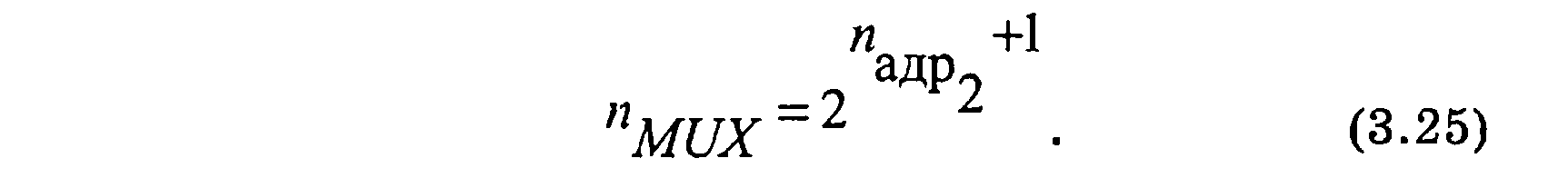

На рис. 3.37 показана структурная схема демультиплексора.

Она включает в себя дешифратор, выходы которого управляют ключами. В зависимости от поданной на адресные входы кодовой комбинации, определяющей номер выходной цепи, дешифратор открывает соответствующий ключ, и вход демультиплексора подключается к определенному выходу.

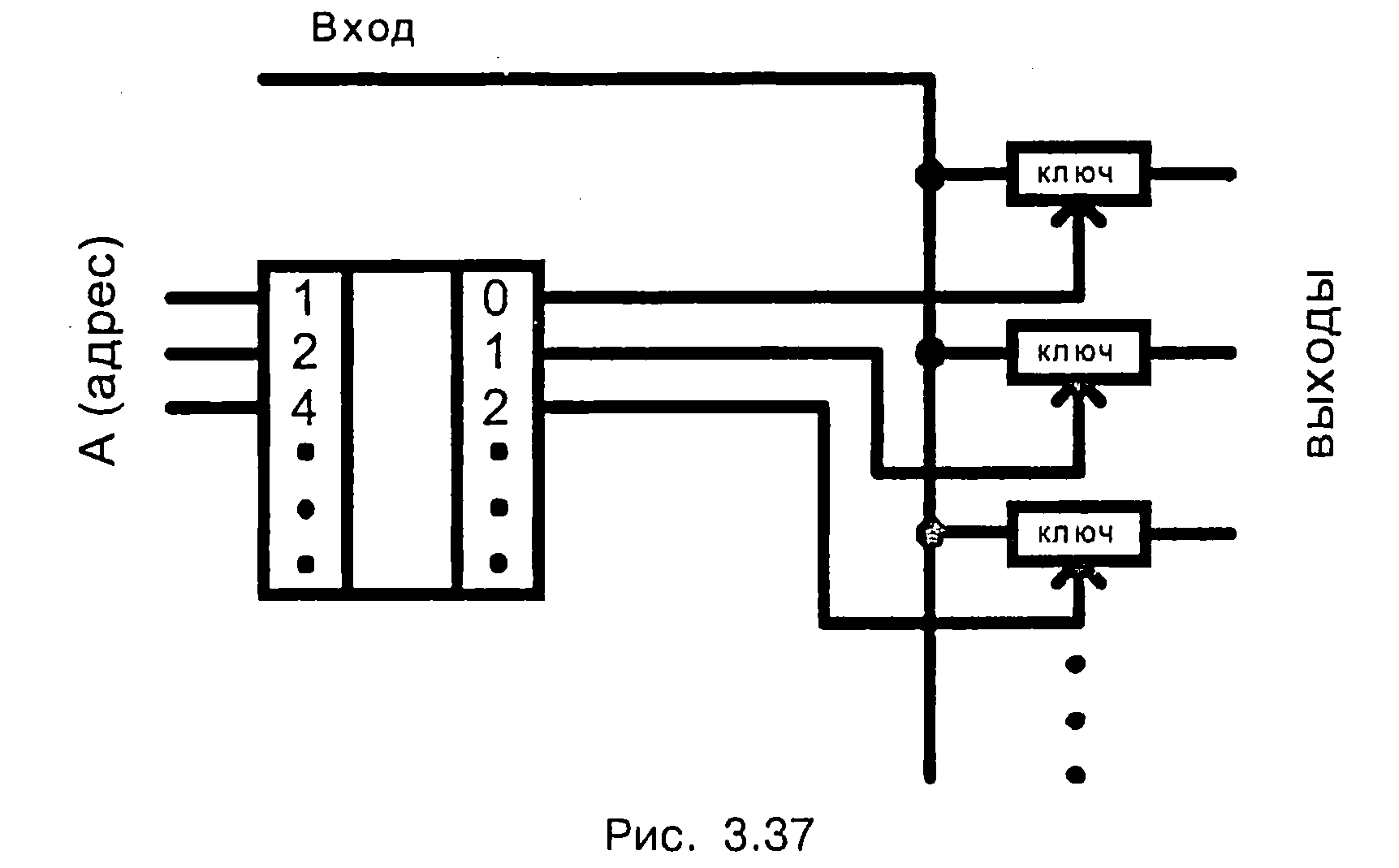

Нетрудно заметить, что дешифратор со входом Е разрешения работы будет функционировать в режиме демультиплексора, если на вход Е разрешения подавать информационный сигнал (рис. 3.38).

Действительно, при единичном значении сигнала Е разрешения работы адресация дешифратора (подача адресного кода на его входы) приведет к возбуждению соответствующего выхода, при нулевом нет. Это означает передачу информационного сигнала в адресованный выходной канал. Поэтому в сериях элементов отдельные демультиплексоры могут отсутствовать, а дешифратор со входом Е разрешения работы часто называют дешифратором — демультиплексором.

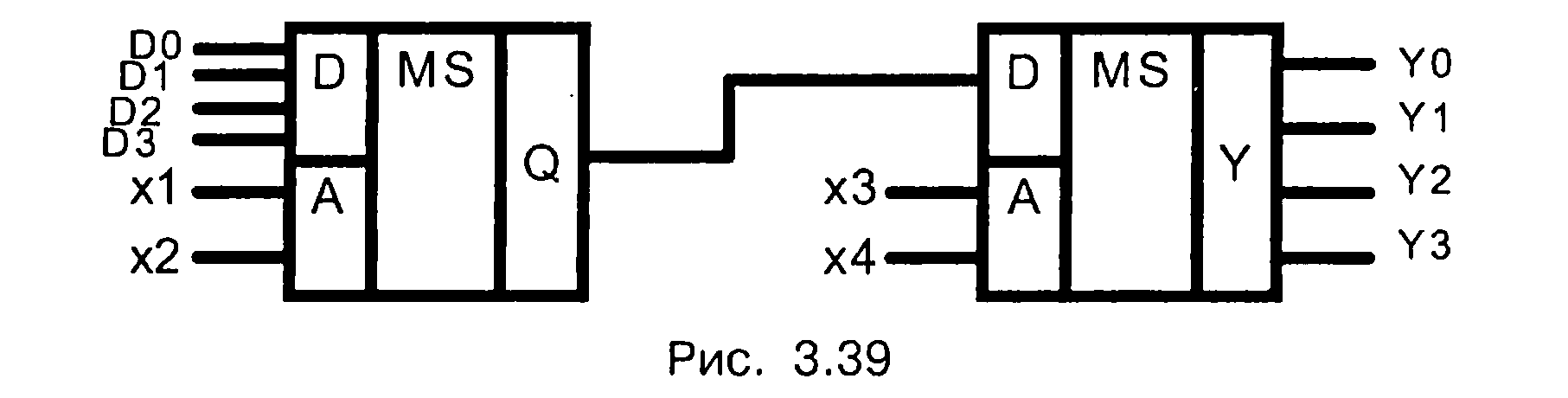

Объединяя мультиплексор с демультиплексором, можно построить устройство, в котором по заданным адресам один из входов подключается к одному из выходов (рис. 3.39).

Таким образом, может быть выполнена любая комбинация соединений входов с выходами. Например, при комбинации значений адресных переменных

Х1 = 1, Х2 = 0, X3 = 0, Х4 = 0

вход D2 окажется подключенным к выходу У0.

Если потребуется большое число выходов, может быть построено демультиплексорное дерево.

| <== предыдущая лекция | | | следующая лекция ==> |

| | | Формы социальных взаимодействий |

Дата добавления: 2015-11-06; просмотров: 28019;