Разработка блока асинхронного обмена по ISA.

Основным типом обмена по ISA является синхронный обмен, то есть обмен в темпе задатчика без учета быстродействия исполнителя. Однако для контроллера параллельного обмена такой тип обмена данными неприемлем ввиду малой по отношению к задатчику скорости УС. Рассмотрим асинхронный обмен, при котором "медленный" исполнитель приостанавливает работу задатчика на время выполнения им требуемой команды. В этом случае надо использовать сигнал I/O CH RDY, снятие которого (установка в состояние логического нуля) говорит о неготовности исполнителя к окончанию цикла обмена. Приостановка задатчика производится на целое число периодов SYSCLK. и не может быть дольше системного времени ожидания 15,6 мкс (для некоторых компьютеров — 2,5 мкс).

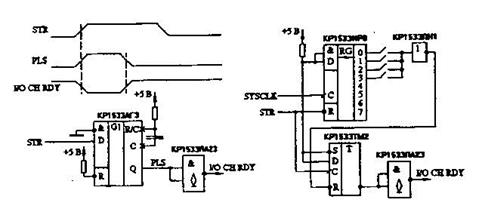

Рис. 2.7. Общая функциональная схема УС, использующего асинхронный обмен.

Существует несколько аппаратурных решений для асинхронного обмена. Прежде всего здесь можно выделить две ситуации: когда генерируется внутренний сигнал УС, говорящий об окончании выполнения функции записи или чтения, и когда такого сигнала нет.

В качестве этого сигнала (обозначим его DK) может выступать, например, сигнал окончания преобразования (готовности данных) АЦП, входящего в состав УС.

На рис. 2.7 представлена структура УС с сигналом DK.

DK может быть потенциальным (то есть сниматься после окончания стробов обмена) или импульсным (то есть окончанию выполнения функции соответствует фронт сигнала DK).

Временные диаграммы и схемы для этих двух случаев показаны на рис. 2.8 и 2.9 (для упрощения считаем, что строб обмена — единственный).

Рис. 2.8. Реализация асинхроннного обмена при потенциальном DК.

Рис. 2.9. Реализация асинхроннного обмена при импульсном DК

Если сигнал DК отсутствует в явном виде, но известно время выполнения функции или его верхний предел, то необходимо сформировать задержку в самой интерфейсной части.

На схеме (рис. 2.10) слева эта задержка определяется временем выдержки одновибратора. Такая схема требует точной настройки. Это связано с тем, что любые аналоговые цепи подвержены действию помех. Поэтому справа приведена схема с использованием линии задержки на сдвиговом регистре, задержка которой определяется номером замкнутого переключателя и задается с точностью до периода сигнала SYSCLK. Но, в принципе, в данном случае требования к точности времени задержки невысоки, и использование одновибратора и даже простой RC-цепочки вполне допустимо.

Рис. 2.10. Формирование задержки с помощью одновибратора и линии задержки.

Асинхронный режим обмена по ISA можно реализовать и на более высоком уровне: путем опроса задатчиком флага готовности исполнителя и путем использования прерываний. Эти решения удобны в случае очень медленных УС, то есть тех, время исполнения функции которыми превышает предельное системное время задержки.

Рассмотрим обобщенную принципиальную схему контроллера параллельного обмена, включающую в себя все вышеописанные узлы (рис. Приложение 2). Здесь использованы входные буфера (не обязательны), двунаправленный буфер данных (в общем случае должен быть разделен на два для каждого байта), выходной буфер, селектор адреса, формирователь внутренних стробов и формирователь сигнала асинхронного обмена I/O СН RDY (DK).

Какими могут быть предельные значения времен задержек всех узлов интерфейсной части? Здесь надо рассмотреть две ситуации. Если УС работает только в режиме записи в него информации, то желательно, чтобы задержка сигнала STR относительно сигнала -IOW и задержки сигналов данных были примерно одинаковыми. Ни в коем случае задержка сигнала STR не должна превышать задержку данных более чем на 30 не, иначе УС примет неверные данные. Разность задержки буферирования и селектирования адреса и задержки буферирования сигнала -IOW не должна превышать 91 не, иначе УС не будет реагировать на свой адрес. Если наше УС работает только в режиме чтения из него информации, то сумма задержки сигнала STR относительно сигнала -IOR и задержки буфера данных не должна превышать 110 не, иначе процессор примет неправильные данные от УС. Требования к буферу адреса и селектору адреса те же. Если же наше УС должно работать как в режиме чтения, так и в режиме записи, то оно должно удовлетворять всем перечисленным требованиям.

Универсальный многоразрядный контроллер параллельного обмена информацией является очень полезным устройством. С его помощью компьютер может общаться с любыми цифровыми устройствами в статическом режиме (то есть в темпе, не превышающем быстродействие компьютера).

Сформулируем требования к разрабатываемому контроллеру:

Во-первых, он должен иметь большое количество линий связи с внешними устройствами (естественно, чем больше, тем лучше, но ограничением сверху здесь выступает количество контактов и размер используемого внешнего разъема, а также размер платы ISA).

Во-вторых, для большей универсальности контроллера должна быть предусмотрена возможность простого изменения количества входных и выходных линий (в идеале все линии — двунаправленные, и направление передачи задается для каждой из них отдельно, но здесь также есть ограничение — это допустимое количество микросхем и размер печатной платы).

Исходя из этих соображений, разработан 56-разрядный контроллер с побайтным управлением направления передачи. Как показывает практика, этого хватает для большинства возникающих задач.

При побайтном управлении внешними линиями можно ограничиться 8-раэрядным обменом (скорость передачи информации здесь не очень важна), и тогда для обмена данными потребуется 7 адресов в адресном пространстве ввода/вывода. Помимо этого в УС надо записывать 7 бит управляющего слова, которое будет определять направление передачи информации для каждого из семи внешних 8-разрядных портов. Поэтому УС необходимо в целом 8 адресов. Нужны ли здесь прерывания? Желательны, но не обязательны: можно ограничиться и опросом флага готовности. Прямой доступ к памяти нe нужен совершенно.

Дата добавления: 2015-10-13; просмотров: 923;