Предделители таймеров/счетчиков

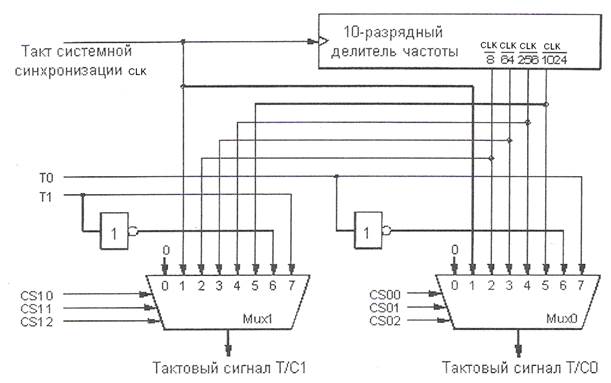

Как уже говорилось ранее, каждый таймер микроконтроллера может работать от двух разных источников тактовых импульсов. Либо это внешние импульсы, либо импульсы, вырабатываемые внутренней схемой микроконтроллера. Какой бы источник сигналов ни был выбран, перед тем, как попасть на вход таймера, этот сигнал проходит схему предварительного делителя. Предварительный делитель предназначен для того, чтобы расширить диапазон формируемых частот и длительностей таймера. Каждая микросхема АVR имеет свою структуру предварительного делителя для таймеров/счетчиков. Упрощенная схема одного из вариантов предварительного делителя приведена на рис. 5.1.

Как видно из приведенных схем, в микроконтроллеры интегрированы 10- ступенчатый делитель и мультиплексоры, осуществляющие подключение соответствующего выхода делителя ко входу счетчиков.

С выходов делителя снимаются сигналы СLК/8, CLK/64, CLK/256 и CLK/1024. В схеме имеют место цепи, через которые на вход таймера могут поступать внешние импульсы Т0 и Т1.

Рис.5.2

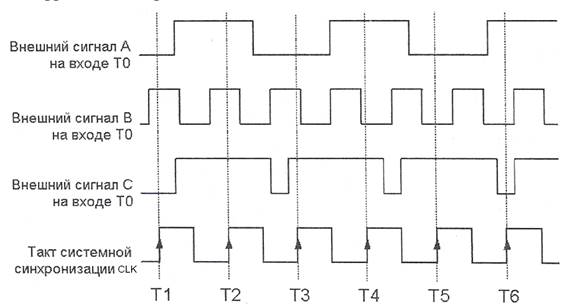

В режиме работы «Счетчик», в качестве активного фронта с помощью мультиплексора может быть выбран нисподающий или нарастающий фронт внешнего импульса на входах Т0 и Т1. При таком режиме внешний сигнал Т0 (как и Т1) синхронизируется с тактом системной синхронизации СLК внутреннего кварцевого осциллятора. Для этого внешний сигнал проверяется в течение каждого нарастающего фронта СLК (рис.5.2).

Рис.5.2.

На рис. 5.2 показаны различные сигналы, синхронизируемые сигналом CLK, при этом необходимо отметить, что только сигнал А синхронизируется без потери информации. Это необходимо учитывать при выборе частоты работы МК.

Все счетные сигналы поступают на входы данных мультиплексора. На адресные входы мультиплексора поступают сигналы от трех разрядов регистра управления таймером (TCCRn).

Таким образом, записывая в разряды CSn0, CSnl, CSn2 различные значения, можно выбирать один из восьми режимов работы предделителя. В зависимости от выбранного режима, на выход схемы могут поступать сигнал с одного из выходов десятиразрядного делителя, прямой сигнал с тактового генератора либо нулевой логический уровень (входа D0). В последнем случае сигнал на входе таймера будет отсутствовать, и его работа приостанавливается.

| CSn2 | CSn1 | CSn0 | Описание |

| Источник тактирования не выбран. (Счетчик остановлен). | |||

| clkI/O/1 (Не предварительного деления). | |||

| clkI/O/8 (Тактовый сигнал с пред. делителя). | |||

| clkI/O/64 (Тактовый сигнал с пред. делителя). | |||

| clkI/O/256 (Тактовый сигнал с пред. делителя). | |||

| clkI/O/1024 (Тактовый сигнал с пред. делителя). | |||

| Внешнее тактирование с вывода Tn. Такт по спадающему фронту сигнала. | |||

| Внешнее тактирование с вывода Tn. Такт по нарастающему фронту сигнала. |

Здесь величиной clkI/O обозначена частота тактирования процессора.

Таким образом, схемы предделителей обеспечивают следующие восемь различных вариантов формирования счетных импульсов:

· 0- отсутствие импульсов;

· 1- «таймер», прямой сигнал от внутреннего генератора;

· 2...5- «таймер», один из сигналов с делителя;

· 6- «счетчик», инверсный сигнал с внешнего входа (активный

ниспадающий фронт);

· 7- «счетчик», прямой внешний сигнал (активный нарастающий

фронт).

Схема, приведенная на рис. 5.1, не является стандартом для всех микроконтроллеров серии АVR. Она отражает лишь общий принцип построения предделителей. В разных моделях это сделано немного по-разному.

Как уже отмечалось, способ тактирования определяется битами CSn2:0 (Clock Select), расположенными в регистре управления TCCRnB.

Дата добавления: 2015-08-11; просмотров: 747;