JTAG порт

JTAG порт реализует соединение между стендом DE2-70 и инструментальным компьютером. Это соединение используется пакетом Quartus II для загрузки файла программирования в кристалл ПЛИС на плате, посредством чего создаётся процессорная система. Соединение также используется приложением AMP для загрузки программы в процессорную систему и управления её выполнением.

Порт JTAG включает универсальный асинхронный приемопередатчик (UART), который может использоваться для передачи символьных данных между инструментальным компьютером и программой, выполняемой в процессорной системе на стенде. Причем обмен между процессором Nios II и портом JTAG осуществляется параллельным кодом, а между JTAG и инструментальным компьютером последовательным кодом.

Если на инструментальном компьютере используется приложение AMP, то для передачи символьных данных в порт JTAG их следует печатать в терминальном окне приложения, предварительно поместив туда курсор с помощью мыши. Вывод символов в порт JTAG из процессорной системы Nios II будет приводить к отображению их в терминальном окне приложения АМР, выполняющегося на инструментальном компьютере.

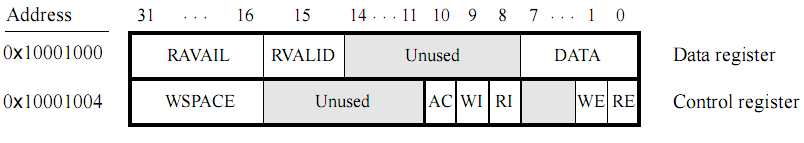

Программный интерфейс JTAG порта состоит из двух 32-битных регистров, показанных на рис. 3.10. Регистр, доступный по адресу 0x10001000, является регистром данных. Регистр, доступный по адресу 0x10001004, является регистром управления.

Рис. 3.10 – Регистры порта JTAG UART

Когда символьные данные из инструментального компьютера посылаются в JTAG UART, то они сохраняются в 64-символьном буфере FIFO. Число символов, хранимых в настоящий момент в буфере FIFO, указывается в поле RAVAIL, которое представлено разрядами 31-16 регистра данных. Если буфер FIFO переполнен, то дополнительно посылаемые в него данные со стороны инструментального компьютера будут потеряны. Если данные присутствуют в буфере FIFO, то величина RAVAIL будет больше нуля и 15-ый бит регистра данных RVALID будет равен 1. Для процессора Nios II рассматриваемый буфер будет содержать вводимую им информацию. Поэтому будем называть его принимаемым. То есть он содержит предназначенные для чтения процессором Nios II символы.

Чтобы осуществить чтение символа из вершины буфера FIFO, необходимо прочитать содержимое регистра данных JTAG порта. При этом младшие разряды 7-0 регистра данных будут содержать вводимый символ. Поле RAVAIL при выполнении чтения автоматически уменьшится на единицу, и это уменьшенное значение как раз и будет получено в результате чтения. Если данных в принимаемом буфере FIFO нет, то поле RVALID будет содержать нулевое значение, и результат чтения из разрядов 7-0 регистра данных будет не определен.

Контроллер JTAG UART также включает 64-символьный буфер FIFO, который хранит данные, ожидающие передачи в инструментальный компьютер. Символьные данные загружаются в этот буфер посредством записи в разряды 7-0 регистра данных. Следует заметить, что запись в этот регистр не оказывает никакого влияния на получаемые данные. Размер доступного пространства в текущий момент времени в записываемом буфере FIFO указывается в разрядах 31-16 регистра управления. Это поле WSPACE (см. рис. 3.10). Если буфер FIFO полон, то все данные, в последующем записываемые в регистр данных, будут теряться.

Бит 10 в регистре управления, названный AC, устанавливается в 1, если к JTAG UART был доступ со стороны инструментального компьютера. Этот бит может быть использован для проверки наличия установленного соединения инструментального компьютера с платой DE2-70. Бит АС может быть вновь очищен посредством записи в него 1. Биты регистра управления RЕ, WE, RI, WI обсуждаются в разделе 3.3.2.

Дата добавления: 2015-05-30; просмотров: 776;