Основные характеристики ЭВМ 7 страница

В ЭВМ счетчики используются для подсчета импульсов, сдвигов, формирования адресов и т.д. Функционально различают:

Ø суммирующие,

Ø вычитающие,

Ø реверсивные счетчики.

Они также отличаются друг от друга логикой работы дополнительных логических элементов, подключаемых к триггерам.

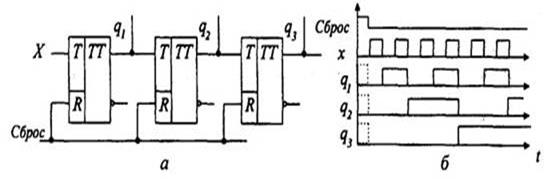

В основу построения любого счетчика положено свойство Т-триггеров изменять свое состояние при подаче очередного сигнала на счетный вход Т. На рисунке 3.30 показана схема трех разрядов суммирующего счетчика, построенного на Т-триггерах. Логика его работы представлена в таблице 3.9.

Таблица 3.9 – Таблица переходов трехразрядного счетчика

| Вход х | Состояние | ||||||||

| Режим | |||||||||

| Хранение Счет |

Рисунок 3.30– Организация счетчика на Т-триггерах:

а - функциональная схема; б - временная диаграмма

Сумматор

Сумматор - узел ЭВМ, в котором суммируются коды чисел. Как правило, любой сумматор представляет собой комбинацию одноразрядных сумматоров. Сумматоры различают по принципам построения:

Ø накапливающего типа

Ø комбинационного типа.

Сумматоры накапливающего типа строят на сложных JK и/или RS-триггерах, дополняя их выходы достаточно сложными схемами формирования и распространения переносов. Процесс сложения при этом осуществляется поэтапно. Сначала на триггерах сумматора фиксируется код первого операнда, затем на счетные коды разрядов подается код второго операнда. На каждом триггере формируются одноразрядные суммы и значения переносов между разрядами. Учет возникающих переносов задерживает формирование окончательного результата суммы и может требовать дополнительных тактов сложения. Из-за этого многоразрядные схемы сумматора накапливающего типа используются достаточно редко.

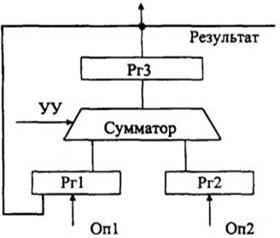

Более часто для построения сумматоров используются сумматоры комбинационного типа. Логика работы такого сумматора была представлена данными таблице 2.2. Обычно у такого сумматора на входе и выходе имеются регистры для хранения и преобразования кодов операндов и результата (рисунок 3.31).

Рисунок 3.31– Упрощенная схема сумматора ЭВМ

Регистр Рг1 предназначается для хранения кода первого операнда, регистр Рг2 - для хранения кода второго операнда. Сумматор по сигналам из устройства управления настраивается на выполнение определенной машинной операции, соответствующей коду операции, находящемуся в коде команды. Результат выполняемой операции фиксируется в регистре РгЗ. При необходимости этот результат может использоваться для продолжения вычислений. Для этого предусматривается возможность перезаписи содержимого регистра РгЗ на Рг1 в качестве значения одного из операндов при выполнении очередной операции.

Арифметико-логическое устройство (АЛУ)

Классическая ЭВМ состоит из трех основных устройств:

ª арифметико-логического устройства,

ª устройства управления

ª запоминающего устройства.

Рассмотрим особенности организации арифметико-логического устройства.

В современных ЭВМ АЛУ не является самостоятельным схемотехническим блоком. Оно входит в состав микропроцессора, на котором строится компьютер. Однако знание структуры и принципов работы АЛУ весьма важно для понимания работы компьютера в целом. Для лучшего понимания этих вопросов проведем синтез арифметического устройства, предназначенного для выполнения только одной операции – умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя. В ходе этого процесса также обратим внимание на особенности использования рассмотренных выше основных схемотехнических элементов ЭВМ.

Синтез АЛУ проходит в несколько этапов. Сначала необходимо выбрать метод, по которому предполагается выполнение операции, и составить алгоритм соответствующих действий. Исходя из алгоритма и формата исходных данных, следует определить набор составляющих АЛУ элементов. Затем требуется определить связи между элементами, установить порядок функционирования устройства и временную диаграмму управляющих сигналов, которые должны быть поданы на АЛУ от устройства управления.

Пусть операнды имеют вид:

[X]пк = x0x1x2…xn

[Y]пк = y0y1y2…yn

где x0, y0 – знаковые разряды.

Операция умножения чисел с фиксированной запятой, заданных в прямом коде, со старших разрядов множителя выполняется по следующей формуле:

Sign Z = Sign X  Sign Y

Sign Y

|Z| = y1•|X|•2-1+ y2•|X|•2-2 +…+yn•|X|•2-n

[X]пк = 0.1101 ; Sign X = 0

[Y]пк = 1.1011 ; Sign Y = 1

Sign Z = 0  1 = 1

1 = 1

|X| = 0. 1 1 0 1

|Y| = 0. 1 0 1 1

y1y2y3y4

+0.00000000 |Z| = 0

y1 = 1 0.01101000 1•|X|•2-1

+0.01101000 |Z| = |Z| + |X|•2-1

y2 = 0 0.00000000 0*|X |•2-2

+0.01101000 |Z| = |Z| + 0

y3 = 1 0.00011010 1•|X|•2-3

+0.10000010 |Z| = |Z| + |X|•2-3

y4 = 1 0.00001101 1•|X|•2-4

0.10001111 |Z| = |Z| + |X|•2-4

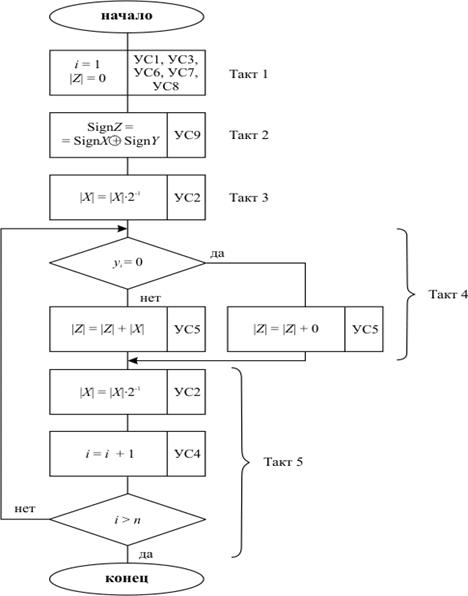

Алгоритм вычислений представлен на рисунке 3.32.

Рисунок 3.32– Алгоритм операции умножения чисел с фиксированной запятой,

заданных в прямом коде, со старших разрядов множителя

Каждой переменной, представленной в алгоритме, в схеме должен соответствовать элемент хранения. Разрядность модуля произведения равна сумме разрядностей сомножителей. Умножение двоичного числа на 2-i обеспечивается сдвигом этого числа вправо на соответствующее количество разрядов. Переход к анализу очередного разряда множителя (i = i + 1) может быть обеспечен сдвигом регистра множителя на один разряд в сторону старших разрядов.

Исходя из этого, определим состав оборудования, необходимого для реализации АЛУ заданного типа для n = 4 ( таблица 3.10).

| Таблица 3.10 – Состав оборудования для АЛУ | |||

| Схема | Разрядность | Функции | Управляющий сигнал |

| Регистр модуля множимого RGX | Загрузка. Сдвиг в сторону младших разрядов. | УС1 УС2 | |

| Регистр модуля множителя RGY | Загрузка. Сдвиг в сторону старших разрядов. | УС3 УС4 | |

| Регистр модуля результата RGZ | Загрузка. Установка в "0". | УС5 УС6 | |

| Триггер знака множимого TX | Загрузка | УС7 | |

| Триггер знака множителя TY | Загрузка | УС8 | |

| Триггер знака результата TZ | Загрузка | УС9 | |

| АЛУ | Комбинационный сумматор | – | |

| Комбинационные схемы | Получение на входе АЛУ сигналов "0" или RGX в зависимости от значения yi | – |

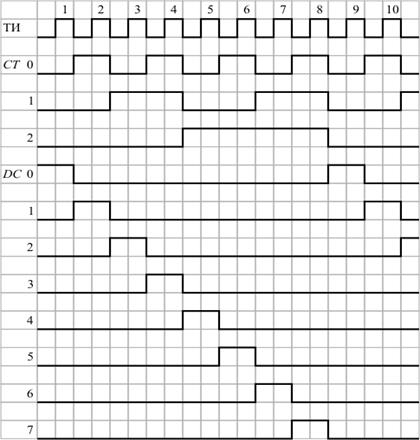

Структурная схема устройства представлена на рисунке 3.33. Временная диаграмма управляющих сигналов, поступающих на арифметико-логическое устройство, показана на рисунке 3.34.

Работа схемы

Такт 1. Загрузка модулей операндов в регистры RGX, RGY, а их знаков – в триггеры TX и TY. Сброс в "0" регистра результата RGZ.

Такт 2. Запись знака результата в триггер TZ.

Такт 3. Сдвиг регистра RGX на один разряд вправо. Через время, равное задержке на переключение регистров и комбинационных схем, на выходе комбинационного сумматора и, следовательно, на входе регистра RGZ устанавливается результат 0+y1• |X|•2-1.

Такт 4. Загрузка RGZ: |Z|=|Z|+y1• |X|•2-1.

Такт 5. Сдвиг RGX на 1 разряд вправо: |X| = |X|•2-1.

Сдвиг RGY на 1 разряд влево: i=i+1.

Устройство управления проверяет условие окончания операции: i > n.

Такты (6,7), (8,9), (10,11) ... Повтор действий тактов (4,5) с анализом других значений yi. В такте 10 в регистре RGZ формируется модуль произведения. Такт 11 используется лишь для определения условия окончания операции умножения.

Рисунок 3.33 – Структурная схема АЛУ для выполнения операции умножения со старших разрядов множителя чисел, заданных в прямом коде

Рисунок 3.34 – Временная диаграмма управляющих сигналов

Устройство управления

Компьютер условно можно разделить на два основных блока:

µ Операционный

µ Управляющий.

Для реализации любой команды необходимо на соответствующие управляющие входы любого устройства компьютера подать определенным образом распределенную во времени последовательность управляющих сигналов. Часть цифрового вычислительного устройства, предназначенная для выработки этой последовательности, называется устройством управления (УУ).

Любое действие, выполняемое в операционном блоке, описывается некоторой микропрограммой и реализуется за один или несколько тактов.

Элементарная функциональная операция, выполняемая за один тактовый интервал и приводимая в действие управляющим сигналом, называется микрооперацией.

Например, в спроектированном АЛУ для умножения чисел в первом такте выполняются следующие микрооперации: TX=0, TY=0, RGX=|X|, RGY=|Y|, RGZ=0.

Совокупность микроопераций, выполняемых в одном такте, называется микрокомандой (МК).

Если все такты должны иметь одну и ту же длину, а именно это имеет место при работе компьютера, то она устанавливается по самой продолжительной микрооперации.

Микрокоманды, предназначенные для выполнения некоторой функционально законченной последовательности действий, образуют микропрограмму.

Например, микропрограмму образует набор микрокоманд для выполнения команды умножения.

Устройство управления предназначено для выработки управляющих сигналов, под воздействием которых происходит преобразование информации в арифметико-логическом устройстве, а также операции по записи и чтению информации в/из запоминающего устройства.

Устройства управления делятся на:

Ø УУ с жесткой, или схемной логикой и

Ø УУ с программируемой логикой (микропрограммные УУ).

В устройствах управления первого типа для каждой команды, задаваемой кодом операции, строится набор комбинационных схем, которые в нужных тактах вырабатывают необходимые управляющие сигналы.

В микропрограммных УУ каждой команде ставится в соответствие совокупность хранимых в специальной памяти слов - микрокоманд. Каждая из микрокоманд содержит информацию о микрооперациях, подлежащих выполнению в данном такте, и указание, какое слово должно быть выбрано из памяти в следующем такте.

Схемное устройство управления

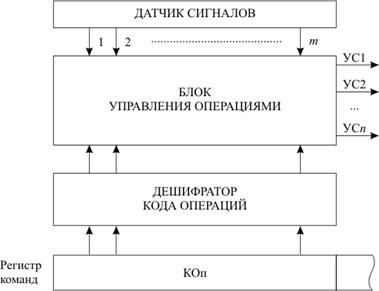

Устройство управления схемного типа (см. рисунок 3.35) состоит из:

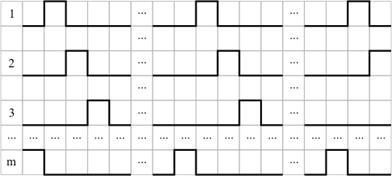

Ø датчика сигналов, вырабатывающего последовательность импульсов, равномерно распределенную во времени по своим шинам (рисунок 3.36) (n - общее количество управляющих сигналов, необходимых для выполнения любой операции; m - количество тактов, за которое выполняется самая длинная операция);

Ø блока управления операциями, осуществляющего выработку управляющих сигналов, то есть коммутацию сигналов, поступающих с ДС, в соответствующем такте на нужную управляющую шину;

Ø дешифратора кода операций, который дешифрирует код операции команды, присутствующей в данный момент в регистре команд, и возбуждает одну шину, соответствующую данной операции; этот сигнал используется блоком управления операциями для выработки нужной последовательности управляющих сигналов.

Рисунок 3.35 – Функциональная схема схемного устройства управления

Рисунок 3.36 – Временная диаграмма работы датчика сигналов

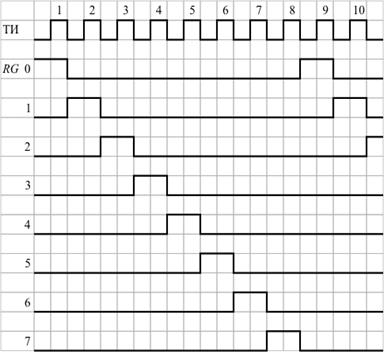

Датчик сигналов обычно реализуется на основе счетчика с дешифратором или на сдвиговом регистре.

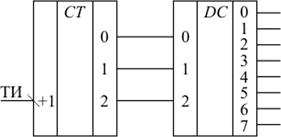

Датчик сигналов на основе счетчика с дешифратором

Реализация датчика сигналов на основе счетчика с дешифратором представлена на рисунке 3.37. По заднему фронту каждого тактового импульса, поступающего на устройство управления с системного генератора импульсов, счетчик увеличивает свое состояние; выходы счетчика соединены со входами дешифратора, выходы которого и являются выходами датчика сигналов рисунке 3.38.

Рисунок 3.37 – Схема датчика сигналов на основе счетчика с дешифратором

Рисунок 3.38 – Временная диаграмма работы датчика сигналов на основе счетчика с дешифратором

Датчик сигналов на сдвиговом регистре

Проектирование датчика сигналов на сдвиговом регистре требует лишь его "закольцовывания", то есть соединения выхода последнего разряда с входом, через который в регистр заносится информация при сдвиге, и первоначальной установки (рисунок 3.39). В начальном состоянии регистр содержит «1» только в разряде 0. Входы параллельной загрузки регистра для его начальной установки и соответствующий этой операции управляющий вход регистра на схеме не показаны.

Рисунок 3.39 – Схема датчика сигналов на основе регистра сдвига

Временная диаграмма работы этой схемы приведена на рисунке 3.40.

Рисунок 3.40 – Временная диаграмма работы датчика сигналов на основе регистра сдвига

Наиболее сложной частью схемного устройства управления является блок управления операциями. Он представляет собой нерегулярную схему, структура которой определяется системой команд и составом оборудования процессора. Такое УУ может быть реализовано в виде специализированной интегральной схемы.

Структурная схема микропрограммного устройства управления

Микропрограммное устройство управления представлено на рисунке 3.41. Преобразователь адреса микрокоманды преобразует код операции команды, присутствующей в данный момент в регистре команд, в начальный адрес микропрограммы, реализующей данную операцию, а также определяет адрес следующей микрокоманды выполняемой микропрограммы по значению адресной части текущей микрокоманды.

Рисунок 3.41 – Функциональная схема микропрограммного устройства управления

(УСi - управляющие сигналы, вырабатываемые устройством управления)

В таблице 3.11 приведен пример микропрограммы для выполнения операции умножения чисел в дополнительном коде. Предполагается, что начальный адрес микропрограммы равен 300, количество разрядов множителя равно 2, а адресная часть микрокоманды содержит адрес микрокоманды, которая должна быть выбрана в следующем такте. В последней микрокоманде в регистр команд загрузится очередная команда, код операции которой определит начальный адрес очередной микропрограммы. В реальных микропрограммных устройствах управления формирование адреса следующей микрокоманды проводится более сложным образом, учитывающим возможности ветвлений и циклического повторения отдельных фрагментов микропрограмм.

| Таблица 3.11 – Микропрограмма выполнения операции умножения | ||||||||

| Адрес МК | УС1 | УС2 | УС3 | УС4 | УС5 | УС6 | Сигнал записи в РК | Адрес следующей МК |

| Х |

Из анализа структуры и принципов работы схемного и микропрограммного устройств управления видно, что УУ первого типа имеют сложную нерегулярную структуру, которая требует специальной разработки для каждой системы команд и должна практически полностью перерабатываться при любых модификациях системы команд. В то же время оно имеет достаточно высокое быстродействие, определяемое быстродействием используемого элементного базиса.

Устройство управления, реализованное по микропрограммному принципу, может легко настраиваться на возможные изменения в операционной части ЭВМ. При этом настройка во многом сводится лишь к замене микропрограммной памяти. Однако УУ этого типа обладают худшими временными показателями по сравнению с устройствами управления на жесткой логике

3.5 Проблемы развития элементной базы

Одним из главных факторов достижения высокого быстродействия, а, значит, и высокой производительности ЭВМ является построение их на новейшей элементной базе. Смена поколений ЭВМ в значительной степени связана с переходами на новые поколения элементной базы, знаменующие достижения новых частотных диапазонов работы схем в рамках доступных технологий. Успехи в создании новой элементной базы определяются передовыми научными и техническими достижениями целого ряда наук (физики, химии, оптики, механики и др.). Качество элементной базы является показателем 'технического прогресса.

Все современные ЭВМ строятся на микропроцессорных наборах, основу которых составляют большие (БИС) и сверхбольшие интегральные схемы (СБИС). Технологический принцип разработки и производства интегральных схем действует уже более четверти века. Он заключается в циклическом послойном изготовлении частей электронных схем по циклу программа - рисунок - схема. По программам на напыленный фоторезисторный слой наносится рисунок будущего слоя микросхемы. Затем рисунок протравливается, фиксируется, закрепляется и изолируется от новых слоев. На основе этого создается пространственная твердотельная структура. Например, СБИС типа Pentium включает около трех с половиной миллионов транзисторов, размещаемых в пятислойной структуре.

Степень микроминиатюризации, размер кристалла ИС, производительность и стоимость технологии напрямую определяются типом литографии. До настоящего времени доминирующей оставалась оптическая литография, т.е. послойные рисунки на фоторезисторе микросхем наносились световым лучом. В настоящее время ведущие компании, производящие микросхемы, реализуют кристаллы с размерами примерно 400мм2 - для процессоров (например, Pentium) и 200мм2 - для схем памяти. Минимальный топологический размер (толщина линий) при этом составляет 0,5 - 0,35 мкм. Для сравнения можно привести такой пример. Толщина человеческого волоса составляет примерно 100 мкм. Значит, при таком разрешении на толщине волоса могут вычерчивать более двухсот линий.

Дальнейшие достижения в микроэлектронике связываются с электронной (лазерной), ионной и рентгеновской литографией. Это позволяет выйти на размеры 0.25, 0.18 и даже 0.08мкм.

При таких высоких технологиях возникает целый ряд проблем. Микроскопическая толщина линий, сравнимая с диаметром молекул, требует высокой чистоты используемых и напыляемых материалов, применения вакуумных установок и снижения рабочих температур. Действительно, достаточно попадания мельчайшей пылинки при изготовлении микросхемы, как она попадает в брак. Поэтому новые заводы по производству микросхем имеют уникальное оборудование, размещаемое в чистых помещениях класса 1, микросхемы в которых транспортируются от оборудования к оборудованию в замкнутых сверхчистых мини-атмосферах класса 1000. Мини-атмосфера создается, например, сверхчистым азотом или другим инертным газом при давлении 10-4 Topp.

Уменьшение линейных размеров микросхем и повышение уровня их интеграции заставляют проектировщиков искать средства борьбы с потребляемой Wn и рассеиваемой Wp мощностью. При сокращении линейных размеров микросхем в 2 раза их объемы изменяются в 8 раз. Пропорционально этим цифрам должны меняться и значения Wn и Wp, в противном случае схемы будут перегреваться и выходить из строя. В настоящее время основой построения всех микросхем была и остается КМОП-технология (комплиментарные схемы, т.е. совместно использующие n- и р-переходы в транзисторах со структурой металл - окисел -полупроводник).

Известно, что W=U*I. Напряжение питания современных микросхем составляет 5 - 3V. Появились схемы с напряжением питания 2,8V, что выходит за рамки принятых стандартов. Дальнейшее понижение напряжения нежелательно, так как всегда в электронных схемах должно быть обеспечено необходимое соотношение сигнал-шум, гарантирующее устойчивую работу ЭВМ.

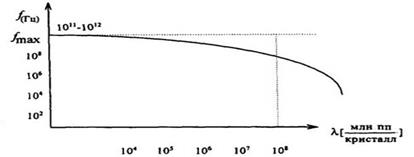

Протекание тока по микроскопическим проводникам сопряжено с выделением большого количества тепла. Поэтому, создавая сверхбольшие интегральные схемы, проектировщики вынуждены снижать тактовую частоту работы микросхем. На рисунке 3.42 показано, что использование максимальных частот работы возможно только в микросхемах малой и средней интеграции. Максимальная частота fmax=1011-1012Гц доступна очень немногим материалам: кремнию Si, арсениду галлия GaAs и некоторым другим. Поэтому они чаще всего и используются в качестве подложек в микросхемах.

Рисунок 3.42 –Зависимость частоты f от степени интеграции l

Таким образом, переход к конструированию ЭВМ на СБИС и ультра-СБИС должен сопровождаться снижением тактовой частоты работы схемы. Дальнейший прогресс в повышении производительности может быть обеспечен либо за счет архитектурных решений, либо за счет новых принципов построения и работы микросхем. Альтернативных путей развития просматривается не очень много. Так как микросхемы СБИС не могут работать с высокой тактовой частотой, то в ЭВМ будущих поколений их целесообразно комплексировать в системы. При этом несколько СБИС должны работать параллельно, а слияние работ в системе должно обеспечивать сверхскоростные ИС (ССИС), которые не могут иметь высокой степени интеграции.

Большие исследования проводятся также в области использования явления сверхпроводимости и туннельного эффекта - эффекта Джозефсона. Работа микросхем при температурах, близких к абсолютному нулю (-273°С), позволяет достигнуть fmax, при этом Wp=Wn=0. Очень интересны результаты по использованию "теплой сверхпроводимости". Оказывается, что для некоторых материалов, в частности для солей бария, явление сверхпроводимости наступает уже при температурах около –1500С. Высказывались соображения, что могут быть получены материалы, имеющие сверхпроводимость при температурах, близких к комнатной. С уверенностью можно сказать, что появление таких элементов знаменовало бы революцию в развитии средств вычислительной техники новых поколений.

В качестве еще одного из альтернативных путей развития элементной базы ЭВМ будущих поколений следует рассматривать и биомолекулярную технологию. В настоящее время имеются опыты по синтезу молекул на основе их стереохимического генетического кода, способных менять ориентацию и реагировать на ток, на свет и т.п. Однако построение из них биологических микромашин еще находится на стадии экспериментов. Таким образом, можно сделать вывод, что в настоящее время возможности микроэлектроники еще не исчерпаны, но давление пределов уже ощутимо. Основой для ЭВМ будущих поколений будут БИС и СБИС совместно с ССИС. При этом структуры ЭВМ и ВС будут широко использовать параллельную работу микропроцессоров.

ГЛАВА 3 ФУНКЦИОНАЛЬНАЯ И СТРУКТУРНАЯ ОРГАНИЗАЦИЯ ЭВМ

4.1. Общие принципы функциональной и структурной организации ЭВМ

Электронные вычислительные машины включают, кроме аппаратурной части и программного обеспечения (ПО), большое количество функциональных средств. К ним относятся коды, с помощью которых обрабатываемая информация представляется в цифровом виде:

µ арифметические коды - для выполнения арифметических преобразований числовой информации;

µ помехозащитные коды, используемые для защиты информации от искажений;

µ коды формы, определяющие, как должна выглядеть обрабатываемая в ЭВМ информация при отображении;

µ цифровые коды аналоговых величин (звука, «живого видео») и др.

Кроме кодов на функционирование ЭВМ оказывают влияние алгоритмы их формирования и обработки, технология выполнения различных процедур (например, начальной загрузки операционной системы, принятой в системе технологии обработки заданий пользователей и др.); способы использования различных устройств и организация их работы (например, организация системы прерываний или организация прямого доступа к памяти), устранение негативных явлений (например, таких, как фрагментация памяти) и др.

Будем считать, что коды, система команд, алгоритмы выполнения машинных операций, технология выполнения различных процедур и взаимодействия аппаратного и программного обеспечений, способы использования устройств при организации их совместной работы, составляющие идеологию функционирования ЭВМ, образуют функциональную организацию ЭВМ.

Реализована идеология функционирования ЭВМ может быть по-разному: аппаратными, программно-аппаратными или программными средствами. При аппаратурной и программно-аппаратной реализации могут быть применены регистры, дешифраторы, сумматоры; блоки жесткого аппаратурного управления или микропрограммного с управлением подпрограммами (комплексами микроопераций); устройства или комплексы устройств, реализованные в виде автономных систем (программируемых или с жестким управлением) и др. При программной реализации могут быть применены различные виды программ - обработчики прерываний, резидентные или загружаемые драйверы, соm-, ехе- или tsr - программы, bat- файлы и др.

Будем считать, что способы реализации функций ЭВМ составляют структурную организацию ЭВМ.

Тогда элементная база, функциональные узлы и устройства ЭВМ, программные модули различных видов (обработчики прерываний, драйверы, соm-, ехе-, tsr-программы, bat-файлы и др.) являются структурными компонентами ЭВМ.

При серьезных конструктивных различиях ЭВМ могут быть совместимыми, т.е. приспособленными к работе с одними и теми же программами (программная совместимость) и получению одних и тех же результатов при обработке одной и той же, однотипно представленной информации (информационная совместимость). Если аппаратная часть электронных вычислительных машин допускает их электрическое соединение для совместной работы и предусматривает обмен одинаковыми последовательностями сигналов, то имеет место и техническая совместимость ЭВМ.

Совместимые ЭВМ должны иметь одинаковую функциональную организацию:

ª информационные элементы (символы) должны одинаково представляться при вводе и выводе из ЭВМ,

ª система команд должна обеспечивать в этих ЭВМ получение одинаковых результатов при одинаковых преобразованиях информации.

Работой таких машин должны управлять одинаковые или функционально совместимые операционные системы (а для этого должны быть совместимы методы и алгоритмы планирования и управления работой аппаратурно-программного вычислительного комплекса). Аппаратные средства должны иметь согласованные питающие напряжения, частотные параметры сигналов, а главное - состав, структуру и последовательность выработки управляющих сигналов.

Дата добавления: 2017-01-13; просмотров: 405;