Основные характеристики ЭВМ 5 страница

Таблица 2.5 – Таблица функций от двух переменных

| Yi | Y0 | Y1 | Y2 | Y3 | ... | Y4 | Y5 | Y6 | Y7 | Y8 | Y9 | ... | Y15 |

| X1 X2 | |||||||||||||

| ... | ... | ||||||||||||

Заметим, что в левой части таблицы перечислены всевозможные комбинации входных переменных (наборы значений), а в правой - возможные реакции выходных сигналов. В таблице 2.5 представлены функции у4-у9, полностью соответствующие функциям таблице 2.4, а также новые, часто используемые и интересные функции у4-у9. При этом местоположение функций и их нумерация в таблице особого значения не имеют. По данной таблице нетрудно составить аналитическое выражение (зависимость) для каждой функции от двух аргументов вида (2.2). Для этого наборы переменных, на которых функция принимает значение единицы, записываются как конъюнкции (логическое умножение) и связываются знаками логического сложения. Такие формы функций получили название дизъюнктивных нормальных форм (ДНФ). Если в этих функциях конъюнкции содержат все без исключения переменные в прямом или инверсном значениях, то такая форма функций называется совершенной.

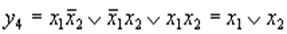

Функция у4 представляет собой функцию логического сложения, дизъюнкцию. Она принимает значение единицы, если значение единицы имеет хотя бы одна переменная х1 или х2:

Тождественность приведенных аналитических зависимостей можно установить, пользуясь законами алгебры логики, приведенными ниже.

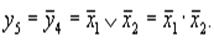

Функция y5 является инверсной функцией по отношению к y4, она имеет название «отрицание дизъюнкции»: ¨

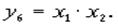

Функция у6 является функцией логического умножения (конъюнкция). Она очень похожа на операцию обычного умножения и принимает значение единицы в тех случаях, когда все ее переменные равны единице:

Функция y7 является инверсной функцией по отношению к у6, она называется «отрицание конъюнкции» или «штрих Шеффера»:

Функция y8 называется логической равнозначностью, она принимает значение единицы, если все ее переменные имеют одинаковое значение (или 0 или 1):

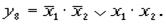

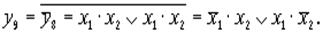

Функция y9 является инверсной по отношению к y8, она принимает значение единицы, если ее переменные имеют противоположные значения:

Ниже будет показано, что функции у8 и у9 являются основой для построения сумматоров, так как они соответствуют правилам формирования цифр двоичных чисел при сложении (вычитании).

Из перечисленных функций двух переменных можно строить сколь угодно сложные зависимости, отражающие алгоритмы преобразования информации, представленной в двоичной системе счисления. Алгебра логики устанавливает правила формирования логически полного базиса простейших функций, из которых могут строиться любые более сложные. Наиболее привычным базисом является набор трех функций {инверсия - Ø , дизъюнкция - \/, конъюнкция - /\ или &}. Работа с функциями, представленными в этом базисе, очень похожа на использование операций обычной алгебры.

Алгебра логики устанавливает, что существуют и другие комбинации простейших логических функций, обладающих свойством логической полноты. Например, наборы логических функций {инверсия, дизъюнкция} и {инверсия, конъюнкция} также являются логически полными. Наиболее интересны минимальные базисы, включающие по одной операции {«отрицание дизъюнкции (Ø \/ )»} и {«отрицание конъюнкции (Ø /\)»}. Однако работа с функциями, представленными в указанных базисах, требует от специалистов по проектированию ЭВМ определенных навыков.

2.4.2. Законы алгебры логики

Из определения вышеприведенных функций можно установить целый ряд простейших свойств:

В алгебру логики установлен целый ряд законов, с помощью которых возможно преобразование логических функций (ЛФ).

| Название закона | Логическое выражение |

| Идемпотентности | x/\x=x x\/x=x |

| Операции с константами | x\/1=1 x/\1=x x\/0=x x\/1=1 |

| Операции с переменной и ее инверсией | x \/ Øx=1 x /\ Øx=0 |

| коммутативный (переместительный) | x1/\x2=x2/\x1

|

| ассоциативный (сочетательный) | (x1/\x2)/\x3=(x1/\x3)/\x2=x1/\(x2/\x3)

|

| дистрибутивный (распределительный) |

|

| Закон поглощения |

|

| Закон склеивания |

|

| Закон свёртки |  где F - логическая функция общего вида, не зависящая от переменной х где F - логическая функция общего вида, не зависящая от переменной х

|

| Правило де Моргана |

|

| Закон двойного отрицания | Ø (Øx)=x |

Убедиться в тождественности приведенных зависимостей можно путем аналитических преобразований выражений или путем построения таблицы истинности для ЛФ, находящихся в левой и правой частях.

Используя данные зависимости, можно преобразовывать исходные выражения в более простые (минимизировать их). По упрощенным выражениям можно построить техническое устройство, имеющее минимальные аппаратурные затраты.

2.4.3. Понятие о минимизации логических функций

Проблема минимизации логических функций решается на основе применения законов склеивания и поглощения с последующим перебором получаемых дизъюнктивных форм и выбором из них оптимальной (минимальной). Существует большое количество методов минимизации ЛФ. Все они отличаются друг от друга спецификой применения операций склеивания и поглощения, а также различными способами сокращения переборов. Среди аналитических методов наиболее известным является метод Квайна-Маккласки, среди табличных - метод с применением диаграмм Вейча и карт Карно. Графические методы минимизации отличаются большей наглядностью и меньшей трудоемкостью. Однако их применение эффективно при малом числе переменных n<5.

Рассмотрим последовательность действий минимизации ЛФ на примере.

Пример 2.15. Найти минимальную дизъюнктивную форму функции, заданной таблицей истинности (таблица 2.6).

Таблица 2.6 – Таблица истинности функции Y = f (X1,X2,X3)

| X1 | Х2 | Х3 | Y | Логическое выражение |

| ||||

| ||||

| ||||

| ||||

| ||||

| ||||

| ||||

|

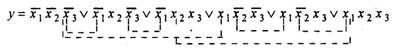

Эта функция интересна тем, что имеет несколько минимальных форм. По данным таблицы запишем аналитическое выражение:

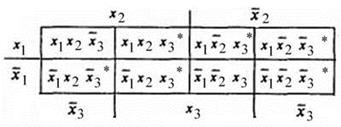

Штриховыми линиями в этом выражении отмечены пары конъюнкций, к которым можно применить операцию склеивания типа  . Особенно это видно при использовании диаграммы Вейча, в которой «склеиваемые» конъюнкции находятся по соседству друг с другом. Диаграмма Вейча просто по-другому интерпретирует таблицу истинности (таблица 2.7).

. Особенно это видно при использовании диаграммы Вейча, в которой «склеиваемые» конъюнкции находятся по соседству друг с другом. Диаграмма Вейча просто по-другому интерпретирует таблицу истинности (таблица 2.7).

Таблица 2.7 - Диаграмма Вейча функции Y

После выделения конъюнкций (они отмечены звездочкой), видно, какие конъюнкции могут образовывать пары для склеивания.

В результате применения операций склеивания и поглощения можно получить другое аналитическое выражение:

в котором отсутствуют возможности дальнейших склеивании и поглощений. Однако последнее выражение является избыточным, так как отдельные конъюнкции могут быть «лишними», т.е. их «составные части» могут включаться в другие конъюнкции. У данной функции существует пять безызбыточных дизъюнктивных форм, из которых только две являются минимальными:

Из приведенных зависимостей видно, что только функции у1 и у4 являются минимальными формами функций, так как они содержат наименьшее число конъюнкций и имеют минимальный ранг этих конъюнкций.

Данный пример показывает, что диаграммы Вейча не дают сразу самый оптимальный вариант для построения ДНФ. Лучше использовать другой табличный метод – метод Карно (карты Карно).

| x1 x2 x3 |  00 00

|  01 01

|  11 11

| |

1 1

|  1 1

|

Рассмотрим алгоритм построения ДНФ. Внутри таблицы (карты) выбираются блоки, содержащие максимальное количество подряд идущих 1 (их количество должно быть степенью 2), таким образом, чтобы покрыть все 1, присутствующее в таблице (при построении блоков допускается их пересечение, но не поглощение).

Замечание: Чем больше размер блока, тем короче логическое выражение.

Внутри блока выражение строится через конъюнкцию, блоки между собой объединяются через дизъюнкцию.

Таким образом, для приведенного примера ДНФ будет иметь вид:

, что совпадает с предыдущим решением.

, что совпадает с предыдущим решением.

Минимизация «вручную» возможна только для функций, зависящих от 4-5 переменных, так как трудоемкость переборов растет в квадратичной зависимости от числа переменных. Применение мощных ЭВМ для этих Целей позволяет расширить границы до п= 12-15. Если при этом учесть, что функции могут быть частично определены (значения функций на некоторых наборах переменных можно определять произвольно), а также что иногда приходится решать задачи совместной минимизации систем ЛФ, то минимизация ЛФ становится сложной инженерной, практической и научной проблемой.

2.4.4. Техническая интерпретация логических функций

Каждой логической операции соответствует свой аппаратный блок (см. п.2.4.1.). На рисунке 2.2. приведены базовые блоки: повторитель, конъюнктор (И-&), дизъюнктор (ИЛИ-1), инвертор (НЕ - Ø), отрицание конъюнкции (И-НЕ), отрицание дизъюнкции (ИЛИ-НЕ).

Каждой логической операции соответствует свой аппаратный блок (см. п.2.4.1.). На рисунке 2.2. приведены базовые блоки: повторитель, конъюнктор (И-&), дизъюнктор (ИЛИ-1), инвертор (НЕ - Ø), отрицание конъюнкции (И-НЕ), отрицание дизъюнкции (ИЛИ-НЕ).

По логическим выражениям проектируются схемы ЭВМ. При этом следует придерживаться следующей последовательности действий.

1. Записать словесное описание работы схемы.

2. Формализовать словесное описание, записав функции в дизъюнктивной (конъюнктивной) совершенной нормальной форме по таблицам истинности.

3. Минимизировать логические зависимости с целью их упрощения.

4. Представить полученные выражения в выбранном логически полном базисе элементарных функций.

5. Построить схему устройства.

6. Проверить работоспособность полученной схемы.

ГЛАВА 2 Классификация элементов и узлов ЭВМ

3.1. Классификация элементов и узлов ЭВМ

При рассмотрении структуры любой ЭВМ обычно проводят ее детализацию. Как правило, в структуре ЭВМ выделяют следующие структурные единицы:

1. устройства,

2. блоки,

3. узлы,

4. элементы.

Такая детализация соответствует вполне определенным операциям преобразования информации, заложенным в программах пользователей.

Нижний уровень обработки реализуютэлементы. Каждый элемент предназначается для обработки единичных электрических сигналов, соответствующих битам информации. Узлы обеспечивают одновременную обработку группы сигналов - информационных слов. Блоки реализуют некоторую последовательность в обработке информационных слов - функционально обособленную часть машинных операций (блок выборки команд, блок записи-чтения и др.). Устройства предназначаются для выполнения отдельных машинных операций и их последовательностей.

В общем случае любая структурная единица ЭВМ обеспечивает преобразование входной информации Х в выходную У (см. рисунок 2.1). Все современные вычислительные машины строятся на комплексах системах интегральных микросхем (ИС).

Электронная микросхема называется интегральной, если ее компоненты и соединения между ними выполнены в едином технологическом цикле, на едином основании и имеют общую герметизацию и защиту от механических воздействий.

Каждая микросхема представляет собой миниатюрную электронную схему, сформированную послойно в кристалле полупроводника: кремния, германия и т.д. В состав микропроцессорных наборов включаются различные типы микросхем, но все они должны иметь единый тип межмодульных связей, основанный на стандартизации параметров сигналов взаимодействия (амплитуда, полярность, длительность импульсов и т.п.). Основу набора обычно составляют большие БИС и даже сверхбольшие интегральные схемы. На очереди следует ожидать появления ультра больших ИС (УБИС). Кроме них обычно используются микросхемы с малой и средней степенью интеграции (СИС). Функционально микросхемы могут соответствовать устройству, узлу или блоку, но каждая из них состоит из комбинации простейших логических элементов, реализующих функции формирования, преобразования, запоминания сигналов и т.д.

Элементы ЭВМ можно классифицировать по различным признакам. Наиболее часто такими признаками являются:

µ тип сигналов,

µ назначение элементов,

µ технология их изготовления и т.д.

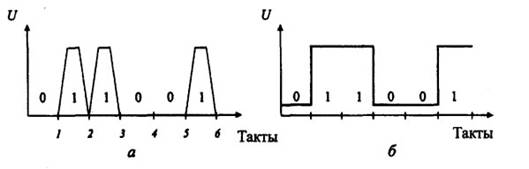

В ЭВМ широко применяют два способа физического представления сигналов: импульсный и потенциальный. При импульсном способе представления сигналов единичному значению некоторой двоичной переменной ставится в соответствие наличие импульса (тока или напряжения), нулевому значению - отсутствие импульса (рисунок 3.1, а). Длительность импульсного сигнала не превышает один такт синхроимпульсов.

При потенциальном или статическом представлении сигналов единично значение двоичной переменной отображается высоким уровнем напряжения, а нулевое значение - низким уровнем (рисунок 3.1, б).

Рисунок 3.1 - Представление информации в ЭВМ:

а - импульсные сигналы; б - потенциальные сигналы

Независимо от вида сигналов различают последовательный и параллельный коды передачи и представления информации в ЭВМ.

При последовательном коде представления данных используются одиночные шины или линии передачи, в которых сигналы, соответствующие отдельным разрядам данных, разнесены во времени. Обработка такой информации производится последовательно разряд за разрядом. Такой вид представления и передачи данных требует весьма экономичных по аппаратурным затратам схем обработки данных. Время же обработки определяется числом обрабатываемых сигналов (разрядов).

Параллельный код отображения и передачи информации предполагает параллельную и одновременную фиксацию всех разрядов данных на различных шинах, т.е. параллельный код данных развернут в пространстве. Это дает возможность ускорить обработку во времени, но затраты на аппаратурные средства при этом возрастают пропорционально числу обрабатываемых разрядов.

Во всех вычислительных машинах используются и параллельно-последовательныекоды представления информации. При этом информация отображается частями. Части поступают на обработку последовательно, а каждая часть данных представляется параллельным кодом.

По своему назначению элементы делятся на формирующие, логические и запоминающие.

К формирующим элементам относятся различные формирователи, усилители, усилители-формирователи и т.п. Данные элементы служат для выработки определенных электрических сигналов, восстановления их параметров (амплитуды, полярности, мощности, длительности).

В каждой ЭВМ имеются специальные блоки, формирующие сигналы тактовой частоты, серии синхронизирующих и управляющих сигналов, координирующих работу всех схем ЭВМ. Длительность такта является важной характеристикой ЭВМ, определяющей ее потенциальную производительность. Время выполнения любой операции ЭВМ связано с определенным числом тактов.

Интервал времени между импульсами основной частоты называется тактом.

Простейшие логические элементы преобразуют входные сигналы в соответствии с элементарными логическими функциями, рассмотренными в п.2.4. В свою очередь, полученные сигналы могут формировать следующий уровень сигналов и т. д. Сложные преобразования в соответствии с требуемыми логическими зависимостями могут приводить к построению многоуровневых схем. Каждая такая схема представляет собой композицию простейших логических схем.

Запоминающим элементом называется элемент, который способен принимать и хранить код двоичной цифры (единицы или нуля).

Элементы памяти могут запоминать и сохранять исходные значения некоторых величин, промежуточные значения обработки и окончательные результаты вычислений. Только запоминающие элементы в схемах ЭВМ позволяют проводить обработку информации с учетом ее развития.

3.2. Комбинационные схемы

Обработка входной информации Х в выходную У (см. рисунок 2.1) в любых схемах ЭВМ обеспечивается преобразователями или цифровыми автоматами двух видов: комбинационными схемами и схемами с памятью.

Комбинационные схемы (КС) – это схемы, у которых выходные сигналы Y = (у1, у2, ..., уm) в любой момент дискретного времени однозначно определяются совокупностью входных сигналов Х = (х1, х2,..., хn), поступающих в тот же момент времени t.

Реализуемый в КС способ обработки информации называется комбинационным потому, что результат обработки зависит только от комбинации входных сигналов и формируется сразу при поступлении входных сигналов. Поэтому одним из достоинств комбинационных схем является их высокое быстродействие. Преобразование информации однозначно описывается логическими функциями вида Y=f(Х).

Логические функции и соответствующие им комбинационные схемы подразделяют на регулярные и нерегулярные структуры. Регулярные структуры предполагают построение схемы таким образом, что каждый из ее выходов строится по аналогии с предыдущими. В нерегулярных структурах такая аналогия отсутствует.

В практике проектирования ЭВМ накоплен огромный опыт по синтезу различных схем. Многие регулярные структуры положены в основу построения отдельных ИС малой и средней степени интеграции или отдельных функциональных частей БИС и СБИС. Из регулярных комбинационных схем наиболее распространены:

Ø дешифраторы,

Ø шифраторы,

Ø схемы сравнения,

Ø комбинационные сумматоры,

Ø коммутаторы и др.

Рассмотрим принципы построения подобных регулярных структур.

Дешифраторы

Дешифраторы (ДШ) - это комбинационные схемы с п входами и m =2n выходами и преобразующая двоичный код на своих входах в унитарный код на выходах.

Унитарным называется двоичный код, содержащий одну и только одну единицу, например 00100000.

Единичный сигнал, формирующийся на одном из т выходов, однозначно соответствует комбинации входных сигналов. Например, разработка структуры ДШ для п=3 согласно методике, изложенной в п.2.4, позволяет получить таблицу истинности (таблица 3.1) и логические зависимости.

Таблица 3.1 - Таблица истинности дешифратора

| Входы | Выходы | |||||||

| X2 | X1 | X0 | Y0 | Y1 | ... | Y5 | Y6 | Y7 |

| … | ||||||||

Условно-графическое обозначение дешифратора на три входа приведено на рисунке 3.1.

Рисунок 3.1– Условно-графическое обозначение трехвходового дешифратора

Рассмотрим логические зависимости при формировании сигнала на одном из его выходов (например, сигнал f5 на выходе 5):  .

.

| Х1Х2 Х0 | ||||

0 0

|  0 0

|  0 0

|  0 0

| |

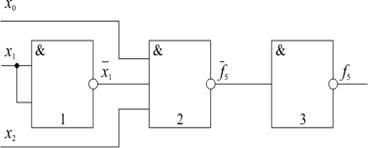

Реализация ДШ в одноэлементном базисе «Штрих Шеффра»  достаточно проста (см. рисунок 3.2).

достаточно проста (см. рисунок 3.2).

Рисунок 3.2 – Схема формирования сигнала на 5 выходе ДШ

Из представленной схемы видно, что фактически логику преобразования выполняет лишь элемент 2, в то время как элемент 1 служит для получения инверсии сигнала x1, а элемент 3 преобразует полученное на элементе 2 инверсное значение функции в прямое. Многие элементы хранения, например триггерные схемы, позволяют получать сигнал в парафазном коде, то есть имеют два выхода, на одном из которых сигнал имеет прямое, а на другом – инверсное значение. Это позволяет избавиться от элемента 1 в схеме. Если предположить, что значения выходных сигналов имеют инверсный вид по отношению к представленному в таблице 3.1, то отпадает необходимость в элементе 3. В большинстве реальных интегральных микросхем реализованы именно дешифраторы с инверсными выходами. Обозначение такого дешифратора показано на рисунке 3.3.

Рисунок 3.3–Условно-графическое обозначение дешифратора с инверсными выходами

На выходах такого дешифратора образуется унитарный код, содержащий один и только один ноль. Например, если входные сигналы имеют значение 1102=610, то выходы дешифратора, представленного на рисунке 3.3, будут находиться в состоянии 10111111, то есть выход 6 будет иметь значение, отличное от остальных выходов.

Дешифраторы широко применяются в различных устройствах компьютеров. Прежде всего, они используются для выбора ячейки запоминающего устройства, к которой производится обращение для записи или считывания информации, для расшифровки кода операции и т.д. При этом часть разрядов адресного кода может дешифрироваться дешифраторами, выполненными в виде отдельных интегральных схем, а другая часть разрядов (обычно младшая) дешифрируется с помощью дешифраторов, встроенных непосредственно в БИС запоминающего устройства. Кроме того, дешифраторы находят применение в устройстве управления для определения выполняемой операции, построения распределителей импульсов и в других блоках.

Дата добавления: 2017-01-13; просмотров: 274;