Байтный режим ввода — Byte Mode

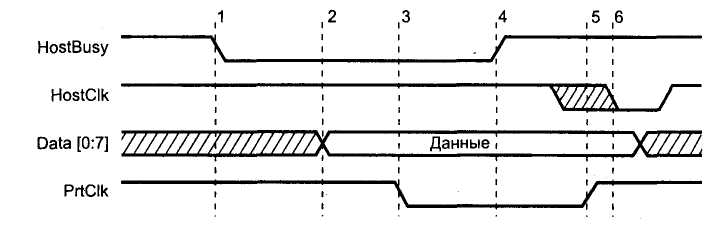

В этом режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита CR. 5=1. Как и предыдущие, режим является программно-управляемым — все сигналы квитирования анализируются и устанавливаются драйвером. , временные диаграммы — на рис. 1.2.

Сигналы действуют в последовательности согласования (см. ниже).

Рис. 1.2. Прием данных в байтном режиме

Фазы приема байта данных перечислены ниже.

1. Хост сигнализирует о готовности приема данных установкой низкого уровня

на линии HostBusy.

2. ПУ в ответ помещает байт данных на линии Data [0:7].

3. ПУ сигнализирует о действительности байта установкой низкого уровня на

линии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость

приемом и обработкой байта.

5. ПУ отвечает установкой высокого уровня на линии PtrClk.

6. Хост подтверждает прием байта импульсом HostClk.

Шаги 1—6 повторяются для каждого следующего байта. После подъема HostBusy ПУ может сигнализировать о наличии данных, занятости Прямого канала и вызывать прерывание по готовности данных. Взаимоблокйрующее квитирование парой сигналов HostBusy и PtrClk хост отрабатывает программно (через CR и SR); ПУ может и не использовать сигнал HostClk (это приглашение к выдаче следующего байта). Достижима скорость как у прямого канала (до 150 кбайт/с). Однако режим может работать только на двунаправленных портах; которые раньше применялись в основном на малораспространенных машинах PS/2, но практически все современные порты можно сконфигурировать на двунаправленный режим (в настройках BIOS Setup — Bi-Di или PS/2).

Режим ЕРР

Протокол ЕРР (Enhanced Parallel Port — улучшенный параллельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия стандарта IEEE 1284. Этот протокол предназначен для повышения производительности обмена по параллельному порту, впервые был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят множеством компаний как дополнительный протокол параллельного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. ниже).

Протокол ЕРР обеспечивает четыре типа циклов обмена:

· запись данных;

· чтение данных;

· запись адреса;

· чтение адреса.

Циклы обмена данными отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение циклов записи и чтения данных очевидно. Выделение адресных циклов позволяет подключать устройство с множеством регистров, организуя мультиплексированную шину адреса и данных. Назначение сигналов порта ЕРР и их связь с сигналами SPP объясняются в табл. 1.4.

' Сигналы действуют в последовательности согласования (см. ниже).

ЕРР-порт имеет расширенный набор регистров (табл. 1.5), который занимаете пространстве ввода-вывода 5-8 смежных байт.

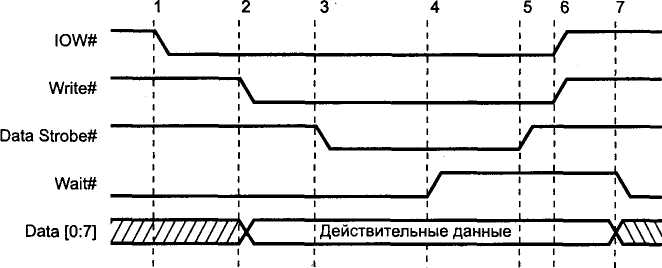

В отличие от программно-управляемых режимов, описанных выше, внешние сигналы ЕРР-порта для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта. На рис. 1.3 приведена диаграмма цикла записи данных, иллюстрирующая внешний цикл обмена, вложенный в цикл записи системной шины процессора (иногда эти циклы называют связанными). Адресный цикл записи отличается от цикла данных только стробом внешнего интерфейса.

Цикл записи данных состоит из следующих фаз.

1. Программа выполняет цикл вывода (IOWR#) в порт 4 (ЕРР Data Port).

2. Адаптер устанавливает сигнал Write* (низкий уровень), и данные помещают

ся на выходную шину LPT-порта.

3. При низком уровне Wait* устанавливается строб данных.

4. Порт ждет подтверждения от ПУ (перевода Wait* в высокий уровень).

5. Снимается строб данных — внешний ЕРР-цикл завершается.

6. Завершается процессорный цикл вывода.

7. ПУ устанавливает низкий уровень Wait*, указывая на возможность начала сле

дующего цикла.

Рис.1.3. Цикл записи данных ЕРР

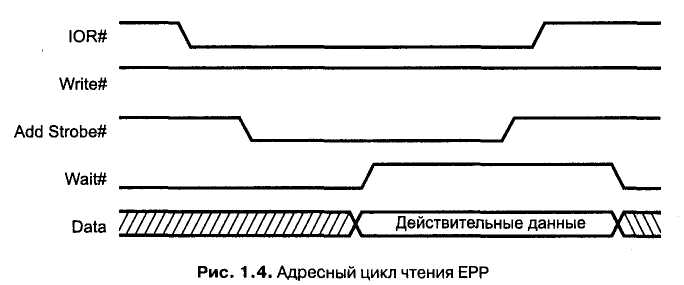

Пример адресного цикла чтения приведен на рис. 1.4. Цикл чтения данных отличается только применением другого стробирующего сигнала.

Главной отличительной чертой ЕРР является выполнение внешней передачи во время одного процессорного цикла ввода-вывода. Это позволяет достигать высоких скоростей обмена (0,5-2 Мбайт/с). ПУ, подключенное к параллельному порту ЕРР, может работать со скоростью устройства, подключаемого через слот ISA.Протокол блокированного квитирования (interlocked handshakes) позволяет автоматически настраиваться на скорость обмена, доступную и хосту, и ПУ. ПУ может регулировать длительность всех фаз обмена с помощью всего лишь одного сигнала Wait#. Протокол автоматически подстраивается под длину кабеля — вносимые задержки приведут только к удлинению цикла. Поскольку кабели, соответствующие стандарту IEEE 1284 (см. выше), имеют одинаковые волновые свойства для разных линий, нарушения передачи, связанного с «состязаниями» сигналов, происходить не должно. При подключении сетевых адаптеров или внешних дисков к ЕРР-порту можно наблюдать непривычное явление: снижение производительности по мере удлинения интерфейсного кабеля.

Естественно, ПУ не должно «подвешивать» процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализаций ЕРР за тайм-аутом интерфейса следит сам адаптер — если ПУ не отвечает в течение определенного времени (5 мкс), цикл прекращается и в дополнительном (не стандартизованном) регистре состояния адаптера фиксируется ошибка.

Устройства с интерфейсом ЕРР, разработанные до принятия IEEE 1284, отличаются началом цикла: строб DataStb# или AddrStb* устанавливается независимо от состояния WAIT*. Это означает, что ПУ не может задержать начало следующего цикла (хотя может растянуть его на требуемое время). Такая спецификация называется ЕРР 1.7 (предложена Xircom). Именно она применялась в контроллере 82360. Периферия, совместимая с IEEE 1284 ЕРР, будет нормально работать с контроллером ЕРР 1.7, но ПУ в стандарте ЕРР 1.7 может отказаться работать с контроллером ЕРР 1284.

С программной точки зрения контроллер ЕРР-порта выглядит просто (см. табл. 1.5). К трем регистрам стандартного порта, имеющим смещение 0,1 и 2 относительно базового адреса порта, добавлены два регистра (ЕРР Address Port иЕРР Data Port), чтение и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для совместимости ЕРР-порта с ПУ и ПО, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппарат-но, при записи в регистр управления CR биты 0, 1 и 3, соответствующие сигналам Strobe*, AutoFeed* и Selectln*, должны иметь нулевые значения. Программное вмешательство могло бы нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты (ЕРР Protect), при включении которых программная модификация этих бит блокируется.

Использование регистра данных ЕРР позволяет осуществлять передачу блока данных с помощью одной инструкции RE P INSB или RE P OUTSB. Некоторые адаптеры допускают 16/32-битное обращение к регистру данных ЕРР. При этом адаптер просто дешифрует адрес со смещением в диапазоне 4-7 как адрес регистра данных ЕРР, но процессору сообщает о разрядности 8 бит. Тогда 16- или 32-битное обращение по адресу регистра данных ЕРР приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Более «продвинутые» адаптеры для адреса регистра данных ЕРР сообщают разрядность 32 бит и для них до 4 байт может быть передано за один цикл обращения процессора. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы ЕРР всегда выполняются только в однобайтном режиме.

Важной чертой ЕРР является то, что обращение процессора к ПУ осуществляется в реальном времени — нет буферизации. Драйвер способен отслеживать состояние и подавать команды в точно известные моменты времени. Циклы чтения и записи могут чередоваться в произвольном порядке или идти блоками. Такой тип обмена удобен для регистро-ориентированных ПУ или ПУ, работающих в реальном времени, например устройств сбора информации и управления. Этот режим пригоден и для устройств хранения данных, сетевых адаптеров, принтеров, сканеров и т. п.

К сожалению, режим ЕРР поддерживается не всеми портами — он отсутствует, к примеру, в ряде блокнотных ПК. Так что при разработке собственных устройств ради большей совместимости с компьютерами приходится ориентироваться на режим ЕСР.

Режим ЕСР

Протокол ЕСР (Extended Capability Port — порт с расширенными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизводительный двунаправленный обмен данными хоста с ПУ.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

? циклы записи и чтения данных;

? командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передача канальных адресов и передача счетчика RLC (Run-Length Count).В отличие от ЕРР вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адаптера, изложенный в документе «The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard» компании Microsoft. Этот документ определяет свойства протокола, не заданные стандартом IEEE 1284:=

? компрессия данных хост-адаптером по методу RLE;

? буферизация FIFO для прямого и обратного каналов;

? применение DMA и программного ввода-вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использовать, только если ее поддерживают и хост, и ПУ.|

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный Драйвер просто адресуется к другому логическому каналу того же порта.

.

1 Сигналы действуют в последовательности согласования (см. ниже).

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

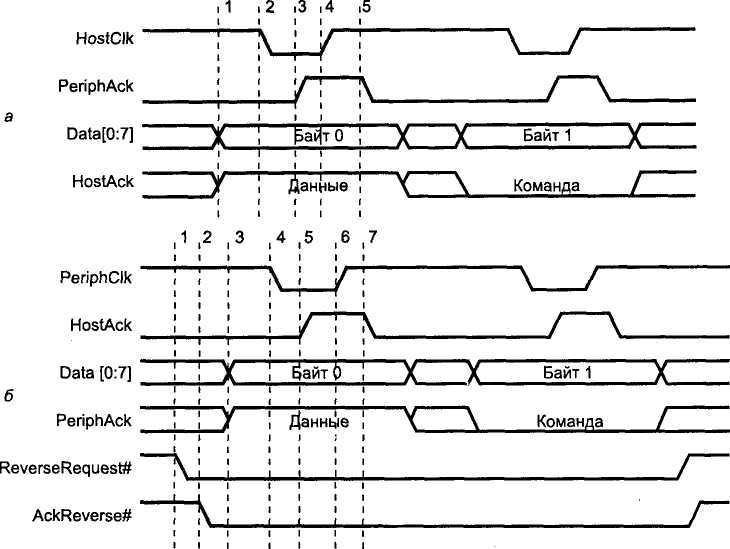

На рис. 1.5, а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цикла задается уровнем на линии HostAck: в цикле данных — высокий, в командном цикле — низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный — то канальный адрес. На рис. 1.5, б показана пара циклов обратной передачи.

В отличие от диаграмм обмена ЕРР, на рис. 1.5 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO-буфер. Обмен драйвера с FIFO-буфером может осуществляться как с использованием DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ЕСР. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но обычно важно только то, завершен он или нет.

Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

1. Хост помещает данные на шину канала и устанавливает признак цикла дан

ных (высокий уровень) или команды (низкий уровень) на линии HostAck.

2. Хост устанавливает низкий уровень на линии HostClk, указывая на действи

тельность данных.

3. ПУ отвечает установкой высокого уровня на линии PeriphAck.

4. Хост устанавливает высокий уровень линии HostClk, и этот перепад может ис

пользоваться для фиксации данных в ПУ.

5. ПУ устанавливает низкий уровень на линии PeriphAck для указания на готов

ность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

Передача в режиме ЕСР: а — прямая, б — обратная

Из рис. 1.5 видно и другое отличие ЕСР от ЕРР. Протокол ЕРР позволяет драйве ру чередовать циклы прямой и обратной передачи, не запрашивая подтвержденю на смену направления. В ЕСР смена направления должна быть согласована: хос запрашивает реверс установкой ReverseRequest*, после чего он должен дождать ся подтверждения сигналом AckReverse#. Поскольку предыдущий цикл мог вы подняться по прямому доступу, драйвер должен дождаться завершения прямой доступа или прервать его, выгрузить буфер FIFO, определив точное значение счет чика переданных байт, и только после этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

1. Хост запрашивает изменение направления канала, устанавливая низкий уро

вень на линии ReverseRequest*.

2. ПУ разрешает смену направления установкой низкого уровня на линии

AckReverse#.

3. ПУ помещает данные на шину канала и устанавливает признак цикла данныч

(высокий уровень) или команды (низкий уровень) на линии PeriphAck.

4. ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действи

тельность данных.

5. Хост отвечает установкой высокого уровня на линии HostAck.

6. ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может ис

пользоваться для фиксации данных хостом.

7. Хост устанавливает низкий уровень на линии HostAck для указания на готов

ность к приему следующего байта.

Дата добавления: 2016-06-13; просмотров: 1133;