Традиционный LPT-порт

Традиционный, он же стандартный, LPT-порт называется стандартным параллельным портом (Standard Parallel Port, SPP), или SPP-портом, и является однонаправленным портом, через который программно реализуется протокол обмена Centronics .

Перечислим шаги процедуры вывода байта по интерфейсу Centronics с указанием требуемого количества шинных операций процессора.

1. Вывод байта в регистр данных (1 цикл IOWR#).

2. Ввод из регистра состояния и проверка готовности устройства (бит SR. 7 —

сигнал Busy). Этот шаг зацикливается до получения готовности или до сраба

тывания программного тайм-аута (минимум 1 цикл IORD#).

3. По получению готовности выводом в регистр управления устанавливается

строб данных, а следующим выводом строб снимается. Обычно, чтобы пере

ключить только один бит (строб), регистр управления предварительно считы-

вается, что к двум циклам IOWR# добавляет еще один цикл IORD#.

Видно, что для вывода одного байта требуется 4-5 операций ввода-вывода с регистрами порта (в лучшем случае, когда готовность обнаружена по первому чтению регистра состояния). Отсюда вытекает главный недостаток вывода через стандартный порт — невысокая скорость обмена при значительной загрузке процессора. Порт удается разогнать до скоростей 100-150 Кбайт/с при полной загрузке процессора, что недостаточно для печати на лазерном принтере. Другой недостаток функциональный — сложность использования в качестве порта ввода.

Стандартный порт асимметричен — при наличии 12 линий (и бит), нормально работающих на вывод, на ввод работает только 5 линий состояния. Если необходима симметричная двунаправленная связь, на всех стандартных портах работоспособен режим полубайтного обмена — Nibble Mode. В этом режиме, называемом также Hewlett Packard Bi-tronics, одновременно принимаются 4 бита данных, пятая линия используется для квитирования. Таким образом, каждый байт передается за два цикла, а каждый цикл требует по крайней мере 5 операций ввода-вывода.Схемотехника выходных буферов данных LPT-портов отличается большим разнообразием. На многих старых моделях адаптеров SPP-порт данных можно использовать и для организации ввода. Если в порт данных записать байт с единицами во всех разрядах, а на выходные линии интерфейса через микросхемы с выходом типа «открытый коллектор» подать какой-либо код (или соединить ключами какие-то линии со схемной землей), то этот код может быть считан из того же регистра данных. Однако выходным цепям передатчика информации придется «бороться» с выходным током логической единицы выходных буферов адаптера. Схемотехника ТТЛ такие решения не запрещает, но если внешнее устройство выполнено на микросхемах КМОП, их мощности может не хватить для «победы» в этом шинном конфликте. Однако современные адаптеры часто имеют в выходной цепи согласующий резистор с сопротивлением до 50 Ом. Выходной ток короткого замыкания выхода на землю обычно не превышает 30 мА. Простой расчет показывает, что даже в случае короткого замыкания контакта разъема на землю при выводе «единицы» на этом резисторе падает напряжение 1,5 В, что входной схемой приемника будет воспринято как «единица». Поэтому нельзя полагать, что такой способ ввода будет работать на всех компьютерах. На некоторых старых адаптерах портов выходной буфер отключается перемычкой на плате. Тогда порт превращается в обыкновенный порт ввода.

Стандарт IEEE 1284

Стандарт на параллельный интерфейс IEEE 1284, принятый в 1994 году, описывает порты SPP, ЕРР и ЕСР. Стандарт определяет 5 режимов обмена данными, метод согласования режима, физический и электрический интерфейсы. Согласно IEEE 1284, возможны следующие режимы обмена данными через параллельный порт:

· Режим совместимости (Compatibility Mode) — однонаправленный прямой 8-

битный канал с протоколом Centronics, программно управляемый хостом. Это

базовый режим порта — исходное состояние и промежуточный при всех пере

ходах.

· Полубайтный режим (Nibble Mode) — однонаправленный обратный парал

лельно-последовательный (4-битный) канал, программно управляемый хос

том. Служит дополнением к Compatibility, одновременно с ним работать не

может, переключение под управлением хоста.

· Байтный режим (Byte Mode) — однонаправленный обратный 8-битный канал,

программно управляемый хостом. Служит дополнением к Compatibility, одно

временно с ним работать не может, переключение под управлением хоста.

· Режим ЕРР (ЕРР Mode) — двунаправленный 8-битный канал, управляемый

процессором; аппаратно реализованное блокирующее квитирование. Отдель

ные линии стробирования позволяют различать передачу данных и адресов,

· Режим ЕСР (ЕСР Mode) — двунаправленный симметричный 8-битный канал,

аппаратно реализованное блокирующее квитирование. Управляющая линия

позволяет различать передачу данных и команд; команды могут быть исполь

зованы для компрессии данных и адресации каналов.

Стандарт определяет способ, по которому ПО может определить режим, доступный и хосту (PC), и периферийному устройству (или присоединенному второму компьютеру). Режимы нестандартных портов, реализующих протокол обмена Centronics аппаратно (Fast Centronics, Parallel Port FIFO Mode), могут и не являться режимами IEEE 1284, несмотря на наличие в них черт ЕРР и ЕСР.

В компьютерах с LPT-портом на системной плате режим — SPP, ЕРР, ЕСР или их комбинация — задается в BIOS Setup. Режим совместимости полностью соответствует SPP-порту. Остальные режимы подробно рассмотрены ниже. При описании режимов обмена фигурируют следующие понятия:

1. хост — компьютер, обладающий параллельным портом;

2. ПУ — периферийное устройство, подключаемое к этому порту;

3. Ptr — в названиях сигналов обозначает Передающее ПУ;

4. прямой канал — канал вывода данных от хоста в ПУ;

5. обратный канал — канал ввода данных в хост из ПУ.

? 1.3.1. Полубайтный режим ввода — Nibble Mode

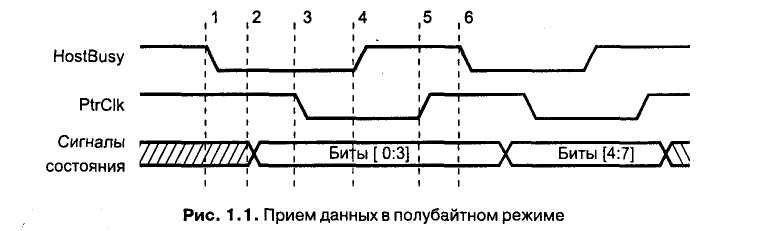

Полубайтный режим предназначен для двунаправленного обмена и может работать на всех стандартных портах. Порты имеют 5 линий ввода состояния, используя которые ПУ может посылать в хост байт тетрадами (nibble — полубайт, 4 бита) за два приема. Сигнал Аск#, вызывающий прерывание, которое может использоваться в данном режиме, соответствует биту 6 регистра состояния, что усложняет программные манипуляции с битами при сборке байта. Сигналы порта приведены в табл. 1.2, временные диаграммы — на рис. 1.1.

Прием байта данных в полубайтном режиме состоит из следующих фаз:

1. Хост сигнализирует о готовности приема данных установкой низкого уровня

на линии HostBusy.

2. ПУ в ответ помещает тетраду на входные линии состояния.

3. ПУ сигнализирует о готовности тетрады установкой низкого уровня на ли

нии PtrClk.

4. Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость

приемом и обработкой тетрады.

5. ПУ отвечает установкой высокого уровня на линии PtrClk.

6. Шаги 1.-5 повторяются для второй тетрады, после чего ПУ может сигнализи

ровать о наличии данных для хоста (Select) и занятости прямого канала

(Busy); вызывать прерывание (АСК).

Дата добавления: 2016-06-13; просмотров: 1307;